Method Article

סיליקון מתכת-תחמוצת-מוליכים למחצה קוונטי נקודות לשאיבת חד אלקטרון

In This Article

Summary

The fabrication process and experimental characterization techniques relevant to single-electron pumps based on silicon metal-oxide-semiconductor quantum dots are discussed.

Abstract

As mass-produced silicon transistors have reached the nano-scale, their behavior and performances are increasingly affected, and often deteriorated, by quantum mechanical effects such as tunneling through single dopants, scattering via interface defects, and discrete trap charge states. However, progress in silicon technology has shown that these phenomena can be harnessed and exploited for a new class of quantum-based electronics. Among others, multi-layer-gated silicon metal-oxide-semiconductor (MOS) technology can be used to control single charge or spin confined in electrostatically-defined quantum dots (QD). These QD-based devices are an excellent platform for quantum computing applications and, recently, it has been demonstrated that they can also be used as single-electron pumps, which are accurate sources of quantized current for metrological purposes. Here, we discuss in detail the fabrication protocol for silicon MOS QDs which is relevant to both quantum computing and quantum metrology applications. Moreover, we describe characterization methods to test the integrity of the devices after fabrication. Finally, we give a brief description of the measurement set-up used for charge pumping experiments and show representative results of electric current quantization.

Introduction

Silicon is the material of choice for most of the modern microelectronics. Its properties, combined with advanced lithographic techniques, have allowed the semiconductor industry to achieve very large-scale integration and deliver billions of transistors per chip. The metal-oxide-semiconductor (MOS) technology1 has been the key of this relentless technological progress2. In brief, it is based on a selectively doped Si substrate which is thermally oxidized to grow a high quality SiO2 gate oxide on which a metal gate electrode is deposited. Recently, it has been shown that the use of a stack of gate oxides could be beneficial3 . While present industry standards have reached minimum feature sizes for gate lengths below 20 nm, it is becoming increasingly evident that, at this level of miniaturization, detrimental quantum mechanical phenomena come into play that may complicate further downscaling4.

Remarkably, silicon is also an excellent host material to exploit the quantum properties of the electron charge and spin5. This has broadened its range of applicability to entirely new fields such as quantum computing6 and quantum electrical metrology7. Among other approaches5, the use of a multi-gate MOS technology8,9 has led to electrostatically-defined quantum dots (QD) whose occupancy can be controlled down to single-electron level10. Unlike the conventional MOS process where just one gate per transistor is needed1, these QDs are defined via a three-layer stack of Al/AlyOx gates which are used to selectively accumulate electrons at the Si/SiO2 interface, as well as provide lateral and vertical confinement11.

Although these devices had been originally developed for quantum computing applications, they have also recently shown promising performances as metrological tools12,13. In the field of quantum electrical metrology, a long-standing goal is the redefinition of the unit ampere in terms of the elementary charge (e) 14. In particular, the emphasis is on the realization of nano-scale charge pumps to clock the transfer of individual electrons timely and accurately. These devices generate macroscopic quantized electric currents, I=nef, where f is the frequency of an external driving oscillator and n is an integer. To date, the best performance has been achieved with a GaAs-based pump by yielding a current in excess of 150 pA with a relative uncertainty of 1.2 parts per million15. Recently, silicon MOS QDs have also stood out for the implementation of highly accurate single-electron pumps thanks to the capability of finely tuning the charge confinement13.

Here, we discuss the protocol used for the fabrication of silicon MOS QDs. Furthermore, the cryogenic set-up used to test the integrity of the devices after fabrication and the one to perform charge pumping experiments are described. Finally, representative measurements of quantized electric current are reported.

Protocol

הערה: פרוטוקול זה מתאר את הנהלים המשמשים לפברק, חבילה ולבדוק משאבות חד-אלקטרון המבוססות על טכנולוגיית MOS QD סיליקון. הצעדים שנדונו בסעיפי משנה 1 ו- 2 מתבצעים בחדר נקי ISO5, בעוד אלה של סעיף 3 מבוצעים במעבדות ISO6. תנאי סביבה ברציפות נשלטים. ערכים נומינליים לטמפרטורה ולחות נקבעים על 20 ± 1 ° C ו -55% ± 5%, בהתאמה.

1. microfabrication

- שדה אוקסיד

- נקה את הרקיק על ידי טבילה בפעולות הבאה: לחרוט פיראניה (10 דקות), מים ללא יונים (DI) (10 דקות), פתרון RCA-2 (מיליליטר מים DI 175, 30 מיליליטר HCl, H 2 O 2 30 מיליליטר ב 100 מעלות צלזיוס במשך 10 דקות), מים ללא יונים (5 דקות), חומצה הידרופלואורית (HF) מדוללת במים 10: 1 (10 שניות), מים DI (10 דקות). השתמש בגדי מגן בעת טיפול HF (כלומר, משקפי מגן, סינר PVC, וכפפות PVC). המשך בצו האמור.

- מניחים את פרוסותבתנור חמצון ב 900 ° C וחמצן בשלבים כדלקמן: O היבש 2 (10 דקות), O הרטוב 2 (40 דקות), O היבש 2 (10 דקות), N 2 (15 דקות).

- מגעים ohmic

- לבצע photolithography ותחמוצת לחרוט.

- להפקיד רובד כמה-ננומטר בעובי של hexamethyldisilazane אמרגן הידבקות (HMDS) על גבי משטח הרקיק כדלקמן: טרום לאפות על פלטה חמה ב 110 מעלות צלזיוס במשך 1 דקות, לשפוך ~ 50 מיליליטר של HMDS בכוס זכוכית, הנח את הכוס והרקיק בתא הוואקום, לפנות ולחכות 2 דקות.

- ספין שכבה 2-4-מיקרומטר בעובי של photoresist בשני מאחור ובצדדים מול הרקיק (3,000-5,000 סל"ד, 25-40 שניות בהתאם לעובי רצוי).

- לחשוף לאור אולטרה הסגול בaligner מסכה (10 mW / 2 סנטימטר ל4-10 שניות על פי להתנגד עובי). הודעה לאפות על פלטה חמה ב 110 מעלות צלזיוס במשך 1 דקות.

- לפתח במשך 1-2 דקות, ולאחר מכן לשטוף במים ללא יונים.

- בצע לחרוט 2 פלזמה O במשך 20 דקות (לחץ = 340 mTorr; כוח התקרית = 50 W; משתקף כוח <1 W).

- תחמוצת לחרוט בפתרון חומצת HF שנאגרו (15: 1, 4-5 דקות, לחרוט 20 ננומטר / דקת ≈ שיעור על 30 מעלות צלזיוס). יש לשטוף במים ללא יונים (5 דקות). מכה יבשה עם N 2.

- הסר photoresist על ידי טבילה באצטון. לשטוף בisopropanol (IPA), ואז מכה יבשה עם N 2.

- מניחים פרוסה בתנור ב 1000 ° C עם מקור זרחן (N 2 זרימה במשך 30-45 דקות בהתאם לצפיפות סימום רצויה).

- הסר שכבת תחמוצת מזוהמת עם חומצת HF מדוללת במים (10: 1, 3-4 דקות, 40 ננומטר / דקת ≈ שיעור לחרוט על 30 מעלות צלזיוס), לשטוף במים ללא יונים (10 דקות).

- חמצן כמו ב1.1.2.

- לבצע photolithography ותחמוצת לחרוט.

- השער אוקסיד

- חזור על שלבים 1.2.1 ו1.2.2.

- מניחים פרוסה בתנור ייעודי ב 800 מעלות צלזיוס וחמצן בשלבים כדלקמן: O היבש 2 (10 דקות), דichloroethylene + O 2 (20 דקות), O היבש 2 (10-30 דקות בהתאם לעובי תחמוצת רצוי), N 2 (15 דקות).

- Metallization מגעים ohmic

- חזור על שלב 1.2.1.

- מניחים פרוסה במאייד אלומת אלקטרונים. להתאדות של אלומיניום 100 ננומטר ב0.2-0.5 ננומטר / sec ו -5 x 10 -6 Torr.

- משרים את פרוסות ב-methyl-2-pyrrolidone N (תמ"א) על פלטה חמה על 80 מעלות צלזיוס במשך שעה 1 להרים את המתכת. השתמש תסיסה קולית במידת צורך. יש לשטוף בIPA למשך 2 דקות. מכה יבשה עם N 2.

- לחשל ביצירת הגז ב 400 מעלות צלזיוס במשך לפחות 15 דקות.

2. Nanofabrication

- ופל חיתוך

- ספין כל להתנגד על גבי פרוסות סיליקון לפעול כציפוי מגן (סוג של פולימר פרמטרים וספינינג אינם רלוונטיים בשלב זה).

- השתמש דייסר טיפ יהלומים כדי לחתוך פרוסות לשבבים בודדים של ~ 10 x 2 מ"מ 2.

- ניקוי

- משרים בתמ"א עבור שעה 1 על פלטה חשמלית על 80 מעלות צלזיוס, ולאחר מכן לשטוף בIPA למשך 2 דקות. מכה יבשה עם N 2.

- בצע לחרוט 2 פלזמה O למשך 5 דקות (כוח תקרית = 50 W; משתקף כוח <1 W).

- ספין נקי עם אצטון וIPA (7,500 סל"ד, 30 שניות)

- דפוסי סמני יישור

- methacrylate polymethyl ספין (PMMA 950K) A4 להתנגד (5,000-7,500 סל"ד, 30 שניות תלוי בעובי רצוי). עובי אופייני עבודה ≈ 150-200 ננומטר. אופה להתנגד על פלטה חמה ב 180 מעלות צלזיוס במשך 90 שניות.

- לבצע יתוגרפיה קורה אלקטרוני. השתמש בתנאים הבאים לכתוב: אנרגיית אלומה = 30 קאב, ≈ נוכחי קרן 30 הרשות הפלסטינית, במינון אזור ≈ 500-650 μC / 2 סנטימטר בהתאם לגודל סמנים ולהתנגד עובי.

- לפתח להתנגד בפתרון של קטון isobutyl התיל וIPA (1: 3) ל40-60 שניות, ולאחר מכן לשטוף בIPA במשך 20 שניות. מכה יבשה עם N 2 אקדח.

- מקוםהשבב במאייד אלומת אלקטרונים. להתאדות 15 ננומטר של Ti ו -65 ננומטר של Pt ב.2-.4 ננומטר / sec ו -5 x 10 -6 Torr.

- הרם את המתכת כמו בשלב 1.4.3.

- שבב נקי כמו בשלבים 2.2.2-2.2.3.

- דפוסי שער

- ספין להתנגד כמו ב2.3.1.

- לבצע יתוגרפיה קורה אלקטרוני. השתמש בתנאים הבאים לכתוב לתכונות ברזולוציה גבוהה: אנרגיית אלומה = 30 קאב, ≈ נוכחי קרן 30 הרשות הפלסטינית, אזור מינון ≈ 500-700 μC / 2 סנטימטר. הוסף תנאים לתכונות ברזולוציה נמוכות: אנרגיית אלומה = 15 קאב, ≈ נוכחי קרן 10 NA, אזור מינון ≈ 400-600 μC / 2 סנטימטר.

- לפתח להתנגד כמו ב2.3.3.

- מניחים את השבב במאייד תרמית. להתאדות אל ב.1-.4 ננומטר / sec ו1-9 x 10 -6 mbar. עובי יעד משתנה בהתאם למספר שכבה, כפי שמוצג באיור 2 (25-35 ננומטר לשכבה 1, 45-65 ננומטר לשכבה 2, 75-90 nמ 'לשכבה 3).

- הרם את המתכת כמו בשלב 1.4.3.

- לבצע חמצון אל על פלטה חמה ב 150 מעלות צלזיוס למשך 5-10 דקות.

- שבב נקי כמו בשלב 2.2.3.

- חזרו על שלבים 2.4.1-2.4.7 פעמיים כדי להבין את ערימת שער 3-שכבה.

אריזת 3. התקן

- שבב קוביות כמו בשלב 2.1

- יש לשטוף את שבבים קטנים יותר וכתוצאה מכך אצטון וIPA למשך 2 דקות.

- דבק חתיכה ללוח מעגלים מודפס (PCB) עם PMMA A5 בודד. חכה 2 דקות לייבוש. לחלופין, כדי לשפר את thermalization, להשתמש אפוקסי כסף.

- טען את PCB על ונדר טריז ולהמשיך בחיווט.

4. בדיקות יושרה התקן

- הר PCB מכיל מכשיר קווי על בדיקה לטבול.

- חוט הקווים החשמליים של המעגלים המודפסים לאלה של הבדיקה לטבול.

- הכנס את הבדיקה לכלי המכיל הליום נוזלי. להתקדם לאט כדי להימנע מב הליום מוגזםשמן פעמי.

- עבור כל שער מכשיר, לחבר את האלקטרודה בטמפרטורת חדר המקבילה של החללית ליחידת מקור-מידה, תוך שמירה על השערים האחרים מקורקעים. הגדר את נוכחי ציות לכמה Na. לטאטא את המתח בין אפס ל 1.5V בצעדים של 0.1 V, למדוד ולתעד הנוכחי.

- חבר כל שורת שער למקור מתח DC משתנה המופעל באמצעות סוללות, קו המקור למובנה במקור AC מתח של מגבר נעילה ב, וקו הניקוז ליציאת הקלט של הנעילה ב מגבר.

- מדוד את המקור לניקוז מוליכות לתצורות מתח שער שונים (ראה איור 4).

- בעולם כבש את המתח להחיל BL שערים, BR, PL, SL וDL, על ידי שמירה על שערי C1 ו- C2 מקורקעים. רשום את מאפייני 'Turn-על' המכשיר.

- בנפרד כבש את כל מתח שער ולתעד את המאפיינים 'קמצוץ פעמי' השערים.

- התאם את מתח השער להגדיר qu אלקטרוסטטינקודת antum ידי הגדרת המתחים על BL וBR (PL, SL וDL) קטן יותר (יותר) מאשר התור-על מתחים. רשום את מאפייני מצור קולון.

תוצאות

ייצור מכשיר

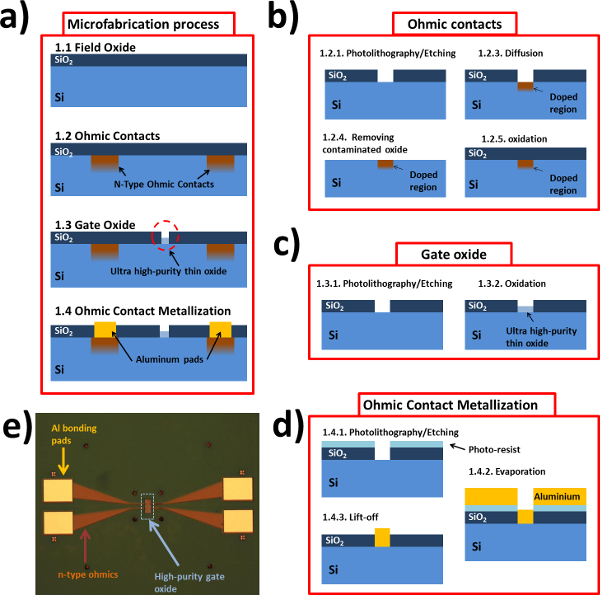

התהליך הראשוני microfabrication (סעיף 1 לפרוטוקול) מתבצע על פרוסות סיליקון מסחריות 4 אינץ 'טוהר גבוה (10 סנטימטרים 12 -3 ≈ ריכוז סימום מסוג n; התנגדות> 10 kΩcm; עובי = 310-340 מיקרומטר ). המטרה היא לממש את המצע שעליו אלקטרודות השער תופקדנה. מצע זה עשוי מאזור פנימי כתרים עם תחמוצת שדה (שלב 1.1), n + אזור כתרים עם תחמוצת שדה (שלב 1.2), אזור פנימי כתרים עם תחמוצת איכות גבוהה שער (שלב 1.3), ומתכת n + אזור ל אנשי קשר ohmic (שלב 1.4). דמויות 1A-D להמחיש את השלבים העיקריים של תהליך microfabrication. איור 1E מראה תמונה מיקרוסקופית של שדה מצע לאחר microfabrication. גודל תכונת המינימום ליתוגרפיה בשלב זה הוא כ 4 מיקרומטר.

SiOיש 2 שכבת תחמוצת גדלה בשלב 1.1 עובי נומינלי של 100 ננומטר ומשמשת כשכבת פסיבציה. אזורים מסוג n הפועלים כמנצחי ohmic מתקבלים באמצעות דיפוזיה זרחן. צפיפות סימום היעד היא כ 19 אוקטובר - 20 אוקטובר סנטימטר -3. יש באיכות גבוהה SiO 2 שהוא גדל באופן סלקטיבי כדי לשמש כדיאלקטרי שער עובי נומינלי של 5 ננומטר. צפיפות פגם ממשק היעד היא <10 10 eV -1 סנטימטר -2 באמצע פער. קיר תנור משולש ייעודי ונבנה בכוונה משמש לתהליך זה. מערכת זו נועדה למזער זיהום מיונים של מתכות כבדות ויונים אלקלי ניידים, כמו גם למנוע לחות מלשדר לתוך תא החמצון. על מנת ליצור את מגעים החשמליים, כריות אלומיניום מופקדות באמצעות אידוי קרן אלקטרונים בחלק מהאזורים מסוג n.

תהליך nanofabrication (ראה סעיף 2) מתבצע על substr השבבאטס מתקבל על ידי חיתוך רקיק מעובד בשלב 1. המטרה הוא להבין את האלקטרודות השער בקנה מידה ננו משמשת להגדרה אלקטרוסטטי QDs MOS. כל ריצת nanofabrication בדרך כלל מייצרת 10-15 דגימות מכשיר שלמות. מיקרוסקופ אלקטרונים סורק הדמיה (SEM) של 1-2 מכשירים ליצוו מתבצע בדרך כלל כדי לאשר ששלבי יתוגרפיה EBL היו מוצלחים. מאז ההדמיה SEM עשויה להזריק חיובים במצע או בשערי המתכת ולגרום לדליפות, רק מספר קטן של מכשירים נבדק בדרך זו, ואילו השאר נבדק חשמלי. גודל תכונת מינימום ליתוגרפיה בשלב זה הוא כ -35 ננומטר. כדי להשיג אחידות טובה של הסרטים אל שהופקדו, המתכת התאדתה בשיעורים איטיים כמו כמה אנגסטרום / שני, בעוד שהמצע הוא רכוב על במה מסתובבת. זה יישאר ב RT, וגודל גרגר אל מוערך של כ -20 ננומטר. איור 2 א ממחיש את השלבים העיקריים של nanofabricatioתהליך n. איור 2 מציג תמונת SEM עם שההגדרה הנכונה של האלקטרודות השער מאומתת. באופן כללי, אחד מטרתה לממש אותם שערים שישירות להגדיר QD (BL, BR וPL) עם גודל התכונה הקטן ביותר האפשרי. לעומת זאת, אלה שערים משמשים להגדרת מאגרי האלקטרונים (DL וSL) יכולים להיות ממדים גדולים יותר, כדי למנוע את discretization לא מכוון של רמות אנרגיה במוביל. סמני Ti / Pt בקנה מידה ננו הבינו בשלב 2.3 משמשים כהתייחסות ליישור של שלוש השכבות של שערים עקביים. הפלטינה נבחרה לניגודו המצוין ביחס למשטח SiO 2 בקורה האלקטרוני. טיטניום משמש כדי לשפר את ההידבקות.

בכל שלבי תהליך הייצור, פינצטה סיבי פחמן-קצה המשמשות לטיפול בשבבים, על מנת להקטין את הסיכוי של שחרור ההרסני אלקטרוסטטית (ESD).

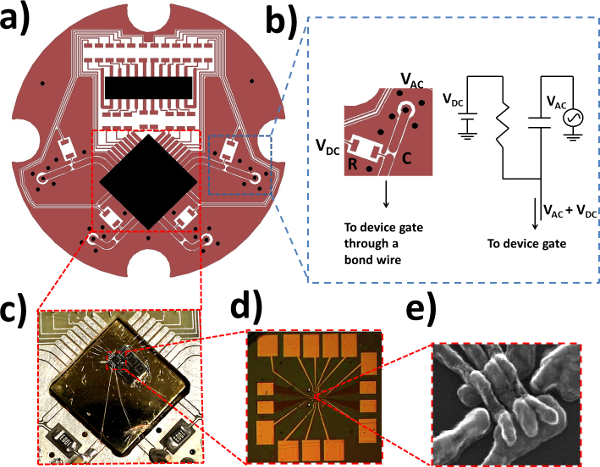

לבסוף, על מנת לבצע מדידות חשמליות בindiviמכשירים כפולים, כל שבב צריך להיות ביקעו בחתיכות קטנות של כ 2 x 2 מ"מ 2 (סעיף קטן 3). כל תכשיט הוא אז דבוק למעגלים מודפסים מותאמים אישית (דיאלקטרי הפסד נמוך רוג'רס R03010) שפינים מחוברים לאלקטרודות המכשיר באמצעות חוטי אל. המליטה חוט מתבצעת עם מכונת ונדר טריז ללא חימום השבבים. הבחירה של הפרמטרים המליטה המתאימים מבוססת על שני שיקולים. מצד אחד, קשר החוט צריך לנקב את שכבת X תרמית אל O y וליצור קשר טוב מתכת אל מתכת עם כרית השער. מצד השני, לחץ מכאני מוגזם עלול לגרום לאירוע אגרוף-שוקת נזקי תחמוצת השדה מתחת לדליפות מצע השער וסיבה ש. במהלך תהליך החיווט, השימוש בצמיד אנטי-סטטית רצוי למנוע ESD. באיור 3, שבב עם 6 מכשירים בודדים מודבק על גבי PCB.

בדיקות תקינות מכשיר

Beforדואר טעינת מכשיר לפלטפורמת מדידת טמפרטורת ח"כ כגון מקרר דילול, בדיקות חשמליות ראשוניות מבוצעים על 4.2 K כדי לבדוק את התקינות של המדגם (ראה סעיף 4 לפרוטוקול). לשם כך, PCB מוכנס לתוך מתחם נחושת ללא חמצן והוא רכוב על גבי חללית לטבול, אשר שקוע בסופו של דבר הוא הנוזל.

הבדיקה הראשונית היא בדרך כלל בדיקת דליפה שמבוצעת ברצף על כל שער. יחידת מקור-מידה מחוברת לאלקטרודה שער בודדת בזמן שאחרים מקורקעים. מתח ramped עד 1.5 V והזרם נמדד במקור. בטווח המתח הזה, שער פועל כראוי לא אמור לנהל, כי שכבת SiO 2 מבודדת את המתכת מן המצע סיליקון וx O y אל מבודד שערים חופפים. בדרך כלל, פירוק תחמוצת ידוע להתרחש למתחים גדולים יותר ~ 4 V, בהתאם לגיאומטרית מכשיר וthic תחמוצתkness. לכן, אם נוכחי מזוהה במהלך הבדיקה, סביר להניח שלפחות אחד משכבות תחמוצת פגומה והמכשיר צריך להיות מושלך. בדרך כלל, פחות מ -10% מהשערים להראות דליפות. התשואה ידועה להיות מושפע ההארכה מישוריים של אלקטרודות השער. בפרט, גדולה יותר החפיפה של השערים עם אזור תחמוצת השער סביר יותר שזה יהיה לי דליפות שער למצע. באופן דומה, גדולה יותר החפיפה בין שערים משכבות שונות יותר את המופע של דליפות שער לשער תהיה. התשואה המצוטטת היא רלוונטית לשערים שלכבוש שטח של כ -50 מיקרומטר 2 על תחמוצת דקה ועם interlayer החופף של כ 0.5 מיקרומטר 2.

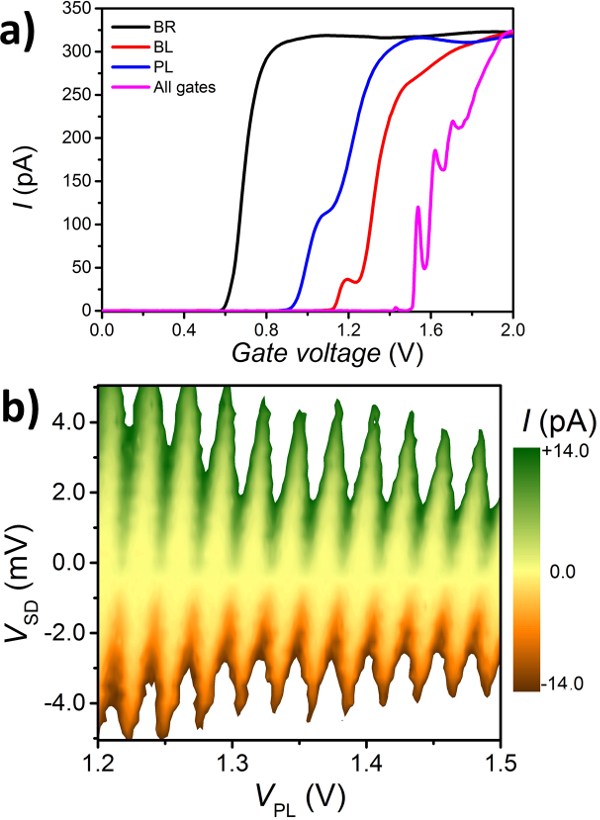

ברגע שהמכשיר עבר את מבחן הדליפה הראשוני, אנשי הקשר ומקור הניקוז מחוברים לנעילה במגבר ואת השערים למדף סוללה לשליטה במתח מודולרי. בתצורה זו, המכשיר מופעל on על ידי גלובלי ramping את כל מתחי השער בו-זמנית. בשלב הבא, כל מתח שער בנפרד ramped מטה, תוך שמירה על אחרים במתח גבוה כדי לאמת את היכולת של שערים בודדים לצבוט את הזרם. איור 4 א מציג עקבות נציג של מדידות אלה. היעדר או מסלול הולכה מקור-ניקוז או שער קמצוץ פעמי פרט הוא לעתים קרובות אינדיקציה של איזה סוג של נזק שער כגון פיצוץ שער או רציפה מתכת.

לבסוף, המקור הנוכחי הבריחה נמדד כפונקציה של הטיה המקור-ניקוז ומתח שער הבוכנה להתבונן החתימה של מצור קולון 16 (ראה איור 4).

מדידות

ברגע שמכשיר מתאים כבר נמצא, הוא מוסר מהספינה הוא נוזלי, ומיובש עם אקדח אוויר חם כדי למנוע היווצרות של לחות שעלולה לגרום לESD. לבסוף, הוא הועבר למקרר דילול.

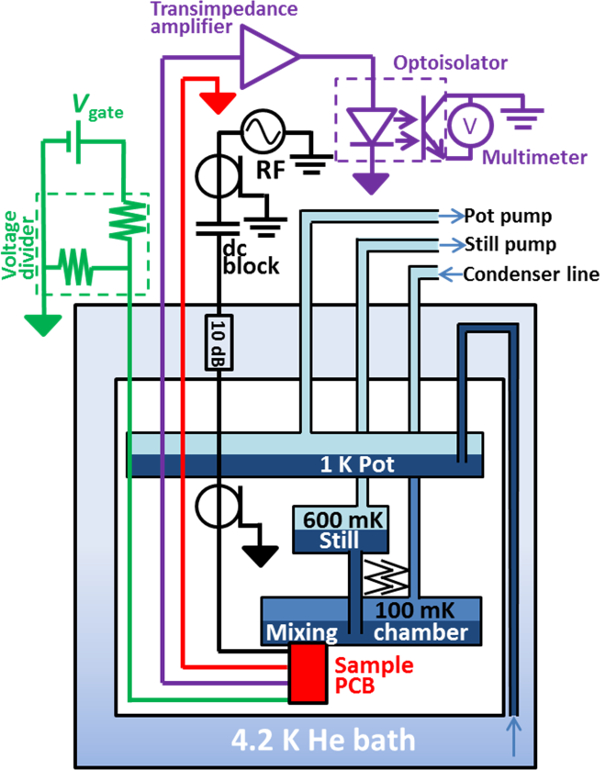

הניסויים מבוצעים במקרר דילול פלסטיק מתוצרת עצמי עם טמפרטורת בסיס של כ -100 ח"כ. Cryostat הוא בתא ואקום השקוע באמבט 4.2 K הליום. הקווים החשמליים thermalized בסיר K 1 אשר גם הוא מועסק להתעבות אדי 3He הנכנסים. בתא הערבוב, ההעברה אנדותרמית של אטומים 3He מהשלב 3He העשיר לשלב 3He-לדלל מאפשרת למערכת להגיע לטמפרטורת בסיס של כ -100 ח"כ.

כפי שניתן לראות בתרשים 5, המקרר מצויד עם 20 קווי DC ו -3 קווי RF משמשים לחיבור האלקטרוניקה בטמפרטורת חדר למכשיר בטמפרטורה נמוכה. חמשת קווי DC הם כבלי Thermocoax ושזורים חוטי 15 נול זוג. קווים אלה להתחבר אלקטרודות השער של המדגם למקורות מתח DC-מופעל על סוללה. מחיצות מתח בRT משמשות להפחתת רעש חשמלי על שערים בודדים. קווי RF הם כבלים קואקסיאליים semirigid ש נחלש ב -10 dB ב 4 K כדי להפחית את הרעש תרמי וdc החסום ב RT. קווים אלה מחוברים לגלבו coplanar של טיז ההטיה על PCB.

מגבר transimpedance רעש נמוך ומודד דיגיטלי משמשים למדידה הנוכחית שנוצר על ידי המשאבה. האלקטרוניקה מחוברת למכשיר באמצעות מבדדים אופטיים המופעלת באמצעות סוללות כדי למנוע היווצרות של לולאות קרקע. אותות RF הכונן מיוצרים על ידי גנרטור צורת גל שרירותי ההארקה שהוא מבודד מאחד cryostat באמצעות רכיב בלוק DC (ראה איור 5).

PCB מכיל 16 קווי DC טהורים ו -4 קווי טי הטיה נהגו לשלב מתח DC ו- AC בטמפרטורה נמוכה. כפי שניתן לראות באיור 3, רכיבים בדידים RC משמשים כדי להבין את קשר טי (R = 100 ק"ג-אוהם, C = 10 NF), ו- 50 Ω התאמה גלבו coplanar המשולב המשמשים להפצת של אותות בתדר גבוה.

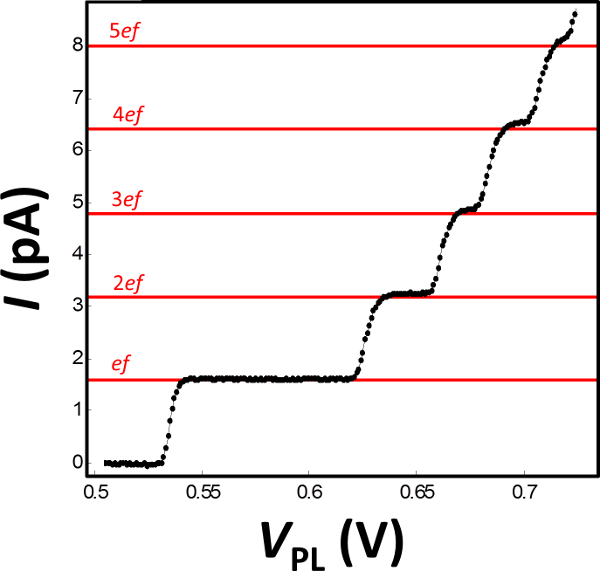

e_content "> ברגע שהמכשיר הוא בטמפרטורת ח"כ, מתחי השער מותאמים כך שתפוסת יחיד אלקטרון בQD מושגת. בפרט, מחסומי מנהרה נוצרים תחת השערים BL וBR, ושכבת הצטברות אלקטרונים מושרה בשערים PL, SL וDL. לשם כך, מתחי שער המחסום נקבעים מתחת התור-על שלהם ערכים, ואילו שערי ההצטברות מקוטבים ב'גדול מ-תור-במתח. בדרך זו QD נוצר תחת שער PL וההארכה מישוריים נשלטת באמצעות שערי C1 ו- C2 שמתח נשמרים מתחת התור-על שלהם ערכים לגרום לכליאה אלקטרוסטטי. בשלב הבא, אותות RF מופעלים לווסת את השקיפות של מחסום המנהרות (ים) מעת לעת, ואלקטרוכימיים הפוטנציאל של הנקודה. שאיבה חד אלקטרון מושגת עם מתחי נהיגה סינוסי אחד או שתיים. במקרה של כונן אחד-אות, אות הנהיגה מוחל BL השער לווסת את הפוטנציאל של מחסום המנהרות ביד השמאל -side שלQD. במקרה של כונן שני אותות, עירורי AC מוחלים על BL שערים וPL לווסת את הפוטנציאלים של שני המחסום עזב וQD באותה התדירות אבל עם שלבים ואמפליטודות שונים. מעלות נוספות אלה של חופש תאפשר אחד כדי לשלוט על הכיוון של העברת אלקטרון 13. תהליך חוזר ונשנה שנדרש בדרך כלל לכוון את הפרמטרים של הניסוי העיקרי (כלומר, אמפליטודות אות כונן RF / שלבים ומתחי שער DC) ולהשיג קוונטיזציה הנוכחית אופטימלית. שים לב שאף אחד משני פרוטוקולי השאיבה צריך הטיה ניקוז-מקור לבצע העברות תשלום. לפיכך, אלקטרודות המקור וניקוז מקורקעות במהלך מבצע המשאבה. איור 6 מציגה את מישורי הרמה הנוכחיות האופייניות במכפילים שלמים של EF מתקבלים על ידי הפעלת כונן סינוסי שתי אות למחסום הקלט (BL) ואת בוכנת השער (PL). נתונים אלה נלקחו בתדירות נמוכה יחסית נהיגה (10 מגה-הרץ) שלא uning של הפרמטרים יכול להתבצע במהירות. בפועל, רצוי לפעול משאבה בכמה מאות מגה-הרץ, בדרך כלל דורש הרבה אופטימיזציה פרמטר עדינה 13.

איור 1. microfabrication. () איור סכמטי של שלבים עיקריים בmicrofabrication. קריקטורות לא נמשכים סולם. מימוש (ב) לאזור מסומם לאנשי קשר ohmic. מימוש של תחמוצת שער (C). Metallization (D) של אנשי קשר ohmic. (ה) מיקרוסקופי תמונה של שדה בודד על שבב לאחר תהליך microfabrication הושלמה. גודל שדה הוא 1.2 x 1.2 מ"מ 2. לחץ כאן כדי לצפות בגרסה גדולה יותר של דמות זו.

איור Nanofabrication () תהליך 2.. ייצור לשכבות שער בודדים. קריקטורות לא נמשכים סולם. ננו-מבנה השער 3-השכבה המשמש לניסויי שאיבת תשלום (B). משמאל: תמונת SEM של מכשיר דומה לזה המשמש למדידות. מימין:. נוף החתך סכמטי של המכשיר על פני חתך-X ולחתוך Y אנא לחץ כאן כדי לצפות בגרסה גדולה יותר של דמות זו.

איור 3. חיבורי חשמל למדגם. פריסה (א) ללוח המעגל המודפס. (ב) הגדלה של אזור של PCB עם הטיה-טי (משמאל)מעגל שווה ערך ד (מימין). (ג) שבב עם 6 שדות בודדים מודבקים על בעל השבב וחוטי קשר לחיבור חשמל למעגלים המודפס. תמונה מיקרוסקופית של שדה בודד לאחר nanofabrication (ד '). תמונה (E) SEM של פריסת השער במרכז אזור תחמוצת שער. אנא לחץ כאן כדי לצפות בגרסה גדולה יותר של דמות זו.

איור 4. בדיקות ראשוניות. () נוכחי AC מקור-ניקוז (שורש ממוצע ריבועים) כפונקציה של מתח שער שונה. עקבות נמדדות עם מגבר נעילה בעם עירור RMS 50 μV ב113.17 הרץ. למתח שער בודד עקבות מתחי השער הנותרים קבועים על 2.0 V, למעט V C1 = V C2 = 0.0 V. מפת הצבע (B) של זרם המקור-ניקוז כפונקציה של מתח שער בוכנה וSL ההטיה מתח. V-מקור ניקוז = 1.5 V, V DL = 1.15 V, V BL = 0.78 V, V BR = 0.85 V, V C1 = V = C2 0.0 V. לחץ כאן כדי לצפות בגרסה גדולה יותר של דמות זו.

קווי איור 5. סכמטי של מדידת הגדרה. העשרים DC (ירוק) ושלושה קווי RF קואקסיאלי (שחור) לחבר את האלקטרוניקה RT ל- PCB. הניקוז של המשאבה (הסגולה) מחובר למגבר transimpedance ולמודד דיגיטלי באמצעות optoisolator, תוך מגע המקור (אדום) מעוגן. חיבורי קרקע נפרדים (indicated עם סמלים שונים) המשמשים למכשור האלקטרוני וקווי חשמל cryostat. אנא לחץ כאן כדי לצפות בגרסה גדולה יותר של דמות זו.

6. קוונטיזציה הספרה נוכחית. אובה נוכחי כפונקציה של V PL עבור כונן סינוסי שני אותות בMHz f = 10 יחולו על BL שערים וPL. הבדל שלב = 49 מעלות, V RF PL = V RF BL = 0.31 V עמ '. המיקום האידיאלי של מישורי רמת השאיבה במכפילים שלמים של EF מוצג כקווים אופקיים אדומים. אנא לחץ כאן כדי לצפות בגרסה גדולה יותר של דמות זו.

Discussion

הפרוטוקול דיווח במאמר זה מתאר את הטכניקות לפברק סיליקון MOS QDs, כמו גם הליכי הניסוי כדי לבדוק את השלמות הפונקציונלית שלהם ולהפעיל אותם כמשאבות חד-אלקטרון. למרבה הפלא, על ידי התאמת עיצוב השער, יכול להיות מועסק באותו תהליך הייצור כדי לייצר מכשירים המתאימים לקריאת נתוני ביט קוונטים ושליטה 17, כמו גם תשלום שאיבת 12,13. נציין כי רב של הפרמטרים התהליך שצוטטו במאמר זה עשוי להשתנות בהתאם לכלי הייצור משמשים (כיול, לעשות או מודל), כמו גם בסוג של מצע סיליקון (עובי וצפיפות סימום רקע). כמויות כגון מינון חשיפה ליתוגרפיה או זמן פיתוח, תחריט או משך חמצון, צריכה להיות מכוילות בקפידה ונבדקו כדי להבטיח תשואה אמינה. יתר על כן, חשוב להימנע מזיהום צולב הנובע מהשימוש באותם הכלים ייצור לתהליכים שונים. לשם כך, מספר CRצעדי itical מתבצעים עם ציוד מוקדש אך ורק לעיבוד סיליקון כגון דודי מתכת, תנורי חמצן ואמבטיות HF.

באופן כללי יותר, סיליקון הוא ציור התעניינות גוברת בחומר של בחירה לממש משאבות תשלום 18-20. זה נובע בחלקו הפרספקטיבה האטרקטיבי של יישום סטנדרטי זרם חשמלי מבוסס קוונטים חדשים באמצעות תהליך סיליקון תעשייה תואמת. זה היה ליהנות מטכניקות אינטגרציה מבוססות ואמינות ליכולת רחבה, במקביל ומעל הנהיגה. חשוב לציין, טכנולוגית MOS המשלים (CMOS) מלאה, ללא מסורתי מתכת כחומר השער, הראתה תנודות תשלום רקע מופחתות במידה ניכרת במכשירים חד-אלקטרון 21. תנודות מסוג זה יכול להיות מזיקות בהשגת דיוקים המטרולוגי.

הפרוטוקול שנדון כאן מוגבל למימוש של ננו-התקני MOS עם שערי מתכת. לכן, כדי achieיש תאימות תעשייתית מלאה ולהפחית תנודות תשלום, זה יהיה צורך לשנות את הטכניקות בתצהיר שער ולהשתמש בסיליקון גבישי מסוממים מאוד כחומר השער.

לסיכום, משאבות MOS QD שנדונו כאן לאחרונה בשילוב היתרון הטכנולוגי של סיליקון עם ביצועים טובים מאוד במונחים של דור הנוכחי מדויק 13. זה נובע מהגמישות הגבוהה של תהליך התכנון וייצור המאפשר אחד למחסנית שכבות מרובות שער מוביל למערכת קומפקטית ורבות-תכליתית. Tunability קנס התוצאה של הכליאה אלקטרוסטטי של הנקודה יחד עם הפוטנציאל להפחתת תנודות תשלום רקע מגדיר את הבמה כדי להתגבר על האתגרים העיקריים שנצפו במוליכים למחצה אחרים משאבות 22,23.

Disclosures

יש המחברים אין לחשוף.

Acknowledgements

אנו מודים KY טאן, פ לראות וGC Tettamanzi לדיונים מועילים. אנו מכירים תמיכה כספית מהמועצה האוסטרלית למחקר (מענק מס 'DP120104710), האקדמיה של פינלנד (מענק מס' 251,748, 135,794, 272,806) ותמיכה ממתקן ייצור הלאומי של אוסטרליה לייצור מכשיר. AR מודה תמיכה כספית מתכנית גרנט חוקר מאוניברסיטת ניו סאות 'ויילס בתחילת הקריירה. מתן שירותים נוספים ותמיכה טכנית על ידי אוניברסיטת אלטו בMicronova מרכז Nanofabrication הוא גם הודה.

Materials

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

References

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930(2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).

Reprints and Permissions

Request permission to reuse the text or figures of this JoVE article

Request PermissionExplore More Articles

This article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. All rights reserved