Method Article

Silicium-Metall-Oxid-Halbleiter-Quantenpunkte für Einzelelektronen Pumping

In diesem Artikel

Zusammenfassung

The fabrication process and experimental characterization techniques relevant to single-electron pumps based on silicon metal-oxide-semiconductor quantum dots are discussed.

Zusammenfassung

As mass-produced silicon transistors have reached the nano-scale, their behavior and performances are increasingly affected, and often deteriorated, by quantum mechanical effects such as tunneling through single dopants, scattering via interface defects, and discrete trap charge states. However, progress in silicon technology has shown that these phenomena can be harnessed and exploited for a new class of quantum-based electronics. Among others, multi-layer-gated silicon metal-oxide-semiconductor (MOS) technology can be used to control single charge or spin confined in electrostatically-defined quantum dots (QD). These QD-based devices are an excellent platform for quantum computing applications and, recently, it has been demonstrated that they can also be used as single-electron pumps, which are accurate sources of quantized current for metrological purposes. Here, we discuss in detail the fabrication protocol for silicon MOS QDs which is relevant to both quantum computing and quantum metrology applications. Moreover, we describe characterization methods to test the integrity of the devices after fabrication. Finally, we give a brief description of the measurement set-up used for charge pumping experiments and show representative results of electric current quantization.

Einleitung

Silicon is the material of choice for most of the modern microelectronics. Its properties, combined with advanced lithographic techniques, have allowed the semiconductor industry to achieve very large-scale integration and deliver billions of transistors per chip. The metal-oxide-semiconductor (MOS) technology1 has been the key of this relentless technological progress2. In brief, it is based on a selectively doped Si substrate which is thermally oxidized to grow a high quality SiO2 gate oxide on which a metal gate electrode is deposited. Recently, it has been shown that the use of a stack of gate oxides could be beneficial3 . While present industry standards have reached minimum feature sizes for gate lengths below 20 nm, it is becoming increasingly evident that, at this level of miniaturization, detrimental quantum mechanical phenomena come into play that may complicate further downscaling4.

Remarkably, silicon is also an excellent host material to exploit the quantum properties of the electron charge and spin5. This has broadened its range of applicability to entirely new fields such as quantum computing6 and quantum electrical metrology7. Among other approaches5, the use of a multi-gate MOS technology8,9 has led to electrostatically-defined quantum dots (QD) whose occupancy can be controlled down to single-electron level10. Unlike the conventional MOS process where just one gate per transistor is needed1, these QDs are defined via a three-layer stack of Al/AlyOx gates which are used to selectively accumulate electrons at the Si/SiO2 interface, as well as provide lateral and vertical confinement11.

Although these devices had been originally developed for quantum computing applications, they have also recently shown promising performances as metrological tools12,13. In the field of quantum electrical metrology, a long-standing goal is the redefinition of the unit ampere in terms of the elementary charge (e) 14. In particular, the emphasis is on the realization of nano-scale charge pumps to clock the transfer of individual electrons timely and accurately. These devices generate macroscopic quantized electric currents, I=nef, where f is the frequency of an external driving oscillator and n is an integer. To date, the best performance has been achieved with a GaAs-based pump by yielding a current in excess of 150 pA with a relative uncertainty of 1.2 parts per million15. Recently, silicon MOS QDs have also stood out for the implementation of highly accurate single-electron pumps thanks to the capability of finely tuning the charge confinement13.

Here, we discuss the protocol used for the fabrication of silicon MOS QDs. Furthermore, the cryogenic set-up used to test the integrity of the devices after fabrication and the one to perform charge pumping experiments are described. Finally, representative measurements of quantized electric current are reported.

Protokoll

Hinweis: Dieses Protokoll beschreibt die zur Herstellung, Verpackung und testen Einzelelektronenpumpen auf Basis von Silizium-MOS-Technologie QD Verfahren. Die in den Absätzen 1 und 2 diskutierten Schritte werden in einem Reinraum durchgeführt ISO5, während jene des § 3 sind in ISO6 Labors durchgeführt. Umgebungsbedingungen werden ständig kontrolliert. Sollwerte für Temperatur und Luftfeuchtigkeit werden bei 20 ± 1 ° C und 55% ± 5% eingestellt sind.

1. Microfabrication

- Feldoxid

- Reinigen des Wafers durch Eintauchen in die folgenden: Piranha Ätzung (10 min), entionisiertem (DI) Wasser (10 min), RCA-2-Lösung (VE-Wasser 175 ml, 30 ml HCl, H 2 O 2 30 ml bei 100 ° C für 10 min), entionisiertem Wasser (5 min), Fluorwasserstoffsäure (HF) in Wasser verdünnt, 10: 1 (10 sec), DI Wasser (10 min). Verwenden Sie Schutzkleidung beim Umgang mit HF (dh Schutzbrille, Schürze PVC und PVC-Handschuhe). Gehen Sie in der angegebenen Reihenfolge.

- Setzen Sie den Waferim Oxidationsofen bei 900 ° C und die Oxidation in Schritten wie folgt: Trocken O 2 (10 min), nasse O 2 (40 min), trockenen O 2 (10 min), N 2 (15 min).

- Ohmsche Kontakte

- Führen Sie Photolithographie und Ätzen Oxid.

- Zahlen Sie nur wenige nm dicken Haftvermittlerschicht Hexamethyldisilazan (HMDS) auf die Waferoberfläche wie folgt: pre-bake auf einer Heizplatte bei 110 ° C für 1 min, gießen ~ 50 ml HMDS in einem Becherglas, das Becherglas und der Wafer in die Vakuumkammer zu evakuieren, und warten, 2 min.

- Spin eine 2-4 um dicke Schicht Photolack auf beiden hinteren und vorderen Seiten des Wafers (3.000-5.000 UpM, 25-40 sec, je nach gewünschter Dicke).

- Aussetzen UV-Licht in Mask Aligner (10 mW / cm 2 für 4-10 sec nach Stärke widerstehen). Nachhärten auf einer Heizplatte bei 110 ° C für 1 min.

- Entwickeln Sie für 1-2 Minuten, dann in entionisiertem Wasser spülen.

- Führen O 2 Plasmaätzen für 20 min (Druck = 340 mTorr; einfallenden Leistung = 50 W reflektierte Leistung <1 W).

- Etch Oxid in gepufferter Fluorwasserstoffsäurelösung (15: 1, 4-5 min Ätzrate ≈ 20 nm / min bei 30 ° C). Spülen in deionisiertem Wasser (5 min). Föhnen mit N 2.

- Entfernen Fotolack durch Eintauchen in Aceton. Spülen in Isopropanol (IPA), dann föhnen mit N 2.

- Platzieren Wafer in einem Ofen bei 1000 ° C mit Phosphorquelle (N & sub2; -Strom für 30-45 min in Abhängigkeit von gewünschten Dotierungsdichte).

- Kontaminierte Oxidschicht mit HF-Säure in Wasser verdünnt (10: 1, 3-4 min, Ätzrate ≈ 40 nm / min bei 30 ° C) gründlich in entionisiertem Wasser (10 min).

- Oxidieren, wie in 1.1.2.

- Führen Sie Photolithographie und Ätzen Oxid.

- Gateoxid

- Wiederholen Sie die Schritte 1.2.1 und 1.2.2.

- Platzieren Wafer in speziellen Ofen bei 800 ° C und die Oxidation in Schritten wie folgt: Trocken O 2 (10 min), dichloroethylene + O 2 (20 min), trockenen O 2 (10-30 min in Abhängigkeit von gewünschten Oxiddicke), N 2 (15 min).

- Ohmsche Kontakte Metallisierung

- Wiederholen Sie Schritt 1.2.1.

- Platzieren Wafer in Elektronenstrahlverdampfer. Verdampfen 100 nm Aluminium auf 0,2-0,5 nm / sec und 5 x 10 -6 Torr.

- Einweichen des Wafers in N-Methyl-2-pyrrolidon (NMP) auf Heizplatte bei 80 ° C für 1 h zum Abheben des Metalls. Verwenden Ultraschallbewegung, wenn nötig. Spülen Sie in IPA für 2 min. Föhnen mit N 2.

- Temperung in Formiergas bei 400 ° C für mindestens 15 min.

2. Nanofabrication

- Wafer Dicing

- Spin jede wider auf den Wafer, um als Schutzschicht dienen (Art des Polymers und Spinnparameter sind irrelevant in dieser Phase).

- Diamantspitze verwenden Dicer, den Wafer in einzelne Chips von ca. 10 x 2 mm 2 geschnitten.

- Reinigung

- Tauchen Sie ein in NMP für 1 h auf Heizplatte bei 80 ° C, dann in IPA spülen für 2 min. Föhnen mit N 2.

- Führen O 2 Plasmaätzen für 5 min (einfallende Leistung = 50 W reflektierte Leistung <1 W).

- Spin sauber mit Aceton und IPA (7500 rpm, 30 s)

- Ausrichtmarkierungen Musterung

- Spin Polymethylmethacrylat (PMMA 950k) A4 Resist (5,000-7,500 rpm, 30 s in Abhängigkeit von der gewünschten Dicke). Typische Arbeitsdicke ≈ 150-200 nm. Backen Sie das Resist auf einer Heizplatte bei 180 ° C für 90 sec.

- Führen Sie Elektronenstrahllithographie. Verwenden Sie die folgenden Schreibbedingungen: Strahlenergie = 30 keV, Strahlstrom ≈ 30 pA, Ortsdosis ≈ 500-650 & mgr; C / cm 2, je nach Größe und Marker Lackdicke.

- Entwickeln des Resists in einer Lösung aus Methylisobutylketon und IPA (1: 3) für 40-60 Sekunden, dann in IPA spülen für 20 Sekunden. Föhnen mit N 2 gun.

- Platzder Chip in Elektronenstrahlverdampfer. Verdunsten 15 nm Ti und 65 nm von Pt bei 0,2-0,4 nm / s und 5 x 10 -6 Torr.

- Heben Sie den Metall wie in Schritt 1.4.3.

- Saubere Chip wie in den Schritten 2.2.2-2.2.3.

- Gatestrukturierungs

- Spin zu widerstehen, wie in 2.3.1.

- Führen Sie Elektronenstrahllithographie. Verwenden Sie die folgenden Schreib Bedingungen für Hochauflösung Features: Strahlenergie = 30 keV, Strahlstrom ≈ 30 pA, Ortsdosis ≈ 500-700 & mgr; C / cm 2. Schreiben Bedingungen für niedrige Auflösung Features: Strahlenergie = 15 keV, Strahlstrom ≈ 10 nA, Ortsdosis ≈ 400-600 & mgr; C / cm 2.

- Entwickeln des Resists, wie in 2.3.3.

- Platzieren Sie den Chip in thermischen Verdampfer. Verdampfen Al bei 0,1-0,4 nm / sec und 1-9 x 10 -6 mbar. Zielstärke je nach Schichtnummer, wie in Figur 2B (25-35 nm für die Schicht 1, 45-65 nm für die Schicht 2 gezeigt, 75-90 nm für Layer 3).

- Heben Sie den Metall wie in Schritt 1.4.3.

- Zuführen Al Oxidation auf einer Heizplatte bei 150 ° C für 5-10 min.

- Saubere Chip, wie in Schritt 2.2.3.

- Wiederholen Sie die Schritte 2.4.1-2.4.7 zweimal, um die 3-Schicht-Gate-Stapel zu realisieren.

3. Geräte-Verpackung

- Dice Chip, wie in Schritt 2.1

- Spülen Sie die daraus resultierenden kleineren Chips in Aceton und IPA für 2 min.

- Kleben Sie ein Einzelstück mit einer gedruckten Leiterplatte (PCB) mit PMMA A5. Warten Sie 2 Minuten, bis es trocken. Alternativ zur Thermalisierung zu verbessern, verwenden Silber Epoxy.

- Laden Sie die Platine auf eine Wedge-Bonder und fahren Sie mit Verkabelung.

4. Vorrichtung Integritätstests

- Montieren Sie die Platine mit dem drahtgebundenen Gerät auf eine Tauchsonde.

- Verdrahten Sie die elektrischen Leitungen der Leiterplatte, die denen der Tauchsonde.

- Stecken Sie die Sonde in ein Gefäß mit flüssigem Helium. Fahren Sie langsam, um übermäßige Helium b vermeidenÖl-off.

- Für jedes Gerät Tor, schließen Sie den entsprechenden Raumtemperatur-Elektrode der Sonde an eine Source-Measure-Einheit, während die anderen Gatter geerdet. Stellen Sie die Einhaltung der Strom auf wenige nA. Fegen Sie die Spannung von Null bis 1,5 V in Schritten von 0,1 V, zu messen und nehmen Sie das aktuelle.

- Verbinden jede Gateleitung auf eine batteriebetriebene variable Gleichspannungsquelle, die Source-Leitung auf dem integrierten Wechselspannungsquelle aus einem Lock-in-Verstärker und die Ablaufleitung mit dem Eingangsanschluss des Lock-in-Verstärker.

- Messen Sie die Quelle an Leitfähigkeit für verschiedene Gate-Spannung-Konfigurationen (siehe Abbildung 4) entleeren.

- Weltweit Rampe bis die Spannungen an die Gates BL, BR, PL, SL und DL, aufgebracht, indem C1 und C2 Tore geerdet. Notieren Sie die "Turn-on 'Geräteeigenschaften.

- Individuell Rampe ab jede Gate-Spannung und notieren Sie die Tore "Pinch-off 'Eigenschaften.

- Passen Sie die Gate-Spannungen elektrostatisch definieren eine quantum Punkt, indem die Spannungen an BL und BR (PL, SL und DL) kleiner (größer) als die Einschalt-Spannungen. Notieren Sie die Coulomb-Blockade Eigenschaften.

Ergebnisse

Vorrichtungsherstellungs

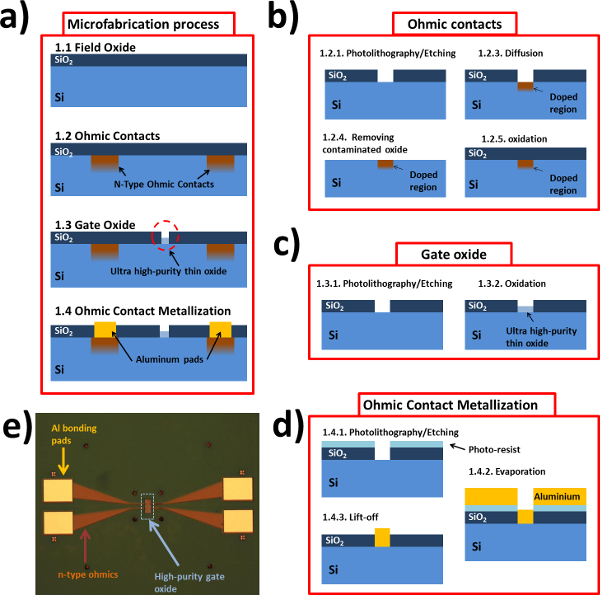

Die anfängliche Mikroprozess (Unterabschnitt 1 des Protokolls) auf einem kommerziellen 4-Zoll-hochreinen Silizium-Wafer durchgeführt (n-Typ-Dotierungskonzentration ≈ 10 12 cm -3; Widerstand> 10 kΩcm, Dicke = 310 bis 340 & mgr; m ). Das Ziel ist es, das Substrat, auf dem die Gate-Elektroden abgeschieden wird realisieren. Dieses Substrat besteht aus einem intrinsischen Bereich mit Feldoxid (Schritt 1.1), einem n + -Bereich mit Feldoxid (Schritt 1.2), einer Eigenleitungsbereich mit hochwertigen Gateoxid (Schritt 1.3) verschlossen capped eingekapselt wird, und eine metallisierte n + Region Ohmsche Kontakte (Schritt 1.4). 1A-D zeigen die Hauptschritte des Mikroprozesses. 1E zeigt eine mikroskopische Aufnahme eines Substrats Feld nach Mikro. Die minimale Merkmalsgröße für die Lithographie bei dieser Stufe beträgt etwa 4 um.

Die SiO2-Oxid-Schicht in Schritt 1.1 gezüchtet hat eine nominale Dicke von 100 nm auf und ist als Passivierungsschicht verwendet wird. Die n-Typ-Bereiche, die als ohmsche Leiter wirken über Phosphordiffusion erhalten. Die Zieldotierungsdichte beträgt ca. 19. Oktober - 20. Oktober cm -3. Das hochwertige SiO 2, die selektiv gewachsen wird als Gate-Dielektrikum verwendet wird, hat eine nominelle Dicke von 5 nm. Die Zielschnittdefektdichte <10 10 eV -1 cm -2 in der Mitte der Lücke. Ein engagiertes und absichtlich eingebaute Dreifachwandofen für dieses Verfahren verwendet. Dieses System wurde entwickelt, um eine Verunreinigung von Schwermetallionen und mobilen Alkaliionen zu minimieren, als auch von Feuchtigkeit zu vermeiden Diffusion in die Oxidationskammer. Um die elektrischen Kontakte zu bilden, werden Aluminiumpads über Elektronenstrahlverdampfung auf einem Teil der n-Typ-Bereichen abgeschieden.

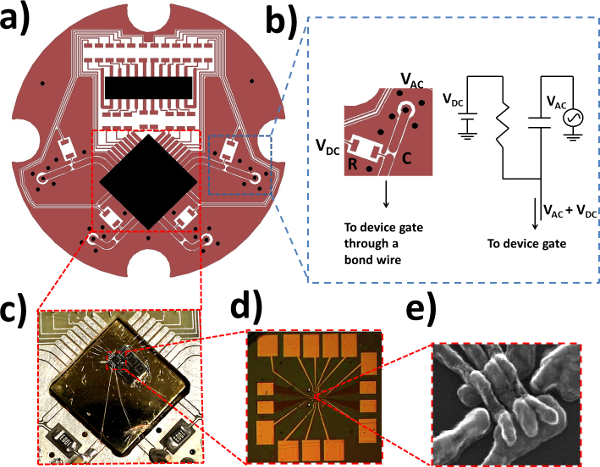

Die Nanofabrikationsprozess (siehe Unterabschnitt 2) auf dem Chip durchgeführt substrates durch Zerteilen des Wafers in Schritt 1 Ziel verarbeitet erhalten ist es, die nanoskalige Gate-Elektroden verwendet, um elektrostatisch definieren die MOS QDs zu realisieren. Jeder Nanofabrikation Lauf erzeugt typischerweise 10-15 Komplettgerät Proben. Rasterelektronenmikroskopische Aufnahme (REM) Abbildung 1-2 Geräte pro Charge wird in der Regel durchgeführt, um zu bestätigen, dass die EBL Lithographieschritte erfolgreich waren. Da SEM-Bildgebung kann Ladungen in das Substrat oder in die metallischen Gates einspritzen und Leckagen, ist nur eine geringe Anzahl von Vorrichtungen auf diese Weise überprüft, während die übrigen elektrisch getestet. Minimale Merkmalsgröße für die Lithographie in dieser Stufe beträgt etwa 35 nm. Um eine gute Homogenität der abgeschiedenen Al-Filme zu erreichen, wird das Metall mit Raten so niedrig wie wenige Angström / s verdampft wird, während das Substrat auf einem Drehtisch montiert. Dies wird bei RT gehalten und die Al Korngröße wird auf von etwa 20 nm sein. 2A zeigt die Hauptschritte des nanofabrication Prozess. 2B zeigt eine SEM-Bild, mit dem die korrekte Definition der Gate-Elektroden überprüft wird. In der Regel soll eine an die Verwirklichung dieser Tore, die die QD direkt definieren (BL, BR und PL) mit der kleinstmöglichen Strukturgröße. Im Gegensatz dazu können diese Gates verwendet, um die Elektronenreservoirs (DL und SL) zu definieren, um den größeren Abmessungen unbeabsichtigtes Diskretisierung der Energieniveaus in den Leitungen zu vermeiden. Die nanoskaligen Ti / Pt-Marker in Schritt 2.3 realisiert werden als Referenz für konsistente Ausrichtung der drei Schichten von Gattern verwendet. Platin ist für seine hervorragenden Kontrast in Bezug auf die SiO 2 -Oberfläche in der E-Strahl ausgewählt. Titan wird verwendet, um die Haftung zu verbessern.

In allen Phasen des Herstellungsprozesses werden kohlefaser Spitze Pinzette verwendet, um die Chips zu behandeln, um die Wahrscheinlichkeit einer destruktiven elektrostatische Entladung (ESD) zu reduzieren.

Schließlich, um elektrische Messungen an indivi auszuführenDual Vorrichtungen benötigt jeder Chip in kleinere Stücke von etwa 2 x 2 mm 2 (Ziffer 3) abgespalten werden. Jedes Stück wird dann auf eine maßgeschneiderte PCB (Rogers R03010 verlustarmen Dielektrikum), deren Stifte an die Einrichtungselektroden durch Al Drähten verbunden geklebt. Drahtbonden mit einem Keilbondmaschine ohne Erwärmen der Chips durchgeführt. Die Auswahl der geeigneten Bindungsparameter ist auf zwei Überlegungen. Auf der einen Seite muss der Drahtverbindung, um die thermische Al y O x Schicht perforieren und gute Metall-auf-Metall-Kontakt mit der Gate-Pad. Auf der anderen Seite kann ein übermäßiger mechanischer Beanspruchung in einem Stempel-Trog Ereignis, das Schäden des Feldoxids unter der Gate- und der Ursache Substrat Leckagen führen. Während des Verdrahtungsprozesses ist die Verwendung eines antistatischen Armband ratsam ESD zu verhindern. In Figur 3 ist ein Chip mit 6 einzelnen Vorrichtungen auf der Leiterplatte verklebt.

Gerät Integritätstests

Vore Laden einer Vorrichtung in einen mK Temperaturmessung Plattform wie beispielsweise ein Verdünnungskühler, werden vorläufige elektrischen Tests bei 4,2 K durchgeführt, um die Integrität der Probe (siehe Unterabschnitt 4 des Protokolls) zu überprüfen. Zu diesem Zweck wird die Leiterplatte in einer sauerstofffreien Kupfergehäuse eingesetzt ist und auf eine Tauchsonde, die schließlich in flüssigem He eingetaucht angeordnet ist.

Die Erstprüfung ist typischerweise eine Dichtheitsprüfung, die der Reihe nach auf jedem Tor durchgeführt wird. Eine Quelle-Messeinheit ist mit einer einzelnen Gate-Elektrode verbunden, während die andere geerdet sind. Die Spannung bis auf 1,5 V hochgefahren und der Strom wird an der Quelle gemessen. Innerhalb dieses Spannungsbereichs ist ein ordnungsgemäß arbeit Gate eigentlich nicht zu leiten, weil die SiO 2 -Schicht isoliert das Metall aus dem Siliziumsubstrat und Al y O x dämmt überlappende Gates. Typischerweise wird Oxiddurchbruch bekannt, für Spannungen auftreten, die größer als 4 V ~, je nach Gerätegeometrie und Oxid thickness. Deshalb, wenn Strom durch den Test erfaßt wird, ist es wahrscheinlich, dass mindestens eine der Oxidschichten beschädigt ist und die Vorrichtung weggeworfen werden. In der Regel weniger als 10% der Tore zeigen Leckagen. Die Ausbeute ist bekannt, dass durch die flächige Ausdehnung der Gateelektroden berührt. Insbesondere, je größer die Überlappung der Tore mit dem Gateoxidbereich desto wahrscheinlicher wird es sein, Gate-zu-Substrat-Leckagen aufweisen. Ebenso werden je größer die Überlappung zwischen den Gates von verschiedenen Schichten, desto wahrscheinlicher das Auftreten von Gate-zu-Gate-Lecks auftreten. Die angegebene Ausbeute für Tore, die eine Fläche von etwa 50 & mgr; m 2 auf der dünnen Oxidschicht besetzen relevant und mit Zwischenschicht überdeckt von etwa 0,5 & mgr; m 2.

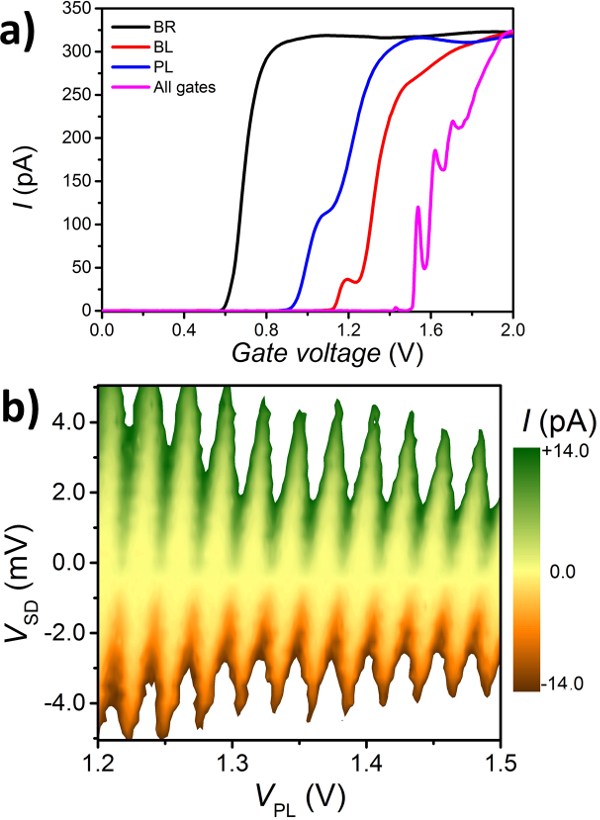

Sobald das Gerät den anfänglichen Lecktest bestanden, werden die Source- und Drain-Kontakte zu einem Lock-in-Verstärker und den Gates eine modulare steuerbare Spannungsbatterie Gestell verbunden ist. In dieser Konfiguration ist die Vorrichtung o gedrehtn durch global Hochfahren alle Gate-Spannungen gleichzeitig. Als nächstes wird jede Gatespannung getrennt heruntergefahren, während die andere bei hohen Spannungen, um die Fähigkeit der einzelnen Gates abzukneifen den Strom zu verifizieren. 4A zeigt repräsentative Spuren dieser Messungen. Die Abwesenheit von entweder einer Source-Drain-Leitungsweg oder einzelne Gate Abschnürspannung ist oft ein Hinweis auf eine Art von Gate-Schäden wie Gate-Explosion oder Metall Diskontinuität.

Schließlich wird die Source-Drain-Strom als Funktion der Source-Drain-Vorspannung und dem Kolben Gate-Spannung, um die Signatur des Coulomb-Blockade-16 (siehe 4B) zu beobachten gemessen.

Messungen

Sobald ein geeignetes Gerät gefunden wurde, wird es aus dem flüssigen Er Gefäß entfernt und mit einem Heißluftgebläse getrocknet, um die Bildung von Feuchtigkeit, die ESD führen, zu vermeiden. Schließlich ist es mit einer Verdünnungskühler überführt.

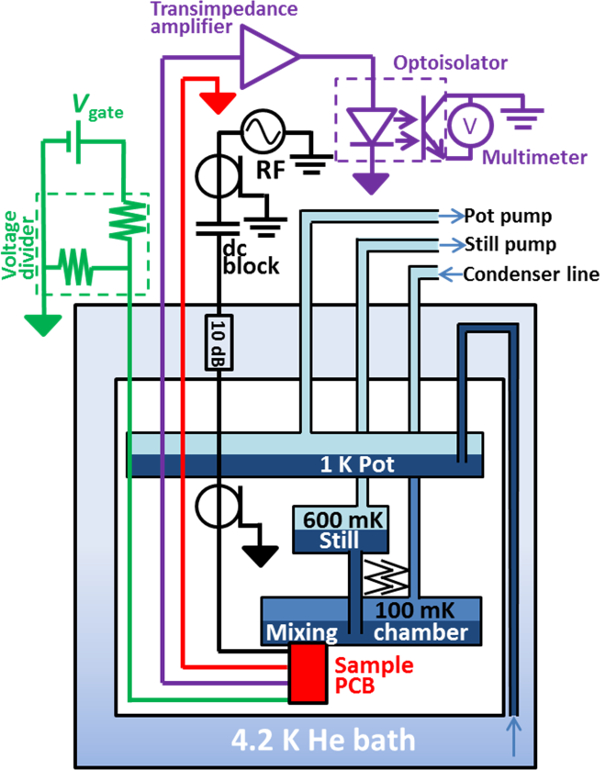

Die Versuche werden in einem selbstgebauten Kunststoffverdünnungskühler mit einer Basistemperatur von etwa 100 mK durchgeführt. Der Kryostat ist in einer Vakuumkammer in einem 4,2 K Helium getaucht. Die elektrischen Leitungen werden mit dem 1 K Pot, die auch verwendet wird, um den eingehenden 3He Dampf zu kondensieren thermalisiert. In der Mischkammer, die endotherme Übertragung von 3He Atome aus der 3He-reiche Phase in die 3He-verdünnte Phase ermöglicht dem System, eine Basistemperatur von etwa 100 mK erreichen.

Wie in 5 gezeigt, ist der Kühlschrank mit 20 DC-Leitungen und 3 verwendet, um die Raumtemperatur-Elektronik an das Gerät bei niedriger Temperatur verbinden HF-Leitungen ausgestattet. Fünf der DC-Leitungen sind Thermocoax Kabel und 15 Twisted-Pair-Kabel Webstuhl. Diese Leitungen verbinden die Gate-Elektroden der Probe auf batteriebetriebene Gleichspannungsquellen. Spannungsteiler bei RT werden verwendet, um elektrisches Rauschen auf einzelnen Gates reduzieren. Die HF-Leitungen sind halbstarre Koaxialkabel, das sind von 10 dB bei 4 K gedämpft, um das thermische Rauschen und DC bei RT blockiert reduzieren. Diese Leitungen werden auf der koplanaren Wellenleiter der Bias Tees auf der Leiterplatte verbunden ist.

Ein geräuscharmer Transimpedanzverstärker und einen digitalen Multimeter verwendet, um den von der Pumpe erzeugten Strom zu messen. Die Elektronik ist zum Gerät über batteriebetriebene Optoisolatoren verbunden sind, um die Bildung von Masseschleifen zu vermeiden. Die HF-Treibersignale werden von einem Signalgenerator, dessen Erdung von dem einen des Kryostaten über einen Gleichstromblockkomponente getrennt hergestellt (siehe Abbildung 5).

Die Leiterplatte enthält 16 reine DC-Leitungen und 4 verwendet werden, um Gleich- und Wechselspannungen bei niedriger Temperatur verbinden Bias-Tee Linien. Wie in 3B gezeigt, werden RC diskrete Komponenten benutzt, um die T-Verbindung (R = 100 k, C = 10 nF) zu realisieren, und 50 Ω abgestimmte integrierten koplanaren Wellenleiter für die Ausbreitung von Hochfrequenzsignalen verwendet wird.

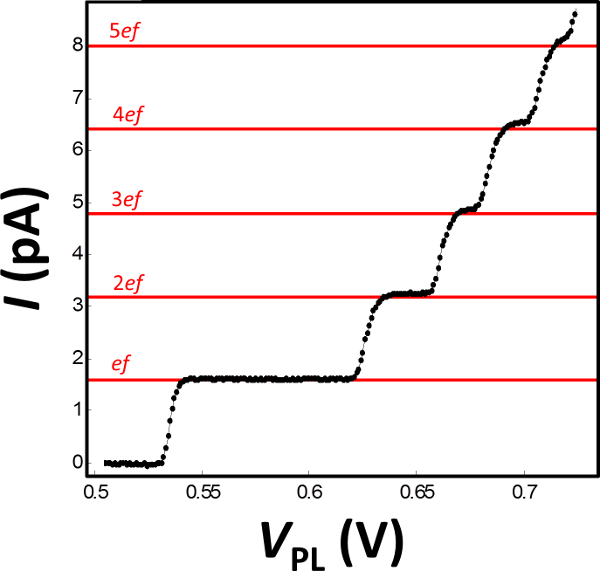

e_content "> Sobald das Gerät an mK Temperatur ist, werden die Gate-Spannungen so eingestellt, daß Einzelelektronenbelegung im QD erreicht wird. Insbesondere Tunnelbarrieren unter Gates BL und BR gebildet, und eine Elektronenansammlungsschicht unter Gates induziert PL, SL und DL. Zu diesem Zweck wird die Barriere Gate-Spannungen sind unten ihre Einschalt-Werte festgelegt, während die Akkumulationsgates an polarisiert ein Größer-als-Einsatzspannung. Auf diese Weise wird unter dem Gate PL a QD gebildet und seine planare Ausdehnung ist über Gatter C1 und C2, deren Spannungen unterhalb ihrer Einschaltspannung Werte gehalten, um eine elektrostatische Eindämmung induzieren die elektro gesteuert. Als nächstes werden die HF-Signale eingeschaltet wird, um periodisch die Transparenz der Tunnelbarriere (n) zu modulieren, und Potential des Punkts. Einelektronenschritten Pumpen mit einem oder zwei sinusförmigen Antriebsspannungen erreicht wird. Im Falle einer Signalplatte wird das Treibersignal an die Gate BL angelegt, um das Potential der Tunnelbarriere an der linken modulieren -Seite vondie QD. Im Fall des Zweisignal Antrieb sind die ac Anregungen an Gates BL und PL angewendet, um die Potentiale sowohl der linken als Barriere und QD bei der gleichen Frequenz, aber mit unterschiedlichen Phasen und Amplituden zu modulieren. Diese zusätzlichen Freiheitsgrade ermöglichen es, die Richtung des Elektronentransfers 13 steuern. Ein iterativer Prozess ist in der Regel stimmen die wichtigsten experimentellen Parameter (dh HF-Treibersignalamplituden / Phasen und DC-Gate-Spannungen) und eine optimale Strom Quantisierung erforderlich. Man beachte, daß keiner der beiden Pump Protokolle benötigt einen Drain-Source-Vorspannung an Ladungstransfers durchzuführen. Somit sind die Source- und Drain-Elektroden während des Pumpenbetriebs geerdet. 6 zeigt die charakteristische Stromplateaus bei ganzzahligen Vielfachen ef durch Aufbringen eines Zweisignal sinusförmig Antrieb auf die Eingangsschranke (BL) und dem Kolben (PL) Gate erhalten. Diese Daten werden mit einer relativ niedrigen Antriebsfrequenz (10 MHz), für welche die T getroffen uning der Parameter kann schnell durchgeführt werden. In der Praxis ist es wünschenswert, dass die Pumpe bei mehreren hundert MHz arbeiten, erfordern typischerweise eine viel feinere Parameteroptimierung 13.

Abbildung 1. Mikrofabrikation. (A) Schematische Darstellung der wichtigsten Schritte in Mikro. Cartoons sind nicht maßstabsgetreu gezeichnet. (B) Umsetzung eines dotierten Bereich für ohmsche Kontakte. (C) Umsetzung des Gateoxids. (D) Die Metallisierung der ohmschen Kontakte. (E) Mikroskopische Aufnahme eines einzelnen Feldes auf einem Chip nach dem Mikrofabrikationsprozess ist abgeschlossen. Feldgröße ist 1,2 x 1,2 mm 2. Bitte klicken Sie hier, um eine größere Version dieser Figur zu sehen.

Abbildung 2. Nanofabrikation. (A) Herstellungsverfahren für die einzelnen Gate-Schichten. Cartoons sind nicht maßstabsgetreu gezeichnet. (B) Das 3-Schicht-Gate-Nanostruktur für Ladungspumpen Experimente verwendet. Links: REM-Aufnahme einer Vorrichtung, die ähnlich zu der für die Messungen verwendet. Rechts:. Schematische Querschnittsansichten der Vorrichtung in X-Schnitt und Y-Schnitt Bitte klicken Sie hier, um eine größere Version dieser Figur zu sehen.

Abbildung 3. Elektrische Anschlüsse an der Probe. (A) Layout der Leiterplatte. (B) Vergrößerung einer Region der Leiterplatte mit einer Bias-T-Stück (links) eind äquivalente Schaltung (rechts). (C) ein Chip mit 6 einzelnen Felder auf der Chiphalter und Bonddrähte zum elektrischen Verbinden mit der Leiterplatte verklebt. (D) Mikroskopische Aufnahme eines einzelnen Feld nach Nanofabrikation. (E) SEM-Bild des Tores das Layout in der Mitte der Gate-Oxid-Region. Bitte klicken Sie hier, um eine größere Version dieser Figur zu sehen.

Abbildung 4. Vorläufige Tests. (A) Source-Drain-Wechselstrom (Root Mean Square) in Abhängigkeit von unterschiedlichen Gate-Spannungen. Spuren sind mit einem Lock-in-Verstärker mit 50 & mgr; V RMS Anregung bei 113,17 Hz gemessen. Für individuelle Gate-Spannung verfolgt die verbleibenden Gate-Spannungen sind bei 2,0 V festgelegt ist, mit Ausnahme von V C1 = Vc2 = 0,0 V (B) Farbkarte von Source-Drain-Strom als eine Funktion der Plunger-Gate-Spannung und der Source-Drain-Vorspannung. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, BR V = 0,85 V, V C1 = C2 = 0,0 V V. Bitte klicken Sie hier, um eine größere Version dieser Figur zu sehen.

Abbildung 5: Schematische Darstellung des Messaufbaus. Zwanzig DC-Leitungen (grün) und drei koaxiale HF-Leitungen (schwarz) verbinden die RT-Elektronik auf der Leiterplatte. Der Drain der Pumpe (lila) wird zu einer Transimpedanzverstärker und einem Digitalmultimeter über einen Optokoppler verbunden ist, während der Source-Kontakt (rot) ist geerdet. Separate Erdungsanschlüsse (imit verschiedenen Symbolen ndicated) für die elektronische Instrumentierung und den Kryostaten elektrischen Leitungen verwendet werden. Bitte klicken Sie hier, um eine größere Version dieser Figur zu sehen.

Figur 6. Diese Quantisierung. Pumpstrom als Funktion von V PL für Zweisignal sinusförmig Antriebs bei f = 10 MHz den Gates BL und PL angelegt. Phasenunterschied = 49 °, V RF PL = V RF BL = 0,31 V pp. Die ideale Lage des Pump Plateaus bei ganzzahligen Vielfachen von ef sind als rote horizontale Linien dargestellt. Bitte klicken Sie hier, um eine größere Version dieser Figur zu sehen.

Diskussion

Das Protokoll in dieser Veröffentlichung beschreibt die Techniken zu fertigen Silizium-MOS-QDs, sowie die experimentellen Verfahren, um ihre Funktionsfähigkeit zu testen und betreiben sie als Einzelelektronenpumpen. Bemerkenswert ist, durch Anpassen der Gate-Design, kann das gleiche Herstellungsverfahren eingesetzt werden, um Geräte für den Quanten-Bit-Anzeige und Steuerung 17 sowie Ladungspump 12,13 produzieren. Wir stellen fest, dass viele der Prozessparameter in diesem Artikel zitiert kann variieren in Abhängigkeit von den Herstellungswerkzeuge verwendet (Kalibrierung, Marke oder Modell), sowie von der Art der Silizium-Substrat (Dicke und Hintergrunddotierungsdichte). Größen wie Lithographie-Belichtungsdosis oder die Entwicklungszeit, Ätzen oder Oxidation Dauer, müssen sorgfältig kalibriert und getestet, um eine verlässliche Rendite zu gewährleisten. Weiterhin ist es von entscheidender Bedeutung, um eine Kreuzkontamination, die aus der Verwendung der gleichen Herstellungswerkzeuge für unterschiedliche Prozesse zu vermeiden. Zu diesem Zweck ist eine Anzahl von crtische Schritte mit Geräten durchgeführt ausschließlich Siliziumverarbeitung gewidmet wie Metallverdampfer, Sauerstofföfen und HF Bäder.

Allgemeiner wird Silizium Zeichnung ein wachsendes Interesse als das Material der Wahl, um Ladungspumpen 18-20 realisieren. Dies ist zum Teil auf die attraktive Perspektive der Umsetzung einer neuen Quanten-basierten elektrischen Strom mit Hilfe eines Standard-Industrie-kompatiblen Siliziumprozess. Dies würde aus etablierten und zuverlässigen Integrationstechniken für Skalierbarkeit, Parallelisierung und Fahraufwand profitieren. Wichtig ist, dass eine vollständige komplementäre MOS (CMOS) Technologie, frei von traditionellen Metall als Gate-Material, stark reduziert Hintergrundladungsfluktuationen in Einzelelektronenvorrichtungen 21 dargestellt. Solche Schwankungen können sich schädlich bei der Erreichung messtechnische Genauigkeit ist.

Die hier diskutierten Protokoll zur Realisierung von MOS Nanogeräte mit Metallgates begrenzt. Deshalb, um Achieve volle Industrietauglichkeit und Ladungsfluktuationen reduzieren, ist es notwendig wäre, um die Gate-Abscheidungstechniken modifizieren und hochdotierten polykristallinen Silicium als Gate-Material sein.

Zusammenfassend haben die MOS-QD Pumpen hier diskutierten kürzlich kombiniert den technologischen Vorsprung von Silizium mit einer sehr guten Leistung in Bezug auf genaue aktuelle Generation 13. Dies ergibt sich aus der hohen Flexibilität der Konstruktion und Herstellungsverfahren, die ein bis mehrere Gate-Schichten, die zu einer kompakten und vielseitigen System-Stack zu ermöglichen. Das so erhaltene feine Einstellbarkeit des elektrostatischen Begrenzung des Punkt zusammen mit dem Potential, um Hintergrundladungsfluktuationen reduzieren die Bühne zu überwinden die wichtigsten Herausforderungen in anderen Halbleiter beobachtet Pumpen 22,23.

Offenlegungen

Die Autoren haben nichts zu offenbaren.

Danksagungen

Wir danken KY Tan, P. See und GC Tettamanzi für hilfreiche Diskussionen. Wir danken für die finanzielle Unterstützung aus dem Australian Research Council (Grant No DP120104710), der Akademie von Finnland (Erteilungsnummer 251748, 135794, 272806) und Unterstützung von der Australian National Herstellungsanlage für die Herstellung von Bauelementen. AR erkennt finanzielle Unterstützung von der University of New South Wales Early Career Researcher Grant-Schema. Die Bereitstellung von Einrichtungen und technische Unterstützung von Aalto-Universität in Micronova Nanofabrication Center wird auch anerkannt.

Materialien

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

Referenzen

- Sze, S. M. . Physics of Semiconductor Devices. , 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930 (2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).

Nachdrucke und Genehmigungen

Genehmigung beantragen, um den Text oder die Abbildungen dieses JoVE-Artikels zu verwenden

Genehmigung beantragenWeitere Artikel entdecken

This article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. Alle Rechte vorbehalten