Method Article

De silicio metal-óxido-semiconductor Quantum Dots para Bombeo solo electrón

En este artículo

Resumen

The fabrication process and experimental characterization techniques relevant to single-electron pumps based on silicon metal-oxide-semiconductor quantum dots are discussed.

Resumen

As mass-produced silicon transistors have reached the nano-scale, their behavior and performances are increasingly affected, and often deteriorated, by quantum mechanical effects such as tunneling through single dopants, scattering via interface defects, and discrete trap charge states. However, progress in silicon technology has shown that these phenomena can be harnessed and exploited for a new class of quantum-based electronics. Among others, multi-layer-gated silicon metal-oxide-semiconductor (MOS) technology can be used to control single charge or spin confined in electrostatically-defined quantum dots (QD). These QD-based devices are an excellent platform for quantum computing applications and, recently, it has been demonstrated that they can also be used as single-electron pumps, which are accurate sources of quantized current for metrological purposes. Here, we discuss in detail the fabrication protocol for silicon MOS QDs which is relevant to both quantum computing and quantum metrology applications. Moreover, we describe characterization methods to test the integrity of the devices after fabrication. Finally, we give a brief description of the measurement set-up used for charge pumping experiments and show representative results of electric current quantization.

Introducción

Silicon is the material of choice for most of the modern microelectronics. Its properties, combined with advanced lithographic techniques, have allowed the semiconductor industry to achieve very large-scale integration and deliver billions of transistors per chip. The metal-oxide-semiconductor (MOS) technology1 has been the key of this relentless technological progress2. In brief, it is based on a selectively doped Si substrate which is thermally oxidized to grow a high quality SiO2 gate oxide on which a metal gate electrode is deposited. Recently, it has been shown that the use of a stack of gate oxides could be beneficial3 . While present industry standards have reached minimum feature sizes for gate lengths below 20 nm, it is becoming increasingly evident that, at this level of miniaturization, detrimental quantum mechanical phenomena come into play that may complicate further downscaling4.

Remarkably, silicon is also an excellent host material to exploit the quantum properties of the electron charge and spin5. This has broadened its range of applicability to entirely new fields such as quantum computing6 and quantum electrical metrology7. Among other approaches5, the use of a multi-gate MOS technology8,9 has led to electrostatically-defined quantum dots (QD) whose occupancy can be controlled down to single-electron level10. Unlike the conventional MOS process where just one gate per transistor is needed1, these QDs are defined via a three-layer stack of Al/AlyOx gates which are used to selectively accumulate electrons at the Si/SiO2 interface, as well as provide lateral and vertical confinement11.

Although these devices had been originally developed for quantum computing applications, they have also recently shown promising performances as metrological tools12,13. In the field of quantum electrical metrology, a long-standing goal is the redefinition of the unit ampere in terms of the elementary charge (e) 14. In particular, the emphasis is on the realization of nano-scale charge pumps to clock the transfer of individual electrons timely and accurately. These devices generate macroscopic quantized electric currents, I=nef, where f is the frequency of an external driving oscillator and n is an integer. To date, the best performance has been achieved with a GaAs-based pump by yielding a current in excess of 150 pA with a relative uncertainty of 1.2 parts per million15. Recently, silicon MOS QDs have also stood out for the implementation of highly accurate single-electron pumps thanks to the capability of finely tuning the charge confinement13.

Here, we discuss the protocol used for the fabrication of silicon MOS QDs. Furthermore, the cryogenic set-up used to test the integrity of the devices after fabrication and the one to perform charge pumping experiments are described. Finally, representative measurements of quantized electric current are reported.

Protocolo

Nota: Este protocolo describe los procedimientos utilizados para fabricar, empaquetar y probar las bombas de un solo electrón basados en silicio tecnología MOS QD. Los pasos discutidos en sub-secciones 1 y 2 se llevan a cabo en una sala blanca ISO5, mientras que las de la sección 3 se realizan en laboratorios ISO6. Condiciones ambientales son controlados continuamente. Los valores nominales para la temperatura y la humedad se fijan a 20 ± 1 ° C y 55% ± 5%, respectivamente.

1. microfabricación

- El campo Óxido

- Limpiar la oblea por inmersión en lo siguiente: etch piraña (10 min), agua desionizada (DI) agua (10 min), solución de RCA-2 (DI 175 ml de agua, HCl 30 ml, H 2 O 2 30 ml a 100 ° C durante 10 min), agua desionizada (5 min), fluorhídrico HF) ácido (diluido en agua 10: 1 (10 seg), agua DI (10 min). Utilice prendas de protección al manipular HF (es decir, gafas, delantal y guantes de PVC, PVC). Proceder en el orden indicado.

- Coloque la obleaen horno de oxidación a 900 ° C y oxidar en los pasos de la siguiente manera: O seco 2 (10 min), O mojada 2 (40 min), O 2 seco (10 min), N 2 (15 min).

- Contactos óhmicos

- Llevar a cabo la fotolitografía y óxido de grabado.

- Depositar una capa de unos pocos nm de espesor de promotor de la adhesión hexametildisilazano (HMDS) en la superficie de la oblea de la siguiente manera: pre-hornear en una placa caliente a 110 ° C durante 1 min, se vierte ~ 50 ml de HMDS en un vaso de precipitados de vidrio, colocar el vaso de precipitados y la oblea en la cámara de vacío, evacuar y esperar a 2 min.

- Haga girar un 2-4 micras de espesor de capa de resina fotosensible tanto atrás y los lados frontales de la oblea (3.000-5.000 rpm, 25-40 seg dependiendo del grosor deseado).

- Exponer a la luz ultravioleta en alineador de máscara (10 mW / cm2 durante 4-10 seg acuerdo para resistir espesor). Post-bake en una placa caliente a 110 ° C durante 1 min.

- Desarrollar durante 1-2 minutos, luego enjuague con agua desionizada.

- Realizar O grabado 2 plasma durante 20 min (presión = 340 mTorr; potencia incidente = 50 W; potencia reflejada <1 W).

- Óxido de Etch en solución de ácido HF tamponada (15: 1, 4-5 min, velocidad de ataque ≈ 20 nm / min a 30 ° C). Enjuague con agua desionizada (5 min). Golpe seco con N 2.

- Retire fotoprotector por inmersión en acetona. Enjuague en isopropanol (IPA), a continuación, secar con N 2.

- Coloque la oblea en horno a 1000 ° C, con fuente de fósforo (flujo de N2 durante 30-45 minutos, dependiendo de la densidad de dopaje se desea).

- Eliminar la capa de óxido contaminada con ácido HF diluido en agua (10: 1, 3-4 min, velocidad de grabado ≈ 40 nm / min a 30 ° C), enjuague en agua desionizada (10 min).

- Oxidar como en 1.1.2.

- Llevar a cabo la fotolitografía y óxido de grabado.

- Puerta Óxido

- Repita los pasos 1.2.1 y 1.2.2.

- Coloque la oblea en el horno dedicado a 800 ° C y oxidar en los pasos de la siguiente manera: O seco 2 (10 min), dichloroethylene + O 2 (20 min), O seco 2 (10-30 min dependiendo del espesor de óxido deseado), N 2 (15 min).

- Contactos óhmicos Metalización

- Repita el paso 1.2.1.

- Coloque la oblea en el evaporador de haz de electrones. Evaporar 100 nm de aluminio a 0,2-0,5 nm / seg y 5 x 10 -6 Torr.

- Remoje la oblea en N-metil-2-pirrolidona (NMP) en placa caliente a 80 ° C durante 1 hora para levantar el metal. Utilice agitación ultrasónica si es necesario. Enjuague en IPA durante 2 min. Golpe seco con N 2.

- Recocido en la formación de gas a 400 ° C durante al menos 15 min.

2. Nanofabricación

- Wafer Dicing

- Haga girar cualquier resisten sobre la oblea para que actúe como capa protectora (tipo de parámetros de polímero e hilatura son irrelevantes en esta etapa).

- Utilice dicer punta de diamante para cortar la oblea en chips individuales de ~ 10 x 2 mm 2.

- Limpieza

- Remojar en NMP durante 1 hora en la placa caliente a 80 ° C, luego enjuague en IPA durante 2 min. Golpe seco con N 2.

- Realizar O grabado 2 plasma durante 5 min (potencia incidente = 50 W; potencia reflejada <1 W).

- Haga girar limpia con acetona e IPA (7500 rpm, 30 seg)

- Marcadores de alineación de patrones

- Girar polimetacrilato de metilo (PMMA 950k) A4 resistir (5,000-7,500 rpm, 30 segundos dependiendo del grosor deseado). Espesor de trabajo típico ≈ 150-200 nm. Hornee el resistir en una placa caliente a 180 ° C durante 90 segundos.

- Llevar a cabo la litografía por haz de electrones. Utilice las siguientes condiciones de escritura: la energía del haz = 30 keV, corriente del haz ≈ 30 pA, dosis zona ≈ 500-650 mu c / cm 2 en función de los marcadores de tamaño y resistir espesor.

- Desarrollar el resistir en una solución de metilisobutilcetona y el IPA (1: 3) para 40-60 segundos, luego enjuague en IPA durante 20 s. Golpe seco con N 2 arma.

- Lugarel chip en el evaporador de haz de electrones. Evaporar 15 nm de Ti y 65 nm de Pt al 0,2-0,4 nm / seg y 5 x 10 -6 Torr.

- Levante el metal como en el paso 1.4.3.

- Viruta limpia como en los pasos 2.2.2-2.2.3.

- Los patrones de puerta

- Vuelta a resistir como en 2.3.1.

- Llevar a cabo la litografía por haz de electrones. Utilice las siguientes condiciones de escritura para funciones de alta resolución: la energía del haz = 30 keV, corriente del haz ≈ 30 pA, área dosis ≈ 500-700 mu c / cm 2. Escribe condiciones para las características de baja resolución: energía del haz = 15 keV, corriente del haz ≈ 10 nA, área dosis ≈ 400-600 mu c / cm 2.

- Desarrollar el resistir como en 2.3.3.

- Coloque el chip en el evaporador térmico. Se evapora Al en 0,1 hasta 0,4 nm / seg y 9.1 x 10 -6 mbar. Target espesor varía según el número de capa, como se muestra en la Figura 2B (25-35 nm para la Capa 1, 45-65 nm para la Capa 2, 75-90 nm para la Capa 3).

- Levante el metal como en el paso 1.4.3.

- Realice Al oxidación sobre una placa caliente a 150 ° C durante 5-10 minutos.

- Viruta limpia como en el paso 2.2.3.

- Repita los pasos dos veces 2.4.1-2.4.7 se den cuenta de la pila de puerta de 3 capas.

3. Dispositivo de embalaje

- Chips dados como en el paso 2.1

- Enjuague los chips más pequeños que resultan en acetona y IPA durante 2 min.

- Pegue una pieza individual de una placa de circuito impreso (PCB) con PMMA A5. Espere 2 minutos para que se seque. Alternativamente, para mejorar thermalization, utilizar epoxi plata.

- Cargue el PCB en un dispositivo de unión de cuña y proceder con el cableado.

4. Las pruebas de integridad del dispositivo

- Monte el PCB que contiene el dispositivo cableado a una sonda de inmersión.

- Cablear las líneas eléctricas de la PCB a los de la sonda de inmersión.

- Inserte la sonda en un recipiente que contiene helio líquido. Proceda lentamente para evitar el exceso de helio baceite-off.

- Para cada dispositivo de puerta, conecte el correspondiente electrodo a temperatura ambiente de la sonda a una unidad de fuente-medida, manteniendo las otras puertas conectadas a tierra. Ajuste la corriente del cumplimiento de algunas nA. Barra el voltaje de cero a 1,5 V en pasos de 0,1 V, medir y registrar la corriente.

- Conecte cada línea de puerta a una fuente de tensión continua variable de pilas, la línea de origen a la incorporada en el ac fuente de tensión de un amplificador lock-in, y la línea de drenaje al puerto de entrada del amplificador lock-in.

- Mida la fuente al drenaje conductancia para diferentes configuraciones de voltaje de puerta (ver Figura 4).

- A nivel mundial la rampa encima de las tensiones aplicadas a puertas BL, BR, PL, SL y DL, manteniendo C1 y C2 puertas a tierra. Anote las características 'encendido' del dispositivo.

- Individualmente deceleración cada tensión de puerta y registrar las características de las puertas 'pinch-off'.

- Ajuste las tensiones de puerta para definir un electrostáticamente qudot Antum estableciendo las tensiones en BL y BR (PL, SL y DL) menor (mayor) que el encendido tensiones. Anote las características de bloqueo de Coulomb.

Resultados

La fabricación del dispositivo

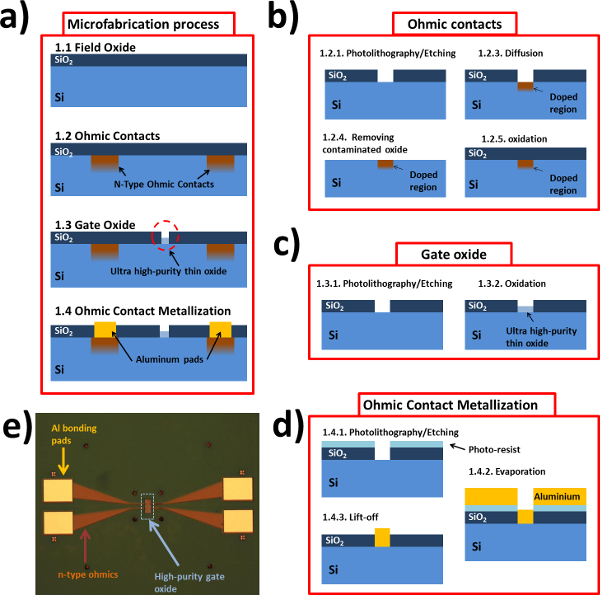

El proceso de microfabricación inicial (subsección 1 del Protocolo) se realiza en un comercial de 4 pulgadas de alta pureza oblea de silicio (de tipo n concentración dopaje ≈ 10 12 cm -3; resistividad> 10 kΩcm; espesor = 310-340 micras ). El objetivo es realizar el sustrato sobre el que se depositan los electrodos de puerta. Este sustrato está hecho de una región intrínseca tapado con óxido de campo (paso 1.1), un n + región tapado con óxido de campo (paso 1.2), una región intrínseca tapado con óxido de puerta de alta calidad (paso 1.3), y un metalizada n + región para contactos óhmicos (paso 1.4). Las Figuras 1A-D ilustran los principales pasos del proceso de microfabricación. La Figura 1E muestra una imagen microscópica de un campo de sustrato después de la microfabricación. La dimensión mínima de elemento para la litografía en esta etapa es de aproximadamente 4 micras.

El SiO2 capa de óxido crecido en el paso 1.1 tiene un espesor nominal de 100 nm y se utiliza como una capa de pasivación. Las regiones de tipo n que actúan como conductores óhmicos se obtienen a través de la difusión de fósforo. La densidad de dopaje de destino es de aproximadamente 10 19 hasta 10 20 cm -3. La alta calidad de SiO 2 que se cultiva de manera selectiva para ser utilizado como dieléctrico de puerta tiene un espesor nominal de 5 nm. La densidad de defectos interfaz objetivo <10 10 eV -1 cm -2 a mitad del hueco. Un horno de triple pared dedicado y construido a propósito se utiliza para este proceso. Este sistema está diseñado para minimizar la contaminación de iones de metales pesados e iones alcalinos móviles, así como evitar que la humedad se difunda en la cámara de oxidación. Con el fin de formar los contactos eléctricos, almohadillas de aluminio se depositan a través de la evaporación por haz de electrones en parte de las regiones de tipo n.

El proceso de nanofabricación (véase la subsección 2) se realiza en substr chipsates obtenidos por corte en dados la oblea procesada en el paso 1. El objetivo es hacer realidad los electrodos de puerta de nano escala se utilizan para definir los puntos cuánticos electrostáticamente MOS. Cada ejecución nanofabricación produce típicamente 10-15 muestras de dispositivos completos. Micrografía electrónica de barrido (SEM) de imágenes de 1-2 dispositivos por lote se lleva a cabo por lo general para confirmar que las etapas de litografía EBL han tenido éxito. Desde imágenes SEM puede inyectar cargas en el sustrato o en las puertas metálicas y causar fugas, sólo un pequeño número de dispositivos está marcada de esta manera, mientras que el resto se prueba eléctricamente. Tamaño mínimo para la función de la litografía en esta etapa es de aproximadamente 35 nm. Para lograr una buena uniformidad de las películas de Al depositada, el metal se evapora a tasas tan lenta como pocos angstrom / segundo, mientras que el sustrato está montado en un escenario giratorio. Esto se mantiene a RT, y el tamaño de grano de Al se estima que es de aproximadamente 20 nm. La Figura 2A ilustra las principales etapas de la nanofabricatioproceso n. La figura 2B muestra una imagen SEM con el que se verifica la correcta definición de los electrodos de puerta. En general, se apunta a la realización de esas puertas que definen directamente del QD (BL, BR y PL) con el tamaño de la característica más pequeña posible. Por el contrario, esas puertas que se utilizan para definir los embalses de electrones (DL y SL) pueden tener dimensiones mayores para evitar la discretización no intencional de los niveles de energía en los cables. Las nano-escala marcadores Ti / Pt realizadas en el paso 2.3 se utilizan como referencia para la alineación coherente de las tres capas de puertas. El platino es elegido por su excelente contraste con respecto a la superficie SiO 2 en la dirección de haz. El titanio se utiliza para mejorar la adhesión.

En todas las etapas del proceso de fabricación, pinzas de fibra de carbono de punta se utilizan para manejar las fichas, con el fin de reducir la probabilidad de una descarga electrostática destructiva (ESD).

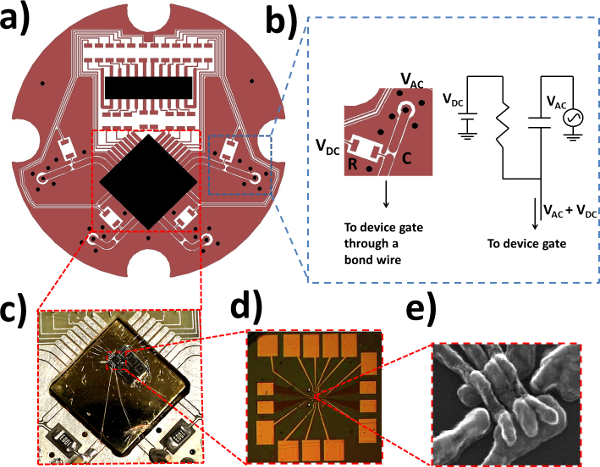

Por último, con el fin de realizar mediciones eléctricas en individispositivos duales, cada chip tiene que ser escindido en piezas más pequeñas de (sub-sección 3) alrededor de 2 x 2 mm 2. Cada pieza y luego se pega a un PCB o hechos a medida (Rogers R03010 baja pérdida dieléctrica) cuyos pines están conectados a los electrodos del dispositivo a través de Al cables. Unión de cables se lleva a cabo con una máquina de Bonder cuña sin calentar los chips. La elección de los parámetros de unión apropiados se basa en dos consideraciones. Por un lado, el enlace de alambre necesita para perforar el Al y O x capa térmica y hacer buen contacto de metal a metal con la almohadilla de puerta. Por otro lado, una tensión mecánica excesiva puede dar lugar a un evento de punzón de cubeta que daña el óxido de campo por debajo de la puerta y causa fugas de sustrato. Durante el proceso de cableado, el uso de una pulsera antiestática es aconsejable para evitar ESD. En la Figura 3, un chip con 6 dispositivos individuales se pega sobre la PCB.

Pruebas de integridad del dispositivo

Before la carga de un dispositivo en una plataforma de medición de temperatura mK como un refrigerador de dilución, pruebas eléctricas preliminares se realizan a 4.2 K para comprobar la integridad de la muestra (véase la subsección 4 del Protocolo). Para este fin, la PCB se inserta en un recinto de cobre libre de oxígeno y se monta en una sonda de inmersión, que se sumerge en Él eventualmente líquido.

La prueba inicial es típicamente una prueba de fugas que se realiza de forma secuencial en cada puerta. Una unidad de fuente-medida está conectado a un electrodo de puerta individual, mientras que los otros están conectados a tierra. El voltaje está en rampa hasta 1,5 V y la corriente se mide en la fuente. Dentro de este rango de tensión, una puerta funciona correctamente no se supone para llevar a cabo, porque la capa de SiO 2 aísla el metal del sustrato de silicio y Al y O x aísla puertas superpuestas. Por lo general, la ruptura de óxido se sabe que se produce para tensiones mayores que ~ 4 V, en función de la geometría del dispositivo y thic óxidoKness. Por lo tanto, si se detecta corriente durante la prueba, es probable que al menos una de las capas de óxido está dañado y el dispositivo tiene que ser descartado. Por lo general, menos del 10% de las puertas mostrar fugas. El rendimiento es conocido por estar afectada por la extensión plana de los electrodos de puerta. En particular, cuanto mayor sea el solapamiento de las puertas con la región de óxido de puerta más probable será tener fugas de puerta a sustrato. Del mismo modo, cuanto mayor sea el solapamiento entre las puertas de diferentes capas más probable la aparición de fugas de puerta a puerta será. El rendimiento indicado es relevante para las puertas que ocupan una superficie de unos 50 m 2 en el óxido fino y con capa intermedia se superpone de aproximadamente 0,5 m 2.

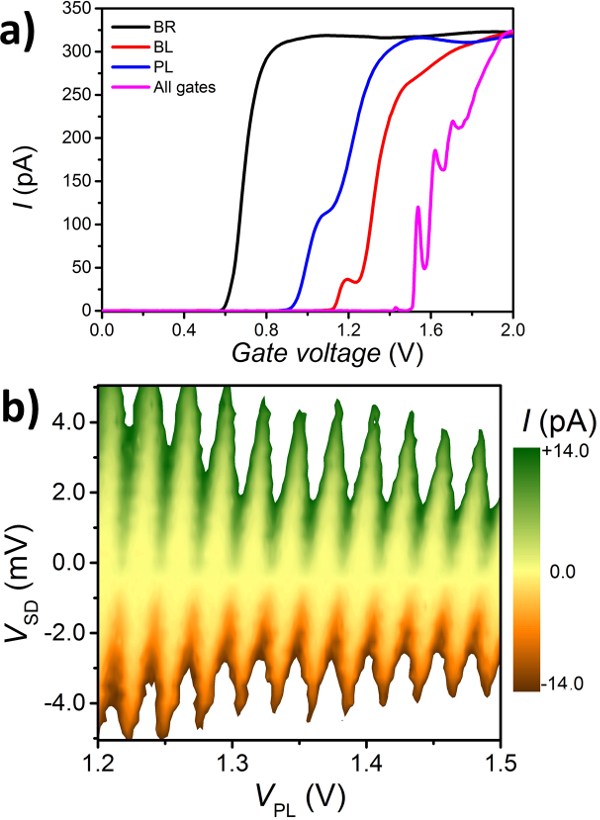

Una vez que el dispositivo ha pasado la prueba inicial de fuga, los contactos de fuente y drenaje están conectados a un amplificador lock-in y las puertas a un rack de baterías controlable tensión modular. En esta configuración, el dispositivo está encendido on por nivel mundial el aumento gradual de todas las tensiones de puerta al mismo tiempo. A continuación, cada voltaje de la puerta está separado rampa abajo, manteniendo los otros en altos voltajes para verificar la capacidad de las puertas individuales para evitar el paso de la corriente. Figura 4A muestra trazas representativas de estas mediciones. La ausencia de cualquiera de una conducción por vía fuente de la fuga o la puerta de estrangulamiento individuo es a menudo una indicación de algún tipo de daño puerta como puerta de explosión o discontinuidad de metal.

Finalmente, la corriente de fuente-drenaje se mide como una función de sesgo fuente-drenaje y voltaje de puerta émbolo para observar la firma de Coulomb bloqueo 16 (véase la Figura 4B).

Mediciones

Una vez se ha encontrado un dispositivo adecuado, se retira del recipiente Él líquido, y se secó con una pistola de aire caliente para evitar la formación de humedad que puede causar ESD. Finalmente, se transfiere a un refrigerador de dilución.

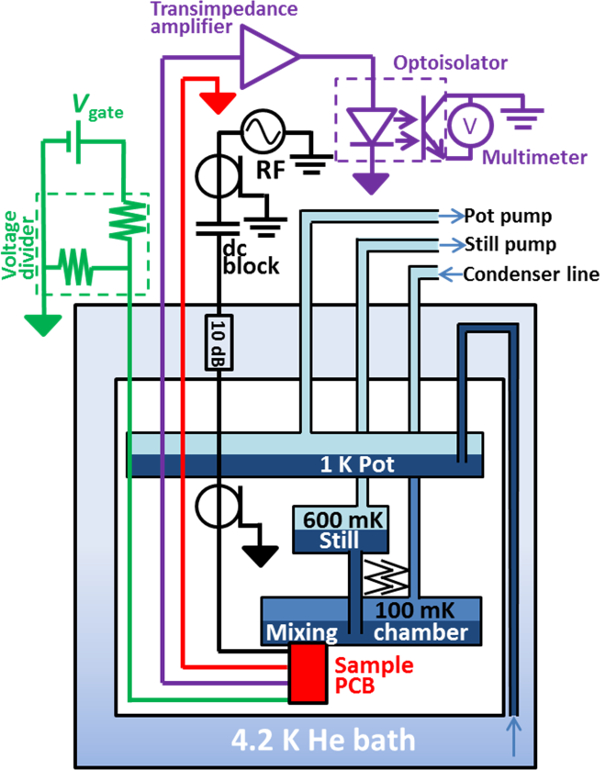

Los experimentos se realizan en una dilución de plástico refrigerador hecho a sí mismo con una temperatura base de alrededor de 100 mK. El criostato está en una cámara de vacío sumergido en un baño de 4,2 K helio. Las líneas eléctricas se termalizados en la olla 1 K que también se emplea para condensar el vapor de 3He entrante. En la cámara de mezclado, la transferencia de átomos de 3He endotérmico de la fase rica en 3He en la fase 3He-diluido permite que el sistema alcance una temperatura de base de alrededor de 100 mK.

Como se muestra en la Figura 5, la nevera está equipada con 20 líneas de corriente continua y 3 líneas de RF utilizados para conectar la electrónica de temperatura ambiente al dispositivo a baja temperatura. Cinco de las líneas de corriente continua son cables Thermocoax y 15 están retorcidos hilos del telar par. Estas líneas conectan los electrodos de puerta de la muestra a las fuentes de tensión de corriente continua que funcionan con baterías. Divisores de tensión a temperatura ambiente se utilizan para reducir el ruido eléctrico en las puertas individuales. Las líneas de RF son cables coaxiales que son semirrígidas atenuada por 10 dB a 4 K para reducir el ruido térmico y dc bloqueado a TA. Estas líneas están conectadas a las guías de onda coplanares de los tees de polarización en el PCB.

Un amplificador de transimpedancia de bajo ruido y un multímetro digital se utilizan para medir la corriente generada por la bomba. La electrónica está conectado al dispositivo a través optoaisladores de pilas para evitar la formación de bucles de tierra. Las señales de accionamiento de RF son producidos por un generador de forma de onda arbitraria cuya puesta a tierra está aislada de la del criostato a través de un componente de bloque dc (véase la Figura 5).

El PCB contiene 16 líneas de corriente continua puros y 4 líneas de polarización tee utilizados para combinar tensiones continuas y alternas a baja temperatura. Como se muestra en la Figura 3B, componentes discretos de RC se utilizan para realizar la conexión en T (R = 100 kW, C = 10 nF), y 50 Ω-emparejados guías de onda coplanares integrados se utilizan para la propagación de señales de alta frecuencia.

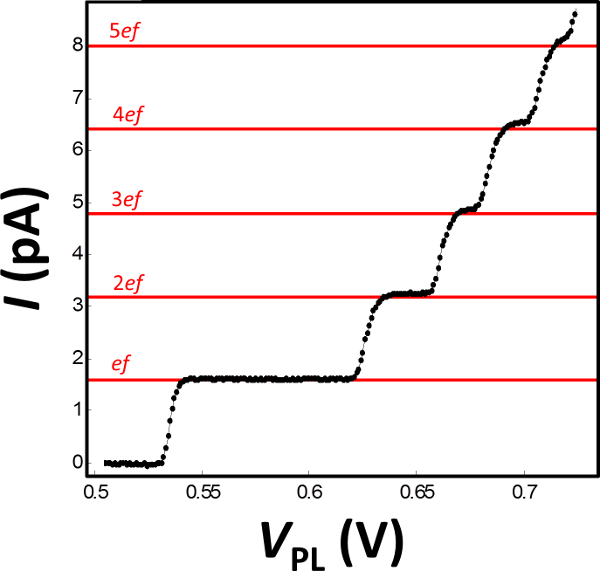

e_content "> Una vez que el dispositivo está a la temperatura mK, las tensiones de puerta se ajustan de modo que se alcanza la ocupación de un solo electrón en el QD. En particular, las barreras de túnel se forman bajo puertas BL y BR, y una capa de acumulación de electrones se induce bajo puertas PL, SL y DL. Con este fin, las tensiones de barrera de puerta se establecen a continuación, a su vez, en los valores, mientras que las puertas de acumulación están polarizados en una mayor a la tensión de encendido. De esta manera, una vez al día se forma bajo la puerta PL y su extensión planar es controlado a través de puertas C1 y C2 cuyos voltajes se mantienen por debajo de su giro en los valores para inducir confinamiento electrostático. A continuación, las señales de RF se enciende periódicamente para modular la transparencia de la barrera (s) de túnel, y la electroquímica potencial del punto. Single-bombeo de electrones se consigue, ya sea con uno o dos tensiones sinusoidales de conducción. En el caso de la unidad de una sola señal, la señal de excitación se aplica a BL puerta para modular el potencial de la barrera de túnel en el lado izquierdo -lado deel QD. En el caso de la unidad de dos señal, las excitaciones de corriente alterna se aplican a las puertas de BL y PL para modular los potenciales de tanto la barrera de la izquierda y el QD a la misma frecuencia pero con diferentes fases y amplitudes. Estos grados de libertad adicionales permiten una para controlar la dirección de la transferencia de electrones 13. Normalmente un proceso iterativo que se necesita para sintonizar los principales parámetros experimentales (es decir, las amplitudes de señal unidad rf / fases y tensiones de puerta dc) y lograr la cuantificación de corriente óptima. Tenga en cuenta que ninguno de los dos protocolos de bombeo necesita un sesgo de drenaje-fuente para realizar las transferencias de carga. Por lo tanto, los electrodos de fuente y drenaje están conectados a tierra durante el funcionamiento de la bomba. La Figura 6 muestra las mesetas actual característica a múltiplos enteros de ef obtenidos mediante la aplicación de una señal de accionamiento de dos sinusoidal a la barrera de entrada (BL) y el (PL) puerta émbolo. Estos datos se toman a una frecuencia de excitación relativamente baja (10 MHz) para el cual el t Sintonizar de los parámetros puede llevarse a cabo rápidamente. En la práctica, es deseable operar la bomba a varios cientos de MHz, normalmente requiere una optimización de parámetros mucho más fina 13.

Figura 1. microfabricación. (A) Representación esquemática de los principales pasos en la microfabricación. Dibujos animados no están dibujados a escala. (B) Realización de una región dopada para contactos óhmicos. (C) Realización de óxido de puerta. (D) metalización de contactos óhmicos. Se completa (E) microscópica imagen de un campo individual en un chip después del proceso de microfabricación. Tamaño del campo es de 1,2 x 1,2 mm 2. Haga clic aquí para ver una versión más grande de esta figura.

Figura 2. Nanofabricación. (A) Procedimiento de fabricación para las capas individuales de la puerta. Dibujos animados no están dibujados a escala. (B) La nanoestructura puerta 3 capas utilizado para experimentos de bombeo de carga. A la izquierda: imagen SEM de un dispositivo similar a la utilizada para las mediciones. Derecha:. Esquemáticos vistas en sección transversal del dispositivo a través de X e Y de corte de corte Haga clic aquí para ver una versión más grande de esta figura.

Figura 3. Conexiones eléctricas a la muestra. (A) Disposición de la placa de circuito impreso. (B) Ampliación de una región de la PCB con un sesgo-tee (izquierda) unad circuito equivalente (derecha). (C) Un chip con 6 campos individuales pegados en el soporte de chip y cables de bonos para la conexión eléctrica a la PCB. (D) Imagen microscópica de un campo individual después de nanofabricación. Imagen (E) SEM de la disposición de puerta en el centro de la región de óxido de puerta. Haga clic aquí para ver una versión más grande de esta figura.

Figura 4. Las pruebas preliminares. (A) actual Fuente fuga de corriente alterna (raíz cuadrada media) como una función de las diferentes tensiones de puerta. Las huellas se miden con un amplificador lock-in con 50 mV RMS excitación a 113,17 Hz. Para tensión de puerta individuo traza las tensiones de puerta restantes se fijan en 2,0 V, a excepción de V C1 = V C2 = 0,0 V. (B) mapa de color de corriente de fuente-drenaje como una función de émbolo voltaje de la puerta y la fuente de la fuga de polarización de tensión. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, V BR = 0,85 V, V = V C1 C2 = 0.0 V. Por favor haga clic aquí para ver una versión más grande de esta figura.

Líneas Figura 5. Esquema de la medición de puesta a punto. Veinte dc (verde) y tres líneas coaxiales RF (negro) conectan la electrónica RT a la PCB. El desagüe de la bomba (púrpura) está conectado a un amplificador de transimpedancia y a un multímetro digital a través de un optoaislador, mientras que el contacto de fuente (rojo) está conectado a tierra. Conexiones a tierra separadas (indicated con diferentes símbolos) se utilizan para la instrumentación electrónica y las líneas eléctricas de criostato. Haga clic aquí para ver una versión más grande de esta figura.

Figura 6. cuantización actual. Actual bombeado en función de V PL para dos señal de excitación sinusoidal a f = 10 MHz aplicada a puertas BL y PL. Diferencia de fase = 49 °, V = V PL RF RF BL = 0,31 V pp. La posición ideal de las mesetas de bombeo en múltiplos enteros de ef se muestran como líneas horizontales rojas. Por favor, haga clic aquí para ver una versión más grande de esta figura.

Discusión

El protocolo se informa en este documento se describen las técnicas para fabricar silicio MOS puntos cuánticos, así como los procedimientos experimentales para poner a prueba su integridad funcional y operar como bombas de un solo electrón. Sorprendentemente, mediante la adaptación de la puerta de diseño, el mismo proceso de fabricación se puede emplear para producir dispositivos adecuados para la lectura bit cuántico y control 17, así como la carga de bombeo 12,13. Tomamos nota de que muchos de los parámetros de proceso citados en este artículo pueden variar en función de las herramientas de fabricación utilizados (calibración, marca o modelo), así como del tipo de sustrato de silicio (espesor y densidad de fondo dopaje). Cantidades como dosis de exposición de litografía o el tiempo de desarrollo, el grabado o la duración de oxidación, tienen que ser cuidadosamente calibrado y probado para asegurar un rendimiento fiable. Además, es crucial para evitar la contaminación cruzada derivada de la utilización de las mismas herramientas de fabricación para diferentes procesos. Para este fin, un número de critical pasos se llevan a cabo con el equipo dedicado exclusivamente al procesamiento de silicio tales como evaporadores de metal, hornos de oxígeno y baños de HF.

Más en general, el silicio está atrayendo un creciente interés como el material de elección para darse cuenta de bombas de carga 18-20. Esto se debe en parte a la perspectiva atractiva de la implementación de un nuevo estándar de corriente eléctrica basados en cuántica utilizando un proceso de silicio compatible con la industria. Esto beneficiaría a partir de técnicas de integración bien establecidas y fiables para la escalabilidad, la paralelización y los gastos generales de conducción. Es importante destacar que una tecnología completa complementaria MOS (CMOS), libre de metales tradicionales como el material de la puerta, se ha mostrado muy reducidos fondo fluctuaciones de carga en los dispositivos de un solo electrón 21. Estas fluctuaciones pueden ser perjudiciales para lograr precisiones metrológicas.

El protocolo discutido aquí se limita a la realización de MOS nanodispositivos con puertas de metal. Por lo tanto, a Achieve compatibilidad industrial completa y reducir las fluctuaciones de carga, que sería necesaria para modificar las técnicas de deposición de puerta y utilizar silicio policristalino altamente dopado como el material de puerta.

En conclusión, las bombas MOS QD discutidos aquí han combinado recientemente la ventaja tecnológica de silicio con un rendimiento muy bueno en términos de generación de corriente precisa 13. Esto se debe a la alta flexibilidad del proceso de diseño y fabricación que permiten una para apilar múltiples capas de puertas que conducen a un sistema compacto y versátil. La capacidad de ajuste fino resultante del confinamiento electrostático del punto junto con el potencial de reducir las fluctuaciones de carga de fondo establece el escenario para superar los principales retos que se observan en otros semiconductores bombas 22,23.

Divulgaciones

Los autores no tienen nada que revelar.

Agradecimientos

Agradecemos KY Tan, P. Ver y GC Tettamanzi útil para los debates. Reconocemos el apoyo financiero del Consejo Australiano de Investigación (Grant No. DP120104710), la Academia de Finlandia (Grant No. 251748, 135794, 272806) y el apoyo del Fondo para Fabricación Nacional de Australia para la fabricación del dispositivo. AR reconoce el apoyo financiero del programa de subvenciones Investigador de la Universidad de Nueva Gales del Sur Carrera Temprana. También se reconoce la prestación de servicios y apoyo técnico de la Universidad Aalto en Micronova Nanofabricación Centro.

Materiales

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

Referencias

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930(2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).

Reimpresiones y Permisos

Solicitar permiso para reutilizar el texto o las figuras de este JoVE artículos

Solicitar permisoThis article has been published

Video Coming Soon

ACERCA DE JoVE

Copyright © 2025 MyJoVE Corporation. Todos los derechos reservados