Method Article

Кремний Металл-оксид-полупроводниковых квантовых точек для одного электрона Перекачивание

В этой статье

Резюме

The fabrication process and experimental characterization techniques relevant to single-electron pumps based on silicon metal-oxide-semiconductor quantum dots are discussed.

Аннотация

As mass-produced silicon transistors have reached the nano-scale, their behavior and performances are increasingly affected, and often deteriorated, by quantum mechanical effects such as tunneling through single dopants, scattering via interface defects, and discrete trap charge states. However, progress in silicon technology has shown that these phenomena can be harnessed and exploited for a new class of quantum-based electronics. Among others, multi-layer-gated silicon metal-oxide-semiconductor (MOS) technology can be used to control single charge or spin confined in electrostatically-defined quantum dots (QD). These QD-based devices are an excellent platform for quantum computing applications and, recently, it has been demonstrated that they can also be used as single-electron pumps, which are accurate sources of quantized current for metrological purposes. Here, we discuss in detail the fabrication protocol for silicon MOS QDs which is relevant to both quantum computing and quantum metrology applications. Moreover, we describe characterization methods to test the integrity of the devices after fabrication. Finally, we give a brief description of the measurement set-up used for charge pumping experiments and show representative results of electric current quantization.

Введение

Silicon is the material of choice for most of the modern microelectronics. Its properties, combined with advanced lithographic techniques, have allowed the semiconductor industry to achieve very large-scale integration and deliver billions of transistors per chip. The metal-oxide-semiconductor (MOS) technology1 has been the key of this relentless technological progress2. In brief, it is based on a selectively doped Si substrate which is thermally oxidized to grow a high quality SiO2 gate oxide on which a metal gate electrode is deposited. Recently, it has been shown that the use of a stack of gate oxides could be beneficial3 . While present industry standards have reached minimum feature sizes for gate lengths below 20 nm, it is becoming increasingly evident that, at this level of miniaturization, detrimental quantum mechanical phenomena come into play that may complicate further downscaling4.

Remarkably, silicon is also an excellent host material to exploit the quantum properties of the electron charge and spin5. This has broadened its range of applicability to entirely new fields such as quantum computing6 and quantum electrical metrology7. Among other approaches5, the use of a multi-gate MOS technology8,9 has led to electrostatically-defined quantum dots (QD) whose occupancy can be controlled down to single-electron level10. Unlike the conventional MOS process where just one gate per transistor is needed1, these QDs are defined via a three-layer stack of Al/AlyOx gates which are used to selectively accumulate electrons at the Si/SiO2 interface, as well as provide lateral and vertical confinement11.

Although these devices had been originally developed for quantum computing applications, they have also recently shown promising performances as metrological tools12,13. In the field of quantum electrical metrology, a long-standing goal is the redefinition of the unit ampere in terms of the elementary charge (e) 14. In particular, the emphasis is on the realization of nano-scale charge pumps to clock the transfer of individual electrons timely and accurately. These devices generate macroscopic quantized electric currents, I=nef, where f is the frequency of an external driving oscillator and n is an integer. To date, the best performance has been achieved with a GaAs-based pump by yielding a current in excess of 150 pA with a relative uncertainty of 1.2 parts per million15. Recently, silicon MOS QDs have also stood out for the implementation of highly accurate single-electron pumps thanks to the capability of finely tuning the charge confinement13.

Here, we discuss the protocol used for the fabrication of silicon MOS QDs. Furthermore, the cryogenic set-up used to test the integrity of the devices after fabrication and the one to perform charge pumping experiments are described. Finally, representative measurements of quantized electric current are reported.

протокол

Примечание: Этот протокол описывает процедуры, используемые для изготовления, упаковки и тестирования одноэлектронных насосов на основе кремниевой технологии МОП КТ. Шаги, описанные в подразделах 1 и 2 осуществляется в чистом помещении ISO5, в то время как в разделе 3 выполняются в ISO6 лабораторий. Окружающие условия постоянно контролируется. Номинальные значения температуры и влажности установлены на 20 ± 1 ° С и 55% ± 5%, соответственно.

1. микротехнологий

- Поле Оксид

- Очистите пластины погружением в следующем: пираньи травления (10 мин), деионизированной (DI) воды (10 мин), RCA-2 решение (DI воды 175 мл, 30 мл HCl, H 2 O 2 30 мл на 100 ° C в течение 10 мин), деионизированной воды (5 мин), плавиковой (HF) кислоты, разведенной в воде 10: 1 (10 сек), деионизированной воды (10 мин). Используйте защитную одежду при работе HF (например, защитные очки, фартук ПВХ и ПВХ перчатки). Перейдите в указанном порядке.

- Поместите пластинув окислительной печи при 900 ° С и окисляют с шагом следующим образом: сухой O 2 (10 мин), влажную O 2 (40 мин), сухой O 2 (10 мин), N2 (15 мин).

- Омические контакты

- Провести фотолитографии и травления оксида.

- Депозит нескольких нм толщиной слой промотора адгезии гексаметилдисилазана (HMDS) на поверхности пластины следующим образом: предварительно выпекать на плите при 110 ° С в течение 1 мин, залить ~ 50 мл гексаметилдисилазана в стеклянном стакане, Стакан помещают и вафельные в вакуумной камере, и ждать эвакуации в течение 2 мин.

- Спин 2-4 мкм толстый слой фоторезиста как на задней и передней сторонах пластины (3000-5000 оборотов в минуту, 25-40 секунд, в зависимости от желаемой толщины).

- Expose ультра-фиолетового света в маске выравнивателя (10 мВт / см 2 для 4-10 сек в соответствии с толщиной сопротивляться). Сообщение-печь на плите при 110 ° С в течение 1 мин.

- Разработка в течение 1-2 мин, затем промыть в деионизированной воде.

- Выполните O 2 плазменного травления в течение 20 мин (давление = 340; мторр падающая мощность = 50 Вт; отраженной мощности <1 Вт).

- Травление оксида в буферном растворе фтористоводородной кислоты (15: 1, 4-5 мин, травление цена услуг ≈ 20 нм / мин при 30 ° С). Промыть в деионизированной воде (5 мин). Удар сухой с N 2.

- Удалить фоторезиста путем погружения в ацетон. Промыть в изопропанола (IPA), то продуйте N 2.

- Поместите пластину в печи при температуре 1000 ° С с источником фосфора (N 2 потока для 30-45 мин в зависимости от желаемой плотности легирования).

- Удалить загрязненную оксидный слой с фтористоводородной кислоты, разведенной в воде (10: 1, 3-4 мин, травление цена услуг ≈ 40 нм / мин при 30 ° С), промыть в деионизированной воде (10 мин).

- Окислите, как в 1.1.2.

- Провести фотолитографии и травления оксида.

- Ворота оксид

- Повторите шаги 1.2.1 и 1.2.2.

- Поместите пластину в выделенном печи при 800 ° С и окисляют с шагом следующим образом: сухой O 2 (10 мин), Dichloroethylene + O 2 (20 мин), сухой O 2 (10-30 мин в зависимости от желаемой толщины оксидного), N 2 (15 мин).

- Омические контакты Металлизация

- Повторите шаг 1.2.1.

- Поместите пластину в электронно-лучевой испаритель. Выпарить 100 нм алюминия в 0,2-0,5 нм / сек и 5 х 10 -6 Торр.

- Замочите пластины в N-метил-2-пирролидон (NMP) на плитке при 80 ° С в течение 1 ч, чтобы оторваться от металла. Использовать ультразвуковой агитацию, если это необходимо. Промыть в МПА в течение 2 мин. Удар сухой с N 2.

- Отжиг в формировании газа при температуре 400 ° С в течение не менее 15 мин.

2. наноматериалов

- Вафли Dicing

- Спин-либо противостоять на пластину, чтобы действовать в качестве защитного покрытия (типа полимерных и прядильных параметров значения на данном этапе).

- Используйте алмазный наконечник Dicer сократить пластины на отдельные чипы ~ 10 х 2 мм 2.

- Уборка

- Замачивание в NMP в течение 1 часа на плите при 80 ° С, затем промыть в IPA в течение 2 мин. Удар сухой с N 2.

- Выполните O 2 плазменного травления в течение 5 мин (мощности падающего излучения 50 Вт; отраженной мощности <1 Вт).

- Спин чистый ацетоном и ИПС (7500 оборотов в минуту, 30 секунд)

- Выравнивание маркеры рисунка

- Спин полиметилметакрилат (ПММА 950k) A4 сопротивляться (5,000-7,500 оборотов в минуту, 30 секунд в зависимости от желаемой толщины). Рекомендуемая толщина рабочего ≈ 150-200 нм. Печь резиста на плите при 180 ° С в течение 90 сек.

- Провести электронно-лучевой литографии. Используйте следующие условия: записи энергии пучка = 30 кэВ, ток пучка ≈ 30 Па, площадь доза ≈ 500-650 мкКл / см 2 в зависимости от размера маркеров и противостоять толщины.

- Разработка резиста в растворе метилизобутилкетона и IPA (1: 3) в течение 40-60 сек, затем промыть в IPA в течение 20 сек. Удар сухой с N 2 пистолета.

- МестоЧип в электронно-лучевой испаритель. Выпаривают 15 нм Ti и 65 нм Pt на 0,2-0,4 нм / сек и 5 х 10 -6 Торр.

- Поднимите металл, как в шаге 1.4.3.

- Чистый чип, как в шагах 2.2.2-2.2.3.

- Ворота рисунка

- Спин сопротивляться, как и в 2.3.1.

- Провести электронно-лучевой литографии. Используйте следующие условия записи для функций с высоким разрешением: энергия пучка = 30 кэВ, ток пучка ≈ 30 Па, площадь доза ≈ 500-700 мкКл / см 2. Написать условия для функций с низким разрешением: энергия пучка = 15 кэВ, ток пучка ≈ 10 нА, зона доза ≈ 400-600 мкКл / см 2.

- Разработка сопротивляться, как и в 2.3.3.

- Поместите чип в термический испаритель. Выпарить Al в 0,1-0,4 нм / сек и 1-9 х 10 -6 мбар. Толщина мишени изменяется в зависимости от количества слоев, как показано на фиг.2В (25-35 нм для слоя 1, 45-65 нм для слоя 2, 75-90 лм для Layer 3).

- Поднимите металл, как в шаге 1.4.3.

- Выполнение Al окисление на плите при 150 ° С в течение 5-10 мин.

- Чистый чип, как в шаге 2.2.3.

- Повторите шаги 2.4.1-2.4.7 дважды реализовать стек ворота 3-слоя.

3. Устройство Упаковка

- Кости чип, как в шаге 2.1

- Промыть в результате меньшие стружки в ацетоне и IPA в течение 2 мин.

- Клей отдельной части к печатной плате (PCB) с ПММА A5. Подождите 2 минуты для того, чтобы высохнуть. Кроме того, для повышения термализацию, использовать серебро эпоксидную смолу.

- Загрузите плату на клин для скрепления и заполните проводки.

4. Устройство целостности тесты

- Установите печатную плату, содержащую проводного устройства на погружной зонд.

- Разводка электрических линий платы для тех, погружной зонд.

- Вставьте датчик в сосуд, содержащий жидкий гелий. Действуйте медленно, чтобы избежать чрезмерного гелия бмасло-офф.

- Для каждого устройства ворот, подключите соответствующий комнатной температуре электрода зонда в источник-единицу измерения, при сохранении других ворота обоснованные. Установите ток соответствия для нескольких нА. Развертки напряжения от нуля до 1,5 В с шагом 0,1 В, измерить и записать ток.

- Подключите каждый линию ворот с батарейным питанием источника переменного напряжения постоянного тока, источник линии встроенный источник переменного тока напряжением усилителя блокировки в, и дренажной линии к входному порту синхронного усилителя.

- Измерьте истока к стоку проводимость для различных конфигураций напряжения затвора (рис 4).

- В глобальном масштабе нарастить напряжение, применяемые к воротам BL, BR, PL, SL и DL, сохраняя C1 и C2 ворота заземлены. Запишите «под» на характеристики устройства.

- Индивидуально нарастить вниз каждый напряжения на затворе и регистрации характеристик Гейтса отсечки ".

- Отрегулируйте напряжение затвора для электростатического определить Куantum точка, установив напряжение на BL и BR (PL, SL и DL) меньше (больше), чем включении напряжения. Запишите кулоновской блокады характеристики.

Результаты

Изготовление устройства

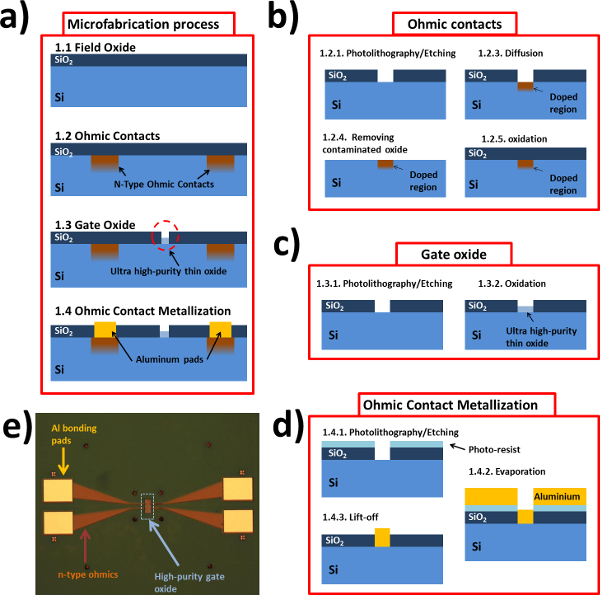

Начальный процесс микротехнологий (подраздел 1 Протокола) осуществляется на коммерческой 4-дюймовым высокой чистоты кремниевой пластины (н-типа легирующей концентрации ≈ 10 12 см -3; сопротивление> 10 kΩcm; толщина = 310-340 мкм ). Цель состоит в том, чтобы реализовать подложку, на которой затворные электроды будут депонированы. Этот субстрат изготовлен из внутренней области ограничен оксидом поля (шаг 1.1), п + регионе ограничен оксидом поля (шаг 1,2), в области собственной ограничен с высоким качеством оксида ворот (шаг 1.3), и металлизированная п + регион для омические контакты (шаг 1.4). 1А-D иллюстрируют основные этапы процесса микротехнологий. рис 1E показывает микроскопическое изображение в области подложки после микротехнологий. Минимальный размер функция для литографии на этой стадии составляет примерно 4 мкм.

SiO2 слой оксида выращивают на шаге 1.1 имеет номинальную толщину 100 нм, и используется в качестве пассивирующего слоя. Области н-типа, которые действуют как омические проводники получают с помощью диффузии фосфора. Плотность цель допинг примерно 10 19 - 10 20 см -3. Высококачественный SiO 2, который селективно выращивают для использования в качестве диэлектрика затвора имеет номинальную толщину 5 нм. Плотность дефектов целевой интерфейс <10 10 эВ -1 см -2 в середине зазора. Самоотверженные и намеренно построена тройная стена печи используется для этого процесса. Эта система предназначена для минимизации загрязнения от ионов тяжелых металлов и мобильных щелочных ионов, а также предотвратить попадание влаги диффундирующего в камеру окисления. Для того чтобы сформировать электрические контакты, алюминиевые прокладки осаждаются с помощью электронно-лучевым испарением на части областей п-типа.

Процесс Nanofabrication (см подраздел 2) выполняется на чипе подстрокаАтеш, полученные в кости пластины обрабатываются в шаге 1. Цель заключается в реализации нано-электроды затвора, используемые для электростатического определить МОП КТ. Каждый Nanofabrication выполнения, как правило, производит 10-15 полных образцов устройств. Сканирующего электронного микроскопа (СЭМ) визуализация 1-2 устройств на партию обычно проводят, чтобы подтвердить, что EBL этапы литографии были успешными. Так изображений СЭМ может вводить заряды в подложке или в металлических ворот и вызвать утечку, лишь небольшое количество устройств проверяется таким образом, в то время как остальная часть электрически испытания. Минимальный размер особенность для литографии на данном этапе составляет около 35 нм. Для достижения хорошей однородности осажденных пленок Al, металл испаряется со скоростью так медленно, как несколько ангстрем / с, в то время как подложка установлена на поворотном столике. Это выдерживают при комнатной температуре, а размер зерна Аль оценивается приблизительно 20 нм. 2А иллюстрирует основные этапы nanofabricatioп процесс. 2В показывает СЭМ-изображение с которой правильное определение электродов затвора проверяется. В общем, один направлен на реализацию тех ворота, которые непосредственно определяют QD (BL, BR и PL) с наименьшим возможным размером элемента. Напротив, эти ворота, используемые для определения электронных резервуары (DL и SL) может иметь большие размеры, чтобы избежать непреднамеренного дискретизации уровней энергии в отведениях. В нано-Ti / Pt маркеры, реализованные в шаге 2.3 используется в качестве ссылки для последовательного выравнивания трех слоев ворот. Платина выбран за его превосходной контрастностью по отношению к поверхности SiO 2 в электронным пучком. Титан используется для улучшения адгезии.

На всех этапах процесса производства, углеродного волокна наконечник пинцет используются для обработки чипов, для того, чтобы уменьшить вероятность деструктивного электростатического разряда (ESD).

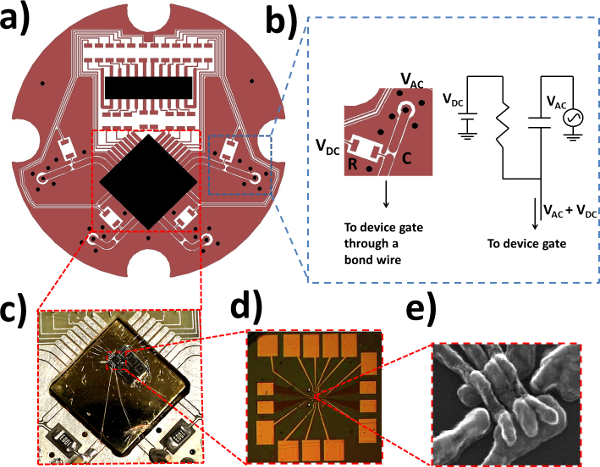

Наконец, для того, чтобы выполнить электрические измерения на INDIVIдвойные устройства, каждый чип должен быть расщеплен на более мелкие куски примерно 2 х 2 мм 2 (подраздел 3). Каждая часть приклеивается к заказ печатной платы (Роджерс R03010 низкой диэлектрических потерь), чьи выводы подключены к электродам устройства через Al проводов. Проводного соединения осуществляется с клином полуторный машины без нагрева стружки. Выбор соответствующих параметров связывания основано на двух соображений. С одной стороны, провод связи необходимо перфорировать тепловой Аль у O X слой и сделать хороший контакт металл-металл с ворот площадки. С другой стороны, чрезмерное механическое напряжение может привести к перфорации-корыто событие, которое повреждает оксида поле под ворота и вызывают подложки утечек. В процессе проводки, использование антистатического браслета Желательно, чтобы предотвратить ОУР. На рисунке 3, чип с 6 отдельных устройств приклеена на печатной плате.

Тесты целостности устройства

Beforе загрузке устройства в измерительной платформе мК температуры, такие как холодильник разведения, предварительные электрические испытания проводятся при температуре 4,2 К, чтобы проверить целостность образца (см подраздел 4 Протокола). С этой целью, печатная плата вставляется в корпус меди бескислородной и установлен на погружной зонд, который в конечном итоге, погруженной в жидкий He.

Начальное испытание обычно проверка герметичности, что выполняется последовательно на каждом ворот. Источник-мера устройство подключено к отдельному электроду затвора, а остальные заземлены. Напряжение повышают до 1,5 В и ток измеряется в источнике. В этом диапазоне напряжения, работает правильно ворота не должны проводить, потому что SiO 2 слой изолирует металл от кремниевой подложки и Аль у О х изолирует перекрывающихся ворота. Обычно пробой оксида, как известно, происходит при напряжении больше, чем ~ 4 V, в зависимости от геометрии устройства и оксида thickness. Таким образом, если ток обнаружен во время испытания, вполне вероятно, что по крайней мере один из слоев оксида поврежден, и устройство должно быть отброшено. Как правило, меньше, чем 10% из ворот показать утечек. Выход, как известно, зависит от плоской расширение электродов затвора. В частности, больше перекрытие ворот с оксидной области ворот скорее это будет иметь затвор-подложки утечки. Точно так же, больше перекрытие между воротами из разных слоев, скорее всего возникновение ворот до ворот-утечек будет. Цитирует выход актуальна для ворот, которые занимают площадь около 50 мкм 2 на тонкой оксида и прослойки перекрывает примерно 0,5 мкм 2.

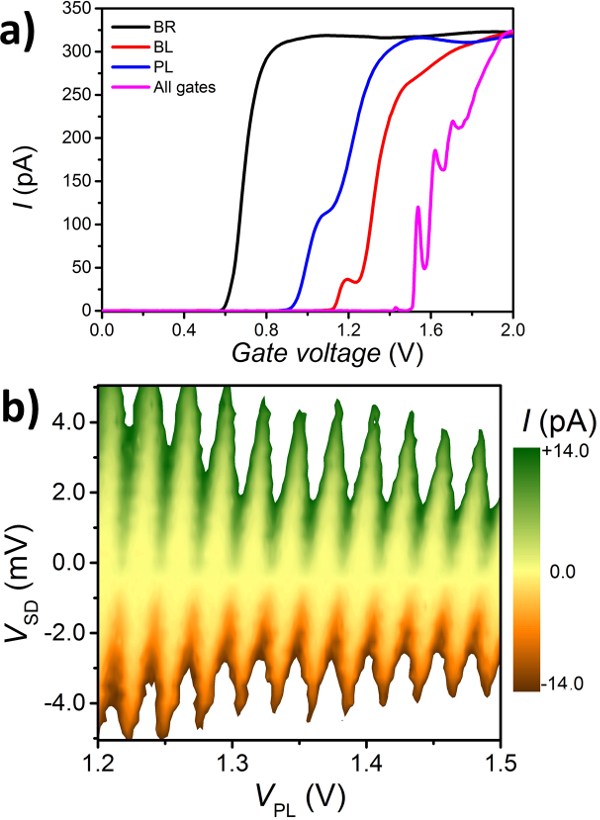

После того, как устройство прошло первоначальный тест утечки, истоком и стоком контакты подключены к замку-усилителем и ворот модульной регулируемого напряжения батареи стойки. В этой конфигурации, устройство включено оп глобально наращивает все напряжения затвора одновременно. Далее, каждый напряжение затвора отдельно по наклону вниз, сохраняя при этом другие при высоких напряжениях, чтобы проверить способность отдельных ворот отщипнуть тока. 4А показаны репрезентативные следы этих измерений. Отсутствие либо исток-сток пути проводимости или индивидуального ворота отсечки часто свидетельствует о некотором типе повреждения ворот, такие как взрыв ворота или металлическим разрыва.

Наконец, ток сток-исток измеряется как функция смещения источник-сток и напряжения поршень затвора, чтобы наблюдать подпись кулоновской блокады 16 (рис 4B).

Измерения

После подходящее устройство было обнаружено, он удаляется из жидкой судна он, и сушат с тепловой пушкой, чтобы избежать образования влаги, которая может вызвать ОУР. Наконец, он переносится на холодильником разбавления.

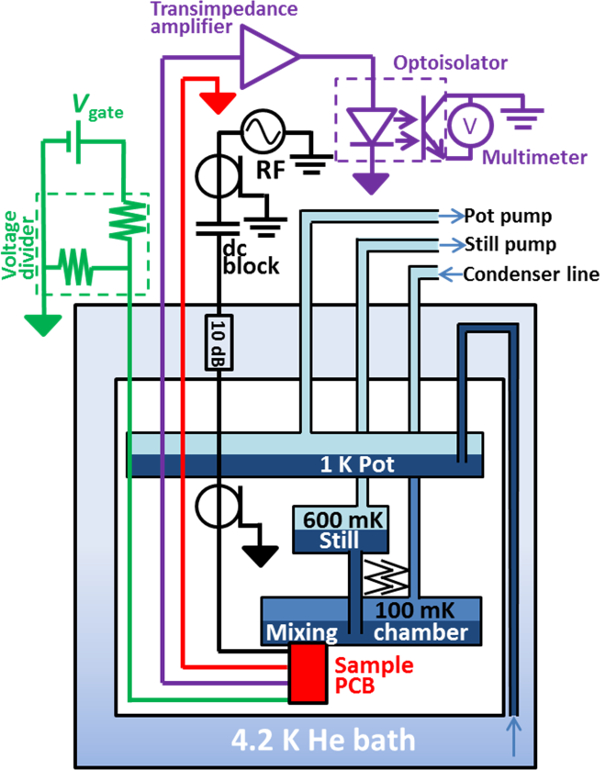

<р = класс "jove_content"> Эксперименты проводились в самодельной пластиковые разбавления холодильник с базовой температуре около 100 мК. Криостат в вакуумной камере, погруженной в 4,2 К гелия ванной. Электрические линии термализуются на 1 горшок K, который также используется для конденсации поступающего пара 3He. В смесительной камере, эндотермический передача атомов 3Не с 3Не-богатой фазы в фазе 3He-разбавленной позволяет системе достичь базовую температуру около 100 мК.Как показано на рисунке 5, холодильник оснащен 20 постоянного тока линий и 3 ВЧ линий, используемых для подключения комнатной температуры электроники в устройстве при низкой температуре. Пять из постоянного линий Thermocoax кабели и 15 витой паре проводов Loom. Эти линии соединяют электроды затвора образца к батарейным питанием источников напряжения постоянного тока. Делителей напряжения в РТ используются, чтобы уменьшить электрический шум на отдельных ворот. Радиочастотные линии полужесткие коаксиальные кабели, которые ослабляется на 10 дБ при 4 К, чтобы уменьшить тепловой шум и постоянного тока блокирован при комнатной температуре. Эти линии подключены к копланарных волноводов тройников смещения на печатной плате.

Усилитель трансимпедансным с низким уровнем шума и цифровой мультиметр используются для измерения тока, генерируемого с помощью насоса. Электроники соединен с устройством с помощью батарейным питанием Оптоизоляторы чтобы предотвратить образование контуров заземления. РФ синхронизирующие сигналы получают путем произвольного генератора импульсов заданной формы, чьи заземления изолирован от одного из криостата через компонент постоянного тока блока (рисунок 5).

PCB содержит 16 чисто постоянного тока линии и 4 смещения теэ линии, используемые для объединения постоянного и переменного напряжения при низкой температуре. Как показано на фигуре 3В, дискретные компоненты RC используются для создания соединения тройник (R = 100 кОм, C = 10 нФ) и 50 Ω соответствием интегрированных волноводов копланарных используются для распространения высокочастотных сигналов.

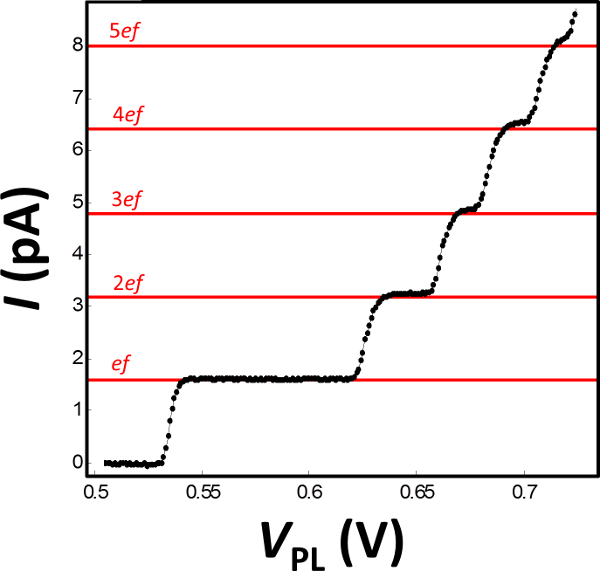

e_content "> После того, как устройство при температуре мК, напряжения ворота регулируют таким образом, что размещение одного электрона в КТ достигается. В частности, туннельные барьеры формируются под ворот BL и BR, и накопление электронный слой индуцируется под воротами PL, SL и DL. Для этого, напряжение барьер ворота устанавливаются ниже их включении ценностей, в то время как накопление ворота поляризованы в более, чем напряжение включения. Таким образом, КТ формируется под ворота PL и его плоской расширение контролируется с помощью вентилей C1 и C2, чьи напряжения поддерживают ниже их включении значений, чтобы вызвать электростатическое удержание. Затем радиочастотные сигналы включены периодически модулируют прозрачности туннельного барьера (ов), а электрохимический Потенциал точки. Одноэлектронное откачка либо с одной или двух синусоидальных напряжений вождения. В случае одного сигнала привода, управляющий сигнал подается на ворота BL модулировать потенциал туннельного барьера на левой руке -сторонаКТ. В случае привода двух сигналов, то переменного возбуждения подаются на затворы BL и PL, чтобы модулировать потенциалы как левого барьера и КТ на той же частоте, но с разными фазами и амплитудами. Эти дополнительные степени свободы позволяют контролировать направление переноса электрона 13. Повторяющийся процесс, как правило, необходимо, чтобы настроиться основные экспериментальные параметры (например, амплитуды ВЧ сигнала возбуждения / фаз и напряжения постоянного тока ворота) и достичь оптимального текущего квантования. Обратите внимание, что ни один из двух насосных протоколов необходим уклон сток-исток на выполнение переводов заряда. Следовательно, истока и стока электродов заземлен во время эксплуатации насоса. Рисунок 6 показывает вольт плато на кратных EF, полученных с применением двух сигналов синусоидальной диск на входной барьер (BL) и поршня (PL) ворот. Эти данные взяты при относительно низкой частоте возбуждения (10 МГц), для которых т uning параметров может быть выполнена быстро. На практике, желательно эксплуатировать насос в несколько сотен МГц, как правило, требует гораздо тоньше оптимизации параметров 13.

Рисунок 1. микротехнологий. () Схематическое изображение основных этапов микротехнологий. Мультфильмы не в масштабе. (Б) Реализация легированной области для омических контактов. (С) Реализация оксида затвора. (D), металлизация омических контактов. (Е) микроскопическое изображение в индивидуальной области на чипе после процесса микротехнологий завершена. Размер поля составляет 1,2 х 1,2 мм 2. Пожалуйста, нажмите здесь, чтобы посмотреть большую версию этой фигуры.

Рисунок 2. наноматериалов. () Процесс изготовления для отдельных слоев ворот. Мультфильмы не в масштабе. (B) затвора наноструктуры 3-слой используется для заряда насосных экспериментов. Слева: СЭМ изображение устройства подобного тому, который используется для измерений. Справа:. Схема поперечного сечения устройства через X-среза и Y-среза Пожалуйста, нажмите здесь, чтобы посмотреть большую версию этой фигуры.

Рисунок 3. Электрические соединения к образцу. () Макет печатной плате. (Б) Увеличение области печатной платы с уклоном-ти (слева)д эквивалентная схема (справа). (С) чип с 6 отдельных полей, склеенных на держателе кристалла и соединительными проводами для электрического соединения с печатной платой. (D) Микроскопический образ отдельного поля после нанофабрикации. (Е) СЭМ изображение макета ворот в центре региона оксида ворот. Пожалуйста, нажмите здесь, чтобы посмотреть большую версию этой фигуры.

Рисунок 4. Предварительные испытания. () Ток сток-исток переменного тока (среднеквадратичное) в зависимости от различных напряжениях на затворе. Следы измеряются с усилителем блокировки в 50 мкВ RMS на возбуждение 113,17 Гц. Для индивидуального напряжения на затворе следы оставшиеся напряжения ворота крепятся на 2,0 V, для V C1 = <исключениемEM> V С2 = 0,0 В. (В) Цвет карта тока исток-сток в зависимости от напряжения на затворе плунжера и исток-сток напряжения смещения. V SL = 1,5 V, V DL = 1,15 V, V BL = 0,78 V, В BR = 0,85 V, V = С1 С2 = V 0.0 В. Пожалуйста, нажмите здесь, чтобы посмотреть большую версию этой фигуры.

Рисунок 5. Схема измерения настройки. Двадцать постоянного тока линии (зеленые) и три коаксиальных радиочастотных линий (черный) подключить электронику RT на печатной плате. Сливной насоса (фиолетовый) подключен к усилителю трансимпедансного и цифровой мультиметр через оптрон, в то время как источник контакта (красный) заземлен. Отдельные соединения наземных (яndicated с разными символами), используется для электронной аппаратуры и электрических линий криостатных. Пожалуйста, нажмите здесь, чтобы посмотреть большую версию этой фигуры.

Рисунок 6. Текущий квантования. Перекачиваемая тока в зависимости от V PL в течение двух-сигнала синусоидальной диска на F = 10 МГц применяется к воротам BL и PL. Разность фаз = 49 °, V = PL РФ В РФ Б. = 0,31 V стр. Идеальная позиция насосной плато на кратных EF показаны красными горизонтальными линиями. Пожалуйста, нажмите здесь, чтобы посмотреть большую версию этой фигуры.

Обсуждение

Протокол сообщил в этой статье описываются методы для изготовления кремниевых МДП КТ, а также экспериментальные процедуры, чтобы проверить их функциональную целостность и управлять ими, как одноэлектронных насосов. Примечательно, пошив дизайн ворот, тот же процесс изготовления может быть использовано для получения подходящие для квантового бита считывания и контроля 17, а также заряд насосных 12,13. Отметим, что многие из параметров процесса, цитируемых в этой статье, может изменяться в зависимости от производственных инструментов, используемых (калибровка, марки или модели), а также от типа кремниевой подложке (толщина и фона легирующей примеси). Таких величин, как мощность экспозиционной дозы литографии или время разработки, травления или продолжительности окисления, должны быть тщательно продуманы и проверены, чтобы гарантировать надежную доходность. Кроме того, важно, чтобы избежать перекрестного загрязнения, возникающего в результате использования одних и тех же инструментов для изготовления различных процессов. С этой целью количество CRitical шаги осуществляются с оборудованием, посвященное исключительно обработки кремния, такие как металлические испарителей, печей и кислородных ванн ВЧ.

В целом, кремний рисунок растущий интерес в качестве материала выбора для реализации подкачки заряда 18-20. Это отчасти из-за привлекательной точки зрения реализации новой электрической стандарт современной квантовой основе с использованием отраслевой совместимы процесс кремния. Это было бы полезно устоявшихся и надежных методов интеграции для масштабируемости, распараллеливания и движущей накладных расходов. Важно отметить, что полный дополняют МОП (CMOS) технологии, без традиционного металла в качестве материала затвора, показал значительно снижается фоновые флуктуации заряда в одноэлектронных устройств 21. Такие колебания могут быть вредны для достижения точности метрологических.

Протокол обсуждается здесь ограничивается реализации МОП нано-устройств с металлическими воротами. Поэтому, чтобы achieве полный промышленный совместимость и уменьшить флуктуации заряда, то необходимо будет изменить методы осаждения ворота и используют весьма легированного поликристаллического кремния в качестве материала затвора.

В заключение, насосы МОП QD, обсуждаемые здесь недавно объединили технологические преимущества кремния с очень хорошей производительности в условиях точного текущего поколения 13. Это связано с высокой гибкостью дизайна и процесса изготовления, которые позволяют укладывать несколько слоев ворота, ведущие к компактным и универсальным системы. Полученный тонкий перестройки частоты электростатического удержания точку вместе с потенциалом для снижения фоновых флуктуации заряда устанавливает сцену, чтобы преодолеть основные проблемы, наблюдаемые в других полупроводниковых насосы 22,23.

Раскрытие информации

Авторы не имеют ничего раскрывать.

Благодарности

Мы благодарим KY Тан, П. увидеть и GC Теттаманци за полезные обсуждения. Мы признаем, финансовую поддержку от Исследовательского Совета (Australian грант № DP120104710), Академии Финляндии (грант № 251748, 135794, 272806) и поддержку со стороны Австралийского национального изготовлению фонда для изготовления устройства. АР признает финансовую поддержку от схемы научный Грант Университет Нового Южного Уэльса начале карьеры. Предоставление помещений и технической поддержки по Аалто университет в Micronova Nanofabrication центра также признал.

Материалы

| Name | Company | Catalog Number | Comments |

| Silicon wafers | TOPSIL | 4 inch | |

| Electron-beam lithography machine | Raith gmbh | Raith 150two | |

| E-beam resist | MicroChem gmbh | PMMA | |

| Photoresist | MicroChem gmbh | nLOF2020 | |

| Mask aligner | Quintel | Q6000 | |

| Photoresist developer | MicroChem gmbh | AZ826MIF |

Ссылки

- Sze, S. M. Physics of Semiconductor Devices. , Wiley. Interscience, NY. 505-566 (1969).

- Moore, G. E. Cramming More Components onto Integrated Circuits. Electronics. 38, 114-117 (1965).

- Voisin, B., et al. Few-Electron Edge-State Quantum Dots in a Silicon Nanowire Field-Effect Transistor. Nano Lett. 14 (4), 2094-2098 (2014).

- Asenov, A., Brown, A. R., Davies, J. H., Savas, K., Slavcheva, G. Simulation of Instrinsic Parameter Fluctuations in Decananometer and Nanometer-Scale MOSFETs. IEEE Trans Electron Devices. 50 (9), 1837-1852 (2003).

- Zwanenburg, F. A., et al. Silicon Quantum Electronics. Rev. Mod. Phys. 85 (3), 961-1019 (2013).

- Ladd, T. D., et al. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Piquemal, F. Genevès, G. for a direct realization of the quantum metrological triangle. Metrologia. 37 (3), 207-211 (2000).

- Angus, S. J., Ferguson, A. J., Dzurak, A. S., Clark, R. G. Gate-Defined Quantum Dots in Intrinsic Silicon. Nano Lett. 7 (7), 2051-2055 (2007).

- Gonzalez-Zalba, M. F., Heiss, D., Podd, G., Ferguson, A. J. Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire. Appl. Phys. Lett. 101 (10), 103504-103501 (2014).

- Lim, W. H., et al. Observation of the single-electron regime in a highly tunable silicon quantum dot. Appl. Phys. Lett. 95 (24), 242102-242103 (2009).

- Yang, C. H., et al. Spin-valley lifetimes in silicon quantum dots with tunable valley splitting. Nat. Commun. 4 (2069), (2013).

- Chan, K. W., et al. Single-electron shuttle based on a silicon quantum dot. Appl. Phys. Lett. 98 (21), 212103-212101 (2011).

- Rossi, A., et al. An accurate single-electron pump based on a highly tunable silicon quantum dot. Nano Lett. 14 (6), 3405-3411 (2014).

- Pekola, J. P., et al. Single-electron current sources: Toward a refined definition of the ampere. Rev. Mod. Phys. 85 (4), 1421-1472 (2013).

- Giblin, S. P., et al. Towards a quantum representation of the ampere using single electron pumps. Nat. Commun. 3, 930(2012).

- Kouwenhoven, L. P., Austing, D. G., Tarucha, S. Few-electron quantum dots. Rep. Prog. Phys. 64 (6), 701-736 (2001).

- Veldhorst, M., et al. An addressable quantum dot qubit with fault-tolerant control fidelity. Nat. Nanotech. 9 (12), 981-985 (2014).

- Fujiwara, A., Nishiguchi, K., Ono, Y. Nanoampere charge pump by single-electron ratchet using silicon nanowire metal-oxide-semiconductor field-effect transistor. Appl. Phys. Lett. 92 (4), 042102-1-042102-3 (2008).

- Jehl, X., et al. Hybrid Metal-Semiconductor Electron Pump for Quantum Metrology. Phys. Rev. X. 3 (2), 021012-1-021012-7 (2013).

- Tettamanzi, G. C., Wacquez, R., Rogge, S. Charge pumping through a single donor atom. New J. Phys. 16 (6), 063036-1-063036-17 (2014).

- Koppinen, P. J., Stewart, M. D., Zimmerman, N. M. Fabrication and Electrical Characterization of Fully CMOS-Compatible Si Single-Electron Devices. IEEE Trans Electron Devices. 60 (1), 78-83 (2013).

- Fletcher, J. D., et al. Stabilization of single-electron pumps by high magnetic fields. Phys. Rev. B. 86 (15), 155311-1-155311-6 (2012).

- Kataoka, M., et al. Tunable Nonadiabatic Excitation in a Single-Electron Quantum Dot. Phys. Rev. Lett. 106 (12), 126801-1-126801-4 (2011).

Перепечатки и разрешения

Запросить разрешение на использование текста или рисунков этого JoVE статьи

Запросить разрешениеСмотреть дополнительные статьи

This article has been published

Video Coming Soon

Авторские права © 2025 MyJoVE Corporation. Все права защищены