Method Article

﹙을 사용 하 여 이온을 트래핑에 대 한 실험 방법 표면 이온 트랩

요약

이 문서는 방 온도 환경에서 트랩이 터 븀 이온에 대 한 상세한 실험 절차로 서 표면 이온 트랩에 대 한 제작 방법론을 선물 한다.

초록

이온은 사중 극 자 폴 함정에에서 갇혀 있다 양자 정보 처리를 구현 하는 강한 물리적 후보 중 하나 간주 되었습니다. 이것은 그들의 긴 일관성 시간 및 그들의 기능을 조작 하 고 개별 양자 비트 (qubits)를 감지입니다. 더 최근 몇 년 동안, ﹙ 표면 이온 트랩 대규모 통합된 큐 비트 플랫폼에 대 한 더 많은 관심을 받았습니다. 이 문서에서는 마이크로 전자 기계 시스템 (MEMS) 기술을 사용 하 여 이온 트랩에 대 한 제작 방법론 설명, 14 µ m 두께 유 전체 층과 금속 제조 방법 등 구조 유 전체 층 위에 돌출. 또한,이 터 븀 (Yb)의 이온 동위 원소 174 (174Yb+) 369.5를 사용 하 여 트래핑에 대 한 실험 절차 nm, 399 nm, 935 nm 다이오드 레이저 설명 됩니다. 이러한 방법론 및 절차 참여 많은 과학 및 엔지니어링 분야, 그리고이 종이 먼저 자세한 실험 절차를 제공 합니다. 이 문서에서 설명한 메서드 동위 원소 171 (171Yb+)의 Yb 이온의 트래핑 및 qubits의 조작에 쉽게 확장할 수 있습니다.

서문

폴 트랩 입자, 정적 전기 필드와 라디오 주파수 (RF), 진동 하는 다양 한 전기 분야의 조합을 사용 하 여 빈 공간에 이온을 포함 한 제한 수 및 함정에 이온의 양자 상태를 측정할 수 있다 고 1,2,3제어. 이러한 이온 트랩 광 시계 및 질량 분광학4,,56을 포함 하 여 정확한 측정 어플리케이션에 대 한 원래 개발 되었다. 최근 몇 년 동안, 이러한 이온 함정 또한 적극적으로 탐험 되어으로 양자 정보 처리를 구현 하는 실제 플랫폼 일관성 시간 오래 같은 덫을 놓은 이온의 바람직한 특성에는 초고에 이상적인 절연 진공 (UHV) 환경, 그리고 개별 큐 비트 조작7,8,,910의 타당성. Kielpinski 외이후. 11 양자 컴퓨터, 표면 트랩, 접합 트랩12,13, 2 차원 배열, 다중 영역 트랩 칩14, 등의 다양 한 종류를 개발 하는 데 사용할 수 있는 확장 가능한 이온 트랩 아키텍처 제안 트랩15,,1617, 반도체 프로세스 파생 제작 방법18,19,20,21 사용 하 여 개발 되었습니다. . 대규모 양자 정보 처리 시스템은 표면에 따라 함정도 있다22,,2324논의.

이 종이 ﹙ 표면 이온 트랩을 사용 하 여 트래핑 이온에 대 한 실험 방법을 제공 합니다. 좀 더 구체적으로, 날조 표면 이온 트랩 및 트랩 이온 조작된 트랩을 사용 하 여에 대 한 자세한 절차에 대 한 프로시저를 설명 합니다. 또한, 실험 시스템을 설정 하 고 이온을 트래핑에 대 한 다양 한 실용적인 기술에 대 한 자세한 설명은 보충 문서에 제공 됩니다.

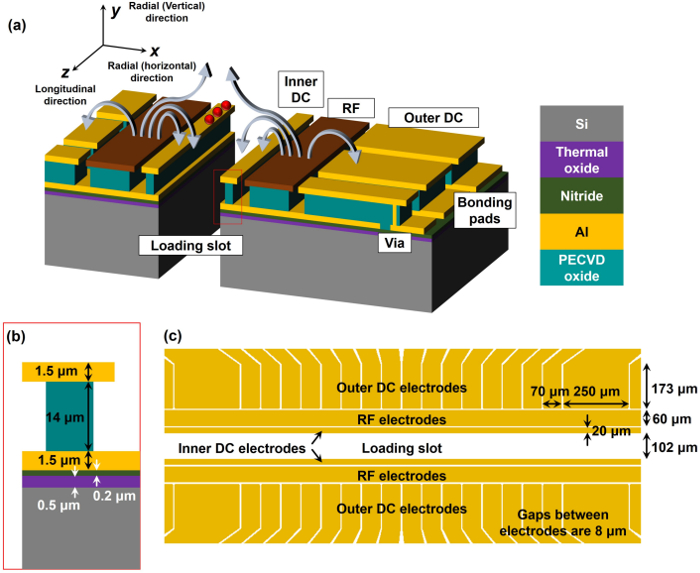

Microfabricating에 대 한 방법론 표면 이온 트랩 1 단계에서 제공 됩니다. 그림 1 표면 이온 트랩의 단순화 된 회로도 보여준다. 가로 평면에서 전극에 적용 된 전압에 의해 생성 된 전기 분야는25도 표시 됩니다. 동안 다른 모든 전극 RF 접지;에 RF 전압 RF 전극의 쌍에 적용 됩니다. ponderomotive 잠재적인26 RF 전압에 의해 생성 된 이온 반지름 방향 제한 합니다. 여러 DC 전극 RF 전극 외부에 적용 되는 직류 (DC) 전압 한정 경도 방향으로 이온. RF 전극 사이 내부 레일 가로 평면에서 총 잠재력의 주요한 도끼를 기울 수 있도록 설계 되었습니다. DC 전압 세트를 디자인 하기 위한 방법론은 보충 문서에 포함 됩니다. 또한, 표면 이온 트랩 칩의 필수적인 형상 매개 변수 설계에 대 한 자세한 내용은27,,2829,,3031에서 찾을 수 있습니다.

1 단계에서 도입 된 제조 방법은 다음과 같은 측면을 고려 하 고 설계 되었습니다. 첫째, 전극 층 및 지상 층 사이의 유 전체 레이어 레이어 간에 전기 분해를 방지 하기 위해 충분히 두꺼운 되어야 합니다. 일반적으로, 두께 10µm 이상 되어야 합니다. 두꺼운 유 전체 층의 증 착 동안 예금 된 영화에서 잔류 응력 기판 또는 손상 예금 된 영화에의 굴복을 발생할 수 있습니다. 따라서, 잔류 응력 제어 표면 이온 트랩의 제조에 핵심 기술 중 하나 이다. 둘째, 길 잃은 요금 흩어져 자외선 (UV) 레이저, 이온의 임의의 변화에 차례 결과에 위치 하 여 유 전체에 유도 될 수 있다 때문에 이온 위치로 유 전체 표면에의 노출을 최소화 한다. 오버행 전극 구조를 설계 하 여 노출된 영역을 줄일 수 있습니다. 그것은 그 일반적인 실험 조건32에서 충전 저항 전극 돌출부와 이온 함정을 표면으로 알려졌다. 셋째, 다양 한 예금 된 영화를 포함 하 여 모든 자료, 약 2 주 동안 제빵 200 ° C를 견딜 수 있어야 하 고 모든 자료에서 가스 방출의 양을 UHV 환경와 호환 되어야 합니다. 이 종이 표면 이온 트랩 칩 ﹙의 디자인은33, 다양 한 실험32,,3334, 에서 성공적으로 사용 되었다에서 트랩 디자인 기반 35.이 디자인에 가운데는 칩 슬롯 포함 나중은 중립 원자 로드 사진-이온 트랩에 대 한 참고.

이온 트랩 칩 제작 후 칩 탑재 하 고 전기 골드 본딩 와이어를 사용 하 여 칩 캐리어에 연결. 칩 캐리어 UHV 챔버에 설치 합니다. 트랩 칩 패키지 및 UHV 챔버의 설계를 준비 하기 위한 상세한 절차는 추가 문서에 제공 됩니다.

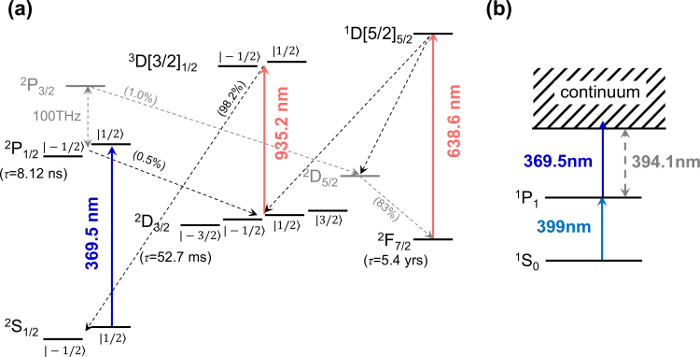

트래핑 이온에 대 한 광학 및 전기 장비, 실험 절차의 준비 단계 2에서에서 자세히 설명 합니다. 잠재적인 ponderomotive에 의해 갇혀 이온은 지속적으로 이온의 평균 운동 에너지 증가 주변의 전기장의 변동에 따라 일반적으로. 레이저 도플러 이동에 따라 냉각 이온의 움직임에서 과잉 에너지를 제거 하려면 사용할 수 있습니다. 그림 2 는 174Yb+ 이온 그리고 중립 174Yb 원자의 단순화 된 에너지 수준 다이어그램을 보여 줍니다. 174Yb+ 이온의 도플러 냉각 369.5 nm 레이저 및 935-nm 레이저 사진-중립 174Yb 원자의 이온화 399-nm 레이저를 필요로 하는 동안 필요 합니다. 2.2 및 2.3 단계 이러한 레이저 표면 이온 트랩 칩 및 사진-이온화에 대 한 적절 한 조건을 찾을 수 절차를 정렬 하는 효율적인 방법을 설명 합니다. 광학 및 전기 부품, 준비 후 이온을 트래핑 하는 것은 비교적 간단 합니다. 트래핑 이온에 대 한 실험 순서는 단계 2.4에서에서 제공 됩니다.

프로토콜

1. 이온 트랩 칩 패키지의 제작

- 표면 이온 트랩 칩의 제작.

참고:이 섹션에 설명 된 프로세스 조건 각 프로세스에 대 한 최적의 크게 다른 장비에 대 한 다를 수 있기 때문에 거친 참조만 제공 합니다. 온도 조건 산화 및 화학 기상 증 착 등의 높은 온도 프로세스에 대해서만 부여 됩니다. 제조 프로세스는 100 mm 직경 실리콘 웨이퍼를 사용 하 여 실시 됩니다.- 단일 결정 실리콘 500-525 µ m 두께 웨이퍼 및 15 분에 대 한 피 라 솔루션을 사용 하 여 그것을 청소 준비

- 열 양쪽 모두에 0.5 µ m 두께 SiO 2 유 전체 층을 형성 하는 보일 러 튜브에 실리콘 웨이퍼를 산화.

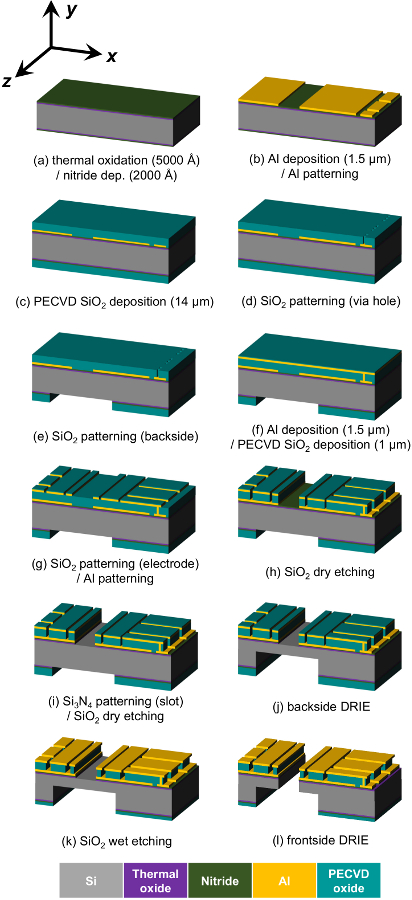

참고: 이러한 레이어 지상 계층에서 실리콘 기판을 분리 전기 수 있습니다. 습식 산화에 사용 되는 프로세스 매개 변수 했다: 6500 sccm, 5000 sccm의 N 2 유량, 7000 sccm의 H 2 유량의 O 2 유량 처리 900 ° C의 온도 및 시간 4.5 h (의 표 참조의 처리 재료 장비 세부 사항을 위해). - 입금 0.2 µ m 두께 Si 3 N 4 레이어 중 열 산화물 층을 보호 하기 위해 저압 화학 기상 증 착 (LPCVD) 과정 ( 그림 3a)를 사용 하 여 웨이퍼의 양쪽에는 습식 에칭 과정 에서처럼 그림 3 k.

참고: 프로세스 매개 변수 LPCVD 공정에 사용 되는: H 2 SiCl 2 유량 30 sccm, NH 3 유량 100 sccm의, 200 mTorr의 압력 및 프로세스 온도 785 ° c.의의 40의 증 착 속도에이 결과 Å / 분 (장비 세부 사항에 대 한 재료의 표 참조). - 스퍼터 링 과정 및 다음 매개 변수를 사용 하 여 웨이퍼에 1.5 µ m 두께 Al/Cu (1%) 층 보증금: 40 sccm, 2 mTorr의 압력 그리고 W. 300의 RF 전력의 아칸소 유량

참고:이 결과 130의 증 착 속도에 Å / 분 (장비 세부 사항에 대 한 재료의 표 참조).

참고:이 레이어 실리콘 기판을 통해 RF 손실을 방지 하기 위해 지 면을 제공 하 고 또한 와이어 본딩 패드에 대 한 접점을 제공 합니다. 1% 구리와 알루미늄 합금 UHV 환경을 달성 하기 위해 베이킹 과정 동안 수염 형성을 방지 하는 데 사용 됩니다. 이 구성 수염 예방을 위해 필수적 이다. - 웨이퍼에 2 µ m 두께 긍정적인 감광 레이어를 회전 하 고 있고 비행기와 와이어 본딩 패드를 차폐 하는 RF 정의 하 그것을 패턴.

참고: 2 µ m 두께 감광 제에 대 한 프로세스 매개 변수는: 5000 rpm의 속도 회전, 회전 시간 40 s, 전 빵 95 ° C의 온도, 90의 사전 빵 시간 s, 144 mJ/cm 2, 노출 에너지 개발 시간 60의 s, 110의 후 구워 온도 ° C, 그리고 5 분 후 빵 시간 (화학 및 장비 세부 사항에 대 한 재료의 표 참조). - 패턴은 1.5 µ m 두께 Al/Cu (1%)는 기존의 드라이 에칭 프로세스 (반응성 이온 에칭 (RIE) 또는 유도 결합된 플라즈마 (ICP) 에칭)를 사용 하 여 레이어, 포토 레지스트에 패턴을 에칭 마스크로 1.1.5 단계.

참고: ICP 에칭 다음 프로세스 매개 변수와 함께 사용 해야 합니다: 20 sccm, Cl 2 유량 30 sccm의, 5 mTorr의 압력 그리고 W. 750의 RF 전력의 BCl 3 유량 3600 Å/min의 etch 속도에서이 결과 (장비 세부 사항에 대 한 재료의 표 참조). - 단계 1.1.6 절차가 O 2 플라즈마 ashing 공정 ( 그림 3b)에 사용 되는 감광 제 제거.

참고: ashing 공정에 대 한 프로세스 매개 변수는: 150 sccm, 0.75 mTorr의 압력 및 RF 전력 300 W (장비 세부 사항에 대 한 재료의 표 참조)의 O 2 유량. - 플라즈마 강화 화학 증기 증 착 (PECVD) 프로세스 ( 그림 3c)를 사용 하 여 웨이퍼의 양쪽에서 14 µ m 두께 SiO 2 레이어 예금.

참고: 프로세스 매개 변수 PECVD 공정에 사용 되는: 540 sccm, 공정 온도가 350 ° C와 750 W.의 RF 전력 1.9 Torr의 압력의 SiH 4 유량 3000의 증 착 속도에이 결과 Å / 분 (장비 세부 사항에 대 한 재료의 표 참조). 14 µ m 두께 SiO 2 층 입금 이후 가장 어려운 프로세스 중 하나, 세부 토론에 설명 추가. - 웨이퍼의 전면에 6 µ m 두께 긍정적인 감광 레이어를 회전 하 고 있고 그것을 통해 구멍을 연결할 전기 DC 전극 와이어 본딩 패드를 정의 패턴.

참고: 6 µ m 두께 감광 제에 대 한 프로세스 매개 변수는: 5000 rpm의 속도 회전, 회전 시간 40 s, 전 빵 95 ° C의 온도, 5 분, 900 mJ/cm 2의 노출 에너지의 사전 빵 시간, 10 분의 시간을 개발, 후 110의 온도 구워 ° C, 그리고 5 분 후 빵 시간 (화학 및 장비 세부 사항에 대 한 재료의 표 참조). - 패턴 단계 에칭 마스크로 1.1.9 꽃무늬 감광 제와 함께 기존의 리에 프로세스를 사용 하 여 웨이퍼의 앞에 14 µ m 두께 SiO 2 층.

참고: SiO 2 에칭의 프로세스 매개 변수는: CHF 3 유량 25 sccm, 5 sccm의 CF 4 유량, 50 sccm의 Ar 유량, 130 mTorr의 압력 그리고 W. 600의 RF 전력의 3600 Å/min의 etch 속도에서이 결과 (장비 세부 사항에 대 한 재료의 표 참조). - 단계 1.1.10 O 2 플라즈마 ashing 공정에서에서 사용 되는 포토 레지스트를 제거 합니다. 웨이퍼가 열된 용으로 찍어 또는 ashing ( 그림 3) 하기 전에 그것을 sonicate.

- 웨이퍼의 뒷면에 6 µ m 두께 긍정적인 감광 레이어를 회전 하 고 있고 ( 3j 그림) 실리콘 기판의 깊은 반응성 이온 에칭 (DRIE)를 위한 산화 하드 마스크를 형성 하기 위하여 그것을 패턴.

- 패턴 14 µ m 두께 SiO 2 레이어는 감광 제와 함께 기존의 리에 프로세스를 사용 하 여 웨이퍼의 뒷면에 꽃무늬 단계 에칭 마스크로 1.1.12.

- 단계 1.1.13 O 2 플라즈마 ashing 공정 ( 그림 3e)와 함께에서 사용 하는 포토 레지스트 제거.

- 스퍼터 링 프로세스를 사용 하 여 전극으로 사용 되는 1.5 µ m 두께 Al/Cu (1%) 레이어 예금.

- PECVD 공정 ( 그림 3 층)을 사용 하 여 웨이퍼에 1 µ m 두께 SiO 2 레이어 예금.

- 웨이퍼에 2 µ m 두께 긍정적인 감광 레이어를 회전 하 고 있고 전극 정의 하 그것을 패턴.

- 패턴은 1.5 µ m 두께 Al/Cu (1%) 레이어 및 에칭 프로세스는 감광 제와 함께 기존의 ICP를 사용 하 여 1 µ m 두께 SiO 2 층 단계 에칭 마스크로 1.1.17 꽃무늬.

- 단계 1.1.18 O 2 플라즈마 ashing 공정 ( 그림 3 g)에서 사용 하는 포토 레지스트 제거.

- 웨이퍼에 6 µ m 두께 긍정적인 감광 레이어를 회전 하 고 있고 14 µ m 두께 산화물 기둥 패턴을 정의 하는 그것을 패턴.

- 패턴 14 µ m 두께 SiO 2 레이어는 감광 제와 함께 기존의 리에 프로세스를 사용 하 여 단계 에칭 마스크로 1.1.20 꽃무늬.

- 단계 1.1.21 O 2 플라즈마 ashing 공정 ( 그림 3 h)에서 사용 하는 포토 레지스트 제거.

- 웨이퍼에 6 µ m 두께 긍정적인 감광 레이어를 회전 하 고 있고 로드 슬롯 폭로 그것을 패턴.

- SiO 2 패턴 및 에칭 마스크로 1.1.23 단계에서 꽃무늬 감광 제와 함께 기존의 리에 사용 하 여 Si 3 N 4 레이어 처리.

- 단계 1.1.24 O 2 플라즈마 ashing 공정 ( 그림 3i)에서 사용 하는 포토 레지스트 제거.

- DRIE 공정 ( 그림 3j)를 사용 하 여 웨이퍼의 뒷면에서 실리콘 기판 패턴.

참고: 식 각 깊이 뒷면에서 실리콘 기판의 침투를 방지 하기 위해 반복적으로 측정 되어야 한다. 대상 에칭 깊이 약 450-470 µ m. DRIE 과정 5 C 4 F 8 증 착의 반복 수행 했다 s, C 4 F 8 엣지 3 s, 및 Si 5 엣지에 대 한 s. C 4 F 8 증 착 단계, C 4 F 8의 흐름 율에서에서 SF 6, 그리고 아칸소 했다 100, 0.5, 및 30 sccm, 각각. Note 아칸소는 C 4 F 8와 Si, etch 속도에 사용 하지만 C 4 F 8 증 착 단계 같은 흐름 속도, 압력 상태를 안정 시키기에 적용 됩니다. C 4 F 8에서 에칭 단계, 흐름 율은 각각 0.5, 50 및 30 sccm에 변경 되었습니다. Si에 에칭 단계, 유량 0.5, 100, 및 30 sccm의 각각, 사용 되었다. RF 전원 및 챔버 압력 825 W 모든 단계에서 23 mTorr로 설정 했다. 이러한 조건에 대 한 Si의 식 각 율은 각 루프에 대 한 1 µ m (장비 세부 사항에 대 한 재료의 표 참조). - Dicing 기계를 사용 하 여 10 m m x 10 m m 조각으로 웨이퍼를 주사위.

- 분리 5 분을 위한 아세톤에 그것을 찍기 하 여 다이에서 dicing 테이프 청소 이온된 (DI) 수 10 분, 2 분의 이소프로필 알코올 (IPA) 110에서 2 분 동안 그것 건조 실행에 그것을 찍기 하 여 다 ° c.

- 엣지는 산화 습식 에칭 과정 60을 사용 하 여 전극 돌출 구조를 조작 하는 산화물 기둥의 측 벽은 버퍼링 된 산화 현상 (비오이)에 s (NH 4 F:HF = 6:1) ( 그림 3 k). 10 분, 2 분에 대 한 IPA 110에서 2 분 동안 건조 디 물 실행에 그것을 찍기 하 여 다이 청소 ° c.

- DRIE 프로세스를 사용 하 여 다이의 앞에서 구멍을 로드 하는 슬릿 모양의 이온 침투.

참고: 이온 트랩 칩의 제조 공정은 ( 그림 3 l)이이 단계에서 완료.

2. 광학 및 전기 장비 및 이온을 트래핑의 준비

참고: 조작된 트랩 칩은 칩 캐리어와 함께 패키지와 칩 캐리어 UHV 챔버에 설치 됩니다. 광학 및 전기 장비를 설정 하 고 트래핑 이온에 대 한 자세한 내용은이 섹션에 설명 절차 날조 트랩-칩 패키지를 위한 및 UHV 챔버 준비에 대 한 보충 문서에 제공 됩니다, 하는 동안.

- 전기 연결의 준비.

- 해당 DC 제어 전극에 전압을 적용할 연결 UHV 챔버의 뒷면에 피드스루에 다중 채널 디지털-아날로그 컨버터 (DAC)

- .

- 뒷면에 피드스루에 오븐 핀에 전류 소스를 연결.

- RF 발생기와 헬리컬 공 진 기 사이의 방향성 커플러를 추가합니다. 방향성 커플러의 출력 포트에 RF 발생기 로부터 신호를 연결 합니다. 또한, 헬리컬 공 진 기의 입력된 포트에 방향성 커플러의 입력된 포트에 연결.

참고:이 구성 허용 36 헬리컬 공 진 기 반사 전력 모니터링. - 헬리컬 공 진 기 캡의 위치를 조정 하 고 스캔에서 반사는 최소 주파수를 찾을 발전기의 주파수. 세계 최소를 찾을 때까지이 단계를 반복.

참고: 글로벌 최소 주파수 공 진 주파수가 이다. 사용 추적 발생기와 스펙트럼 분석기의 옵션 또는 S 11 매개 변수는 네트워크 분석기의 측정 최소 반사에 대 한 스캔 과정을 단순화할 수 있습니다. 경우 DAC 전압 소스와 오븐에 대 한 전류 소스 전기 연결 변경 되, RF 피드스루의 임피던스 변경 되 고 공 진 주파수 이동 합니다. - RF 발생기 해제.

주의: 헬리컬 공 진 기는 함정을 높은 RF 전압을 적용, 하는 때에 임피던스 변화를 일으킬 수 있는 어떤 전기 연결 변경 하지 마십시오. 갑자기 임피던스 변화 쉽게 칩의 본딩 와이어를 구울 수 있습니다.

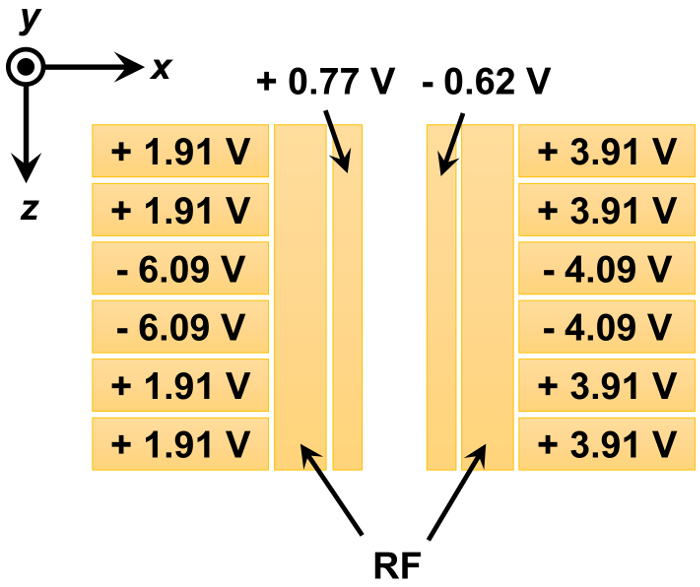

참고: 그림 4 트랩 칩에 적용 된 전압에의 한 예를 보여 줍니다. 같은 디자인에 대 한 자세한 방법 DC 전압 설정 보충 문서에 설명 되어. - 369.5 nm 레이저 및 이미징 시스템의 맞춤.

- 369.5 nm 레이저는 겨냥 틀을 사용 하 여 광섬유에서 당기기 고 칩의 높이에 광학 테이블의 표면에서 겨냥 틀의 높이 일치 하려고; 수평 전파 빔 확인. 그림 5에서 보듯이

- UHV 챔버의 왼쪽 또는 오른쪽 뷰포트를 통해 트랩 칩으로 조명을된 369.5 nm 광속의 전파 방향을 설정 합니다. 개의 레이저 빔 트랩 칩 표면에 평행 하 게 전파 하 고 거의 칩의 표면 접촉 되도록 정렬.

- 번역 단계에서 369.5 nm 레이저 초점 렌즈를 탑재. 레이저 칩 표면 위에 트랩 위치 주변 집중 될 것 이다 고 초점된 레이저 트랩 칩 표면을 따라 전파 전파 방향 따라 초점 렌즈를 배치 합니다. 번역 단계; 초점 렌즈의 위치를 조정 레이저 빔 초점의 위치 초점 렌즈의 움직임에 따라 합니다.

- 장소 높은 수 가늠 구멍 영상 렌즈 UHV 챔버 앞 번역 무대에 장착 된 칩 표면 ( 그림 5)에서 거리를 고려 하 고.

- 일부 양의 칩 표면에서 레이저 산란 되도록 트랩 칩 표면 369.5 nm 빔 정렬.

참고: 이미징 렌즈에 의해 수집 된 흩어진된 빛 렌즈의 이미지 평면 주위 희미 한 이미지를 형성 합니다. 이 이미지 일반적으로 관찰 될 수 있다, 심지어 종이로 형광 면 충분히 어두운 때. - 형광 종이에 이미지 날카로운 될 때까지 이미지 렌즈의 위치를 조정.

- 장소는 전자 곱한 충전 결합 장치 (EMCCD) 번역 단계에 장착 된 렌즈의 이미징 비행기의 위치를 고려 하 고 이전 단계에서 찾은.

- 증발에 대 한 오븐이 열 오븐에서 흑 체 방사선을 차단 하는 EMCCD 앞에 적외선 (IR) 필터를 탑재.

- 배경 빛을 차단 하는 EMCCD 앞 369.5 nm 대역 통과 필터를 탑재.

- 전극의 레이아웃은 EMCCD의 이미지를 비교합니다. 전극은 EMCCD와 함께 볼 수 있습니다 때까지 EMCCD와 이미지 렌즈의 위치를 조정 합니다. 때까지 흐려지므로 이미징 렌즈와는 EMCCD 정렬.

- 식별 어떤 전극은 EMCCD에 표시 되 고 예상된 트래핑 위치에 중심을 일치 하도록 EMCCD 정렬.

- 트랩 위치를 통과 한다 그래야 369.5 nm 빔 세로로 맞춥니다. 광선의 산란 최대화 될 때까지 이동 트랩 표면으로 빔을 광속의 센터와 트랩 표면 사이의 거리를 보세요.

참고: 단계 2.2.12, 그것 추측 될 수 있다 칩 표면에 바로 광속의 센터는. - 트랩 잠재적인 29의 수치 시뮬레이션, 칩 표면에서 이온 트랩 위치 예상된 높이 찾을. 칩 표면에서 369.5 nm 빔을 렌즈 번역 무대의 마이크로미터를 사용 하 여 예상된 높이 이동 합니다. 같은 거리에 의해 이미징 렌즈와는 EMCCD 다시 이동 합니다. 적어 이미징 렌즈와는 EMCCD의 마이크로 미터 판독.

- 는 399의 맞춤 및 935 nm 레이저 및 오븐 테스트

- 바꾸기 369.5 nm 대역 통과 필터링 399 nm 대역 통과 필터. 이미징 렌즈의 수치 시뮬레이션에서 399-nm 빛의 초점 거리와 369.5 nm 빛 색채 착오에서 결과 차이 찾아. 이미징 렌즈와 399-nm는 EMCCD에 초점을 EMCCD의 세로 위치를 조정.

- 당기기 935 399 nm 광선 각각 바꾸기와 광섬유에서 전달 하 고 섬유 지닌 두 빔 수평 전파 수 있도록 칩의 높이 맞게 높이 조정.

- 369.5 nm 레이저에서 반대 방향으로 전파 되 고 399 nm 레이저 같은 다른 뷰포트를 통해 함정 칩 표면으로 399 nm 광속을 맞춥니다. 조명을된 399 만들려고 초점된 369.5 nm 레이저와 nm 레이저 중복.

- Dichroic 거울을 사용 하 여 조명을 399 nm 레이저 조명을된 935 nm 광속을 결합 하 고 935 nm 레이저 공동 399-nm 레이저 전파 되도록 935 nm 빔 정렬. 얼마나 잘 두 광선 서로 겹치며 확인, 그들은 챔버를 입력 하 고 빔 프로파일러 또는 작은 구멍을 사용 하 여 빔 경로 따라 광선의 위치를 측정 하기 전에 임시 미러로 그 두 빔 전환. 공간이 챔버와 초점 렌즈 사이 임시 대칭 배치에 대 한 충분 하지 않으면 두도록 광학 설치 작은 광학 브레드보드;에 별도 장소에 중복 정도 확인할 수 있습니다.

- 추가 번역 무대에서 두 레이저 초점 렌즈를 탑재 하 고 dichroic 거울과 임시 미러 사이 초점 렌즈를 설정 합니다. 트래핑 위치에 임시 대칭에서 거리를 예측 하 고는 399 nm 레이저 트랩 위치 ( 그림 6b)에 초점을 맞추고 초점 렌즈의 위치를 조정.

- 399 nm 레이저의 초점 935 nm 레이저의 초점 일치 여부를 확인 합니다. 두 foci 오버랩 되지 않는 경우 잘게 935 nm 레이저 정렬.

- 399 nm 레이저 경로에서 임시 미러를 제거합니다. EMCCD를 사용 하 여 칩 표면에 399 nm 레이저의 추적을 확인 하십시오. 399 nm 레이저 광선의 흔적이 관찰 될 수 있다, 칩 주위 399 nm 빔 경로 이동 합니다. 또한, 약간 조정 실과 이미징 렌즈 사이의 거리의 칩 표면 이미지 날카로운 될 때까지.

- 예상된 트랩 위치를 통과할 것 이다 그런 칩 표면에 399 nm 광속의 추적을 맞춥니다. 마찬가지로 369.5 nm 빔 정렬, 이동 흩어져 빛의 강도까지 칩 표면으로 399-nm 빔 최대화 된다.

- 는 2.2.13는 마이크로미터를 사용 하 여 단계에서 사용한 동일한 높이 칩 표면에서 399 nm 레이저 빔을 이동 합니다. 같은 거리에 의해 이미징 렌즈와는 EMCCD를 다시 이동.

- 단계 2.3.4 다시에서 사용 하는 임시 거울을 넣어. 2.3.6 단계를 반복 하 고 다음 임시 미러 제거.

참고: 단계 후에 2.3.10, 935 nm 레이저 추측 될 수 있다 칩 표면 위에 트랩 위치를 통과 하. - 설정 1 S 0에 가까우면 399 nm 레이저의 파장-174 Yb (751,526 g h z)의 1 P 1 전환. 오븐으로 가득에 대 한 현재 설정 Yb를 자연스럽 게 발생 하 고 점차적으로 현재 증가.

참고: 일반적으로, 증발 잔류 가스 분석기 (RGA)에 의해 발견 보충 문서에 설명 된 대로 동일한 전류에서 반드시 시작 하지 않습니다, 그리고 그래서 증발 관찰 될 때까지 다른 현재 값을 사용해 보십시오. 만 때 중립 Yb 원자 증발 하기 시작 하 고 레이저의 주파수는 공명 1 S 0-1 P 1 전환 Yb 동위 원소 중 원자 흡수 하기 시작할 것 이다 중립 Yb 레이저 빛을 다시는 Yb에서 형광은 EMCCD와 함께 관찰 될 수 있다 그런 방출. 일반적으로, 파장 미터에 의해 측정 하는 공명 주파수는 공칭 값은, 수만 수백 MHz에서 이동 됩니다. 따라서, 현재 각 설정에 대 한 1 g h z의 span 범위와 단계 미만 50 MHz의 레이저 주파수를 스캔 좋습니다. - 자연적 오븐에서 공명 형광 관찰 되 면 전류를 낮출 수 형광 관찰 될 수 없을 때까지.

- 첫 번째 공명 주파수 주위 레이저를 검사 하 고 각 공명에서 형광의 양을 적어 둡니다. 형광 강도 및 37의 값으로 공명 사이 간격의 분포를 비교 합니다. 다른 동위 원소에 대 한 공명 주파수를 식별.

참고: 174 Yb의 공명 약 751.52646(2) THz 것 측정 되었다. 그러나,이 값은 약간 도플러 효과 의해 이동 하 고 측정 된 값은 파장 미터의 정확도 따라 달라질 수 있습니다.

- 이온을 트래핑.

- 369.5 nm 대역 통과 필터와 399 nm 대역 통과 필터를 장착 하 고 이미징 렌즈와는 EMCCD 369.5 nm 형광 갇힌된 이온에서 방출 되는 EMCCD에서 몇 군데 수 있도록 단계 2.2.13에서에서 얻은 위치로 다시 이동. 반복 단계 2.2.12 자외선 및 적외선 빔 오버랩의 시각적 검사에 대 한 카드 보기를 사용 하 여 한 번 더 모든 레이저의 맞춤을 확인 하십시오.

- 확인 DAC의 전압을다시 제대로 설정합니다. 매우 낮은 전원 설정에서 RF 발생기를 켜고 출력을 점차적으로 증가. 또한, 헬리컬 공 진 기에서 반사 전력 인지 확인 여전히 최소 주위 공명 RF 주파수를 스캔 하 여.

주의: 트랩 칩에서 증폭 된 전압은 전압을 초과 하지 않는 다는 것을 확인 하십시오. 대기압, SiO 2 영화의 유 전체 강도 약 10으로 알려져 7 V/cm, 하지만이 값 UHV 환경에서 추정 될 수 없습니다. UHV 환경에서 정확한 고장 전압 명시적으로 측정 되지 않습니다, 비록 8 µ m 측면 간격의 10 -11에서 칩-Torr 진공 견딜 실험적인 체제에 RF 전압 진폭의 240 V. - 는 174 Yb, 단계 2.3.13에서에서 확인의 공명 주파수에 399-nm 레이저의 주파수를 설정 합니다. 174 Yb + 동위 원소에 대 한 935-nm 레이저의 주파수 설정.

참고: 파장 미터 320.57199(1) THz 사용할 수 있습니다, 하지만 파장 미터의 한정 된 정확도 때문 거기 수 변형 최대 수십 MHz. - 설정 주파수 값을 100 ~ 200에 369.5 nm 레이저의 그래서 파장 미터 부정확의 일부 금액입니다 경우에 공 진 주파수 보다는 더 적은 MHz 주파수 있을 것입니다 아직도 레드 detuned.

참고: 여기, 200 MHz 튠에서 뺍니다 예상된 공명 174 Yb +의 예상된 공 진 주파수는 811.29152(1) THz 주위 때. - 오븐 하 고 증가 때까지 천천히 전류에 도달 단계 2.3.12에서에서 찾은 값에 대 한 현재 소스를 켭니다. 몇 분 동안 기다립니다. 없는 이온 갇혀 ~0.1-0.2 A에 의해 전류를 증가 하 고 다시 대기. 이온은 여전히 갇혀 하지, 반사 RF 여전히 최소에서 인지 확인 하 고 다음 점차적으로 RF 발생기의 출력 증가.

주의: 트랩 칩에서 증폭 된 전압 예상된 고장 전압을 초과 하지 않는 있는지 확인 하십시오. - 짧게 935 nm 레이저를 차단 하 고 이미지에 변경 사항이 있는지 여부를 확인.

참고: (를 포함 하 여 전자 멀티 (EM) 이득, 노출 시간, 및 이미지의 명암) EMCCD 설정 하지 않은 경우 적절 한 범위 내에서 이온 덫을 놓은 경우에 그것 쉽지 않다 말할 여부 트래핑 지역 주변 강도의 변화 진짜 갇힌된 이온 또는 변화 369.5 nm 레이저의 산란에 의해 발생 합니다. IR 필터 때문에 EMCCD 카메라 표시할 수 없습니다 어떤 변화 935 nm 레이저에 그래서 935 nm 레이저를 차단 만들지 않는다 변경한 이미지를 없는 덫을 놓은 이온이 있을 때. 그러나, 이온 덫을 놓은 경우 369.5 nm 레이저의 비 산 속도가 떨어지면 크게 935 nm 레이저 없이. 따라서, 935 nm 레이저를 차단 하 여 발생 하는 EMCCD 이미지에 변화는 이온 트랩의 성공의 좋은 지표.

주의: 너무 오래 935 nm 레이저 차단 되 면 덫을 놓은 이온이 열 되 면 고 함정을 피할 수 있습니다. - 해제 후 이온 갇혀 있다 오븐. 369.5 nm 레이저의 공 진 주파수를 점차적으로 증가 하 여 찾으려고.

참고: 주파수 공명에 가까이 면, 산란 율 증가 것입니다, 하지만 일단 공명 넘어 369.5 nm 레이저 시작 원인 차례로 그것에 냉각 불안정 덫을 놓은 이온의 이미지 보다는 이온을가 열 합니다. 369.5 nm 레이저의 공 진 주파수 발견 되 면 공명에서 10mhz 하 여 레이저의 주파수를 감소. - 369.5의 산란 율까지 935 nm 레이저의 주파수를 스캔 nm 최대화 가져옵니다.

- 이온의 이미지 선명 하 게 될 때까지 이미지 렌즈와 EMCCD 카메라의 위치를 조정.

결과

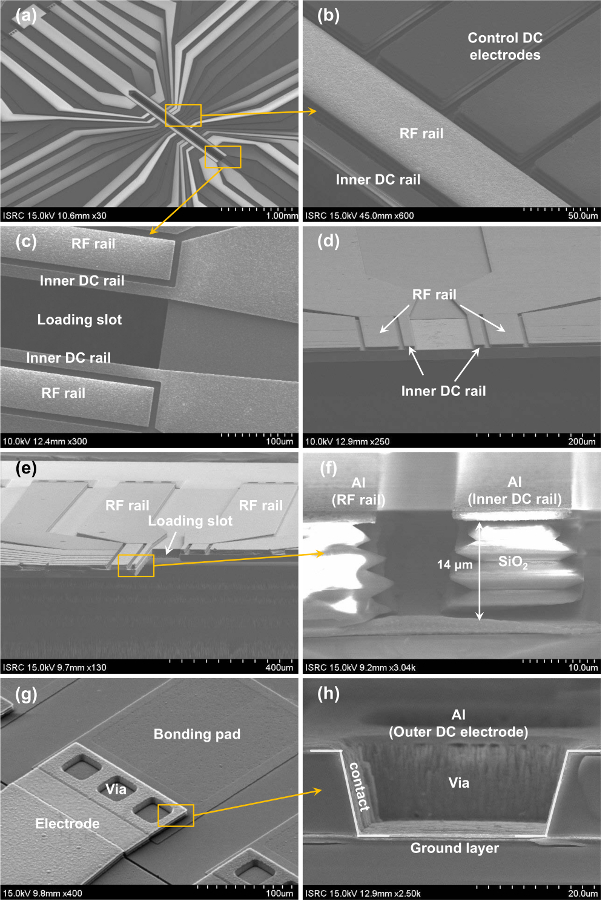

그림 7 조작된 이온 트랩 칩의 스캐닝 전자 현미경 (SEM)을 보여준다. RF 전극, 내부 DC 전극, 외부 DC 전극, 및 로딩 슬롯 성공적으로 조작 했다. 유 전체 기둥의 sidewall 프로필 PECVD 산화물은 여러 단계에서 예금 되었다 때문에 들쭉날쭉한 되었다. 여러 증 착 단계 두꺼운 산화물 필름에서 잔류 응력의 영향을 최소화 하기 위해 사용 되었다. 이 토론에 설명 추가 합니다.

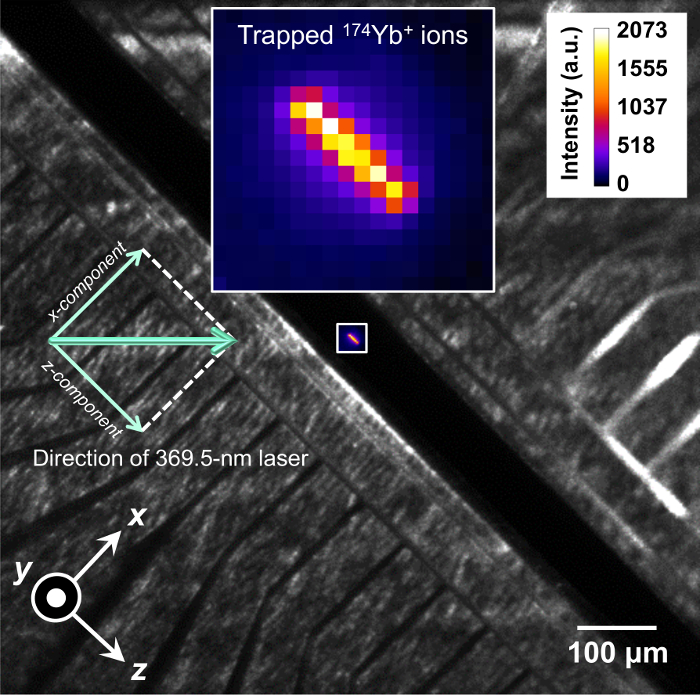

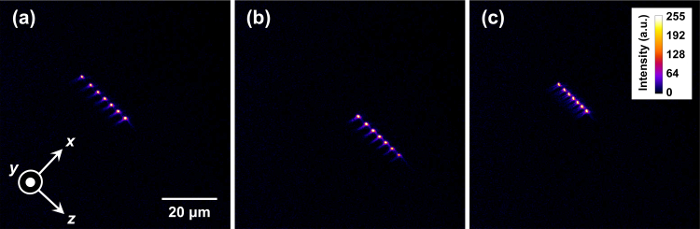

그림 8 ﹙ 이온 트랩 칩을 사용 하 여 갇혀 5 174Yb+ 이온의 EMCCD 이미지를 보여 줍니다. 덫을 놓은 이온 냉각 연속 도플러와 24 시간 이상 지난 수 있습니다. 덫을 놓은 이온 수 1과 20 사이의 적용된 DC 전압 설정 변경 하 여 조정할 수 있습니다. 이 실험적인 체제 매우 안정적이 고 강력한 이며 현재 50 개월 동안 운영 하고있다.

그림 9 축 방향 따라 갇힌된 이온 였죠 보여줍니다. 그림 9b 에서 이온 위치는 전치에서 그림 9a 에 DC 잠재적인 최소의 위치 조정을 통해 DC 전압을 변경 하 여.

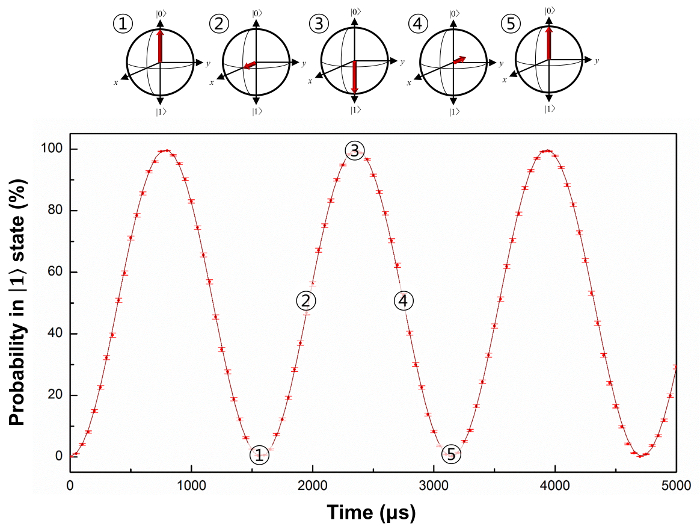

그림 10 은 171Yb+ 이온 Rabi 진동 실험의 예비 결과 보여줍니다. 결과 얻으려면 보충 문서 에서 설명 하는 추가 설정은 사용 했다. 결과이 문서에서 설명 하는 실험적인 체제의 잠재적인 응용 프로그램 표시를 포함 했다.

그림 1: 표면 이온 트랩의 도식. (한) 빨간 점 덫을 놓은 이온을 나타냅니다. 갈색과 노란색 전극 RF와 DC 전극, 각각 나타냅니다. 회색 화살표 RF 전압의 긍정적인 단계 중 전기 분야의 방향으로 표시합니다. 회로도 그릴 없는 참고 규모. (b) 수직 전극 구조의 치수. (c)는 옆 전극 구조의 치수. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 2: 174Yb+ 이온 그리고 중립 174Yb 원자의 에너지 레벨 다이어그램 단순화. (한) 경우는 369.5 nm 레이저 공명의 빨간 측면 (낮은 주파수)에 detuned, 자전거 전환 2P1/2 및 2S1/2 는 도플러 때문에 이온의 운동 에너지 감소 효과입니다. 때때로, 작지만 유한 분기 비율 2D3/2, 2P1/2 에서 전자 부패 하 게 하 고 935-nm 레이저 전자 주요 자전거 전환 다시 반환 하는 데 필요한. 전자 평균, 한 번 시간당, 2F7/2 상태로 부패 또한 수 638 nm 레이저 2F7/2 상태 펌프 수 있습니다 하지만이 간단한 시스템38에 대 한 필요 하지 않습니다. Ket 표기법의 값 양자화 축 mJ따라 총 각 결합체 J 의 계획을 나타냅니다. (b) 오븐, 2 광자 흡수 과정에서에서 증발 하는 중립 원자를 이온화 하는 사용된39. 399 nm 레이저 1P1 상태로 전자 흥분 그리고 도플러 냉각 369.5 nm 광자는 이온에서 흥분된 전자를 제거 하는 데 필요한 것 보다 더 많은 에너지를 했다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 3: 제조 프로세스 흐름 표면 이온 트랩의. 성장 하는 5000 Å 두께 SiO2 층 고 2000 Å 두께 Si3N4 계층의 LPCVD (는) 열 산화. 1.5 µ m 두께의 (b) 증 착 및 ICP 에칭 알 레이어 스퍼터 링. (c)는 14의 PECVD 프로세스를 사용 하 여 웨이퍼의 양쪽에서 µ m 두께 SiO2 층. (d) 리에 과정 (e)를 사용 하 여 웨이퍼의 앞에 14 µ m 두께 SiO2 층의 패턴 14 µ m 두께 SiO2 층의 패터 닝 리에 프로세스를 사용 하 여 웨이퍼의 뒷면에 입금. (f) 1.5의 µ m 두께 알 레이어 및 1 µ m 두께 PECVD SiO2 층을 스퍼터 링. (g)는 1.5 µ m 두께 알 ICP 과정을 사용 하 여 레이어와 리에 사용 하 여 1 µ m 두께 SiO2 층의 패터 닝 과정. (h) 14 µ m 두께 SiO2 층의 패터 닝 리에 프로세스를 사용 하 여 웨이퍼의 앞면에 입금. (나) 5000 Å 두께 SiO2 층과는 리에 사용 하 여 2000 Å 두께 Si3N4 레이어 패터 닝 과정. (j) 실리콘 기판 450의 DRIE는 웨이퍼의 뒷면에서 µ m. (k) 알 전극 및 유 전체 기둥의 측 벽에 SiO2 층의 습식 에칭. (l) DRIE 과정을 통해 앞에서 실리콘 기판의 침투. 설계도 그려집니다 하지 참고 규모. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 4: 이온 함정 사용 설정 하는 DC 전압의 예. 내부 레일에 적용 된 전압 가로 평면에서 총 잠재력의 주 축 기울기를 수평 방향으로 비대칭 전기 분야 보정할 수 있습니다. 전압 설정에 의해 생성 된 축방향 함정 주파수 550 kHz 이었다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

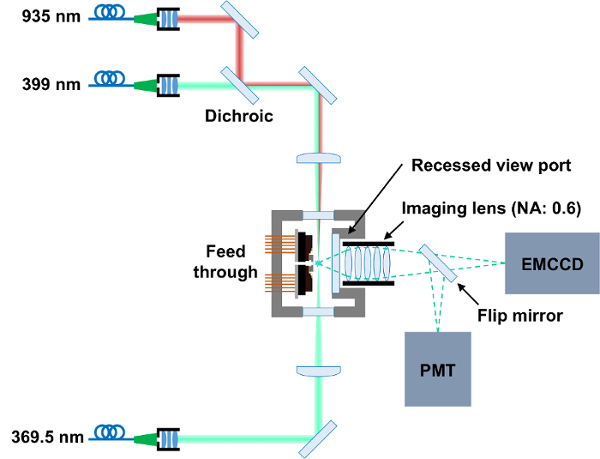

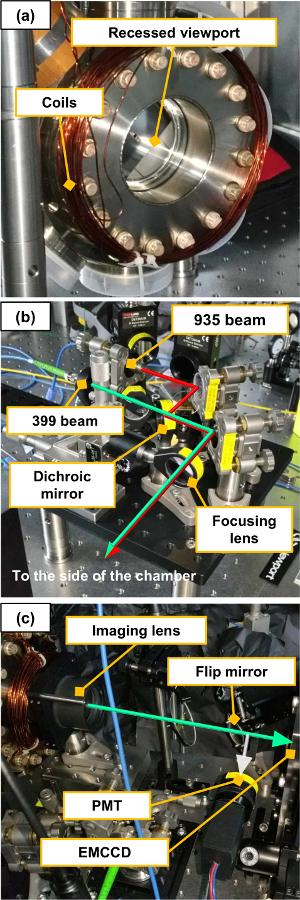

그림 5: 광학 설치의 도식. 3 개의 다이오드 레이저 트랩 위치에 겹치게 정렬 됩니다. UHV 챔버의 recessed 뷰포트 수 배치 이미징 렌즈 표면 칩에 최대한 가까이. 플립 미러 이미징 렌즈와는 EMCCD 사이 배치 곱한 광자 관 (PMT)를 사용 하 여 이온 형광의 선택적 모니터링에 대 한 허용 또는 EMCCD. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 6: 이미지 생성 된 광학 설치의. (한) A 코일이 터 븀 이온의 타락 한 에너지 레벨을 깰 수 있는 자기장을 생성 하는 챔버의 전면 뷰포트 주위 상처는. (b)는 399 조 타를 위한 광학 설치 및 935 nm 광속. 빨간색과 녹색 라인 표시는 935의 빔 경로 및 399 nm 레이저, 각각. 플립 미러, 이미징 렌즈, EMCCD, 그리고는 PMT.를 포함 하 여 (c)는 영상의 구성 시스템 플립-거울에 의해 덫을 놓은 이온에서 방출 하는 형광의 경로 확인할 수 있습니다. 녹색과 흰색 화살표는 각각 모니터링 하는 EMCCD 및 PMT 때 형광의 경로 나타냅니다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 7: 표면 이온 트랩의 제조 결과. (한) 칩 레이아웃의 개요. (b) 칩 레이아웃을 보여주는 여러 외부 DC 전극의 확대 보기. (c) 칩 레이아웃을 보여주는 로드 슬롯의 확대 보기. (d)는 횡단면 로드 슬롯을 관통 하기 전에 트래핑 지역 보기 (e)는 횡단면 로드 슬롯 관통 후 트래핑 지역 보기 (f) A의 산화물 기둥 단면 보기 확대. 산화물 기둥 벽, 가변 있다 그리고 오버행의 길이 충분 한는 별도로 입금된 3.5 µ m 두께 SiO2 레이어 사이의 인터페이스에 SiO2 의 비균일 etch 속도에 따라 결정 됩니다. (g) A의 DC 전극 와이어 본딩 패드의 최고 볼 수 있습니다. (h) A의 횡단면 뷰를 통해. 산화물 기둥의 경사 프로필 작성 대신 산화 기둥의 측 벽에 알 층의 증 착 하는 동안 DC 전극과 접지 층의 연결에 대 한 허용은 구멍을 전기 도금 프로세스를 통해. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 8: 5 174Yb+ 이온에의 한 EMCCD 이미지 ﹙ 이온 트랩 칩에 갇혀. 그리고 표면 트랩 전극 구조의 이미지, 별도로 찍은 덫을 놓은 이온의 고 전극의 이미지 선명도 위한 결합 했다. 강도 범례 상자에서 픽셀에만 적용 됩니다. 두꺼운 화살표 보여줍니다 369.5 nm 레이저의 빔 경로 및 얇은 화살표는 광자의 운동량 x 그리고 z 컴포넌트를 나타냅니다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 9: 선형 사슬에 갇힌된 이온의 축 잠재력의 조정. (한) 7 이온 트랩의 센터에서. (b) 이온 마이크로미터 shuttled 수만 했다. (c) 이온 문자열 축 방향으로 압착. 이 그림은 별도로 업로드 되는 동영상으로 잘 전망 된다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

그림 10: 사이 Rabi 진동의 실험 결과 | 0  및 | 1

및 | 1  상태. | 0

상태. | 0 2S1/2로 정의 됩니다 | F = 0, mF= 0

2S1/2로 정의 됩니다 | F = 0, mF= 0 171Yb+ 이온의 상태 및 | 1

171Yb+ 이온의 상태 및 | 1 2S1/2로 정의 됩니다 | F = 1, mF= 0

2S1/2로 정의 됩니다 | F = 1, mF= 0 상태. Rabi 진동 12.6428 g h z의 마이크로파에 의해 유도 된다. 작 위의 블로흐 분야는 서로 다른 시간에 해당 양자 상태를 보여줍니다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

상태. Rabi 진동 12.6428 g h z의 마이크로파에 의해 유도 된다. 작 위의 블로흐 분야는 서로 다른 시간에 해당 양자 상태를 보여줍니다. 이 그림의 더 큰 버전을 보려면 여기를 클릭 하십시오.

보조 문서: 이 문서를 다운로드 하려면 여기를 클릭 하십시오.

토론

이 문서는 트래핑 이온 ﹙ 표면 이온 트랩을 사용 하는 방법을 제시. 이온 트랩 시스템의 건설 다양 한 연구 분야에서 경험을 필요 하지만 이전 세부 사항에서 설명 하지 않는. 이 종이 microfabricating 처음으로 이온을 트래핑 하는 실험적인 체제 구축에 관해서는 뿐만 트랩 칩에 대 한 자세한 절차를 제공 합니다. 이 종이 또한 174Yb+ 이온을 트래핑 하 고 덫을 놓은 이온으로 실험에 대 한 자세한 절차를 제공 합니다.

제작 절차에 직면 하는 중요 한 장애물은 10 µ m의 두께 가진 유 전체 층의 증 착. 두꺼운 유 전체 층의 증 착 과정 중 잔류 응력 유 전체 필름에 손상을 일으킬 수 있는 하거나 심지어는 웨이퍼를 휴식, 구축할 수 있습니다. 일반적으로 압축은, 잔여 스트레스를 줄이기 위해 느린 증 착 속도 사용된40이어야 한다입니다. 우리의 경우 SiH4 가스 유량, 140 W의 RF 전원 및 1.9 Torr 압력에서 5 µ m 두께의 540 sccm의 증 착 조건 110.4 MPa의 압축 스트레스 측정 했다. 그러나, 이러한 프로세스 조건 이후 이러한 조건이 크게 다른 장비에 대 한 다를 수 있습니다만 거친 참조를 제공 합니다. 누적 된 스트레스의 영향을 줄이기 위해 3.5 µ m 두께 SiO2 영화 복선 제시 방법에 웨이퍼의 양쪽에 예금 되었다. 경우 작은 RF 전압 진폭 유 전체 층의 필요한 두께 줄일 수 있습니다 하 고 따라서 얕은 트랩 깊이 선택 됩니다. 그러나, 얕은 트랩 깊이 쉽게 리드 갇힌된 이온의도 주에 그래서 더 높은 RF 전압을 견딜 수 있는 두꺼운 유 전체 층의 제조 더 바람직합니다.

이 문서에 소개 된 제조 방법에는 몇 가지 제한이 있습니다. 그림 7 층에서처럼는 돌출부의 길이 완전히 갇힌된 이온에서 절연 측 벽을 숨기려고 충분 하지 않습니다. 또한, 산화물 기둥의 측 벽 들쭉날쭉한, 수직 산화물 기둥에 비해 절연 측 벽의 노출된 영역을 증가. 예를 들어 5 µ m의 균일 한 오버행 로드 슬롯 근처 내부 DC 레일의 측 벽의 경우 그것은 유 전체 표면의 33% 수직 측 벽의 덫을 놓은 이온 위치에 노출 되어 계산 됩니다. 들쭉날쭉한 가장자리 경우에서 측 벽 면적의 70% 이상 노출 됩니다. 이러한 비 이상적 제조 결과 노출된 유에서 추가 처진 분야를 일으킬 수 있지만 효과 양적 측정 하지는. 그럼에도 불구 하 고, 위의 보고 조작된 칩은 이온 트랩 및 큐 비트 조작 실험에 성공적으로 사용 되었습니다. 또한,이 문서에 소개 된 트랩 칩 로드 슬롯 근처 실리콘 측 벽을 노출 했다. 네이티브 산화 실리콘 표면에 성장할 수 있고 추가 처진 분야에서 발생할 수 있습니다. 따라서,33처럼도 색 되지 않은 금속 레이어 추가 실리콘 기판 보호 하는 것이 좋습니다.

174Yb+ 이온 함정, 몇 수십 MHz, 내 레이저의 주파수를 안정화 하 고 몇 가지 다른 방법에 대해서는 고급 설정38,41에서 설명. 그러나,이 문서에서 설명 하는 간단한 설치 프로그램에 대 한 초기 트래핑은 안정화 파장 미터를 사용 하 여 함께.

이 종이 174Yb+ 이온 ﹙ 표면 이온 트랩 칩을 사용 하 여 트랩 프로토콜을 제공 합니다. 171Yb+ 이온을 트래핑에 대 한 프로토콜은 구체적으로 설명 하지, 하지만이 문서에 설명 된 실험 설정 또한 사용할 수 있습니다 171Yb+ 이온을 트래핑 하 고 171의 큐 비트 상태를 조작 하 Yb+ 이온 결과 얻기 위해 Rabi 진동 ( 그림 10에 표시 된). 이 레이저의 출력에 여러 광학 변조기를 추가 하 여 및 보충 문서에 설명 된 대로 전자 레인지 설치를 사용 하 여 수행할 수 있습니다.

결론적으로, 실험 방법 및 결과이 문서에 소개 된 표면 이온 트랩을 사용 하 여 다양 한 양자 정보 응용 프로그램 개발에 사용할 수 있습니다.

공개

저자는 공개 없다.

감사의 말

이 연구는 과학, 정보 통신의 정부에 의해 부분적으로 지원 하 고 미래 계획 (MSIP), 한국 정보 기술 연구 센터 (ITRC)에서 지원 프로그램 (IITP-2017-2015-0-00385)와 ICT R & D 프로그램 (10043464, 개발의 정보에 대 한 연구소 주관 양자 중계기 기술 통신 시스템에 응용 프로그램에 대 한), & 통신 기술 진흥 (IITP).

자료

| Name | Company | Catalog Number | Comments |

| photoresist used for 2-μm spin coating | AZ Materials | AZ7220 | Discontinued. Easily replaced by other alternative photoresist product. |

| photoresist used for 6-μm spin coating | AZ Materials | AZ4620 | Discontinued. Easily replaced by other alternative photoresist product. |

| ceramic chip carrier | NTK | IPKX0F1-8180BA | |

| epoxy compound | Epotek | 353ND | |

| Plasma enhanced chemical vapor deposition (PECVD) system | Oxford Instruments | PlasmaPro System100 | |

| Low pressure chemical vapor deposition (LPCVD) system | Centrotherm | E-1200 | |

| Furnace | Seltron | SHF-150 | |

| Sputter | Muhan Vacuum | MHS-1500 | |

| Manual aligner | Karl-Suss | MA-6 | |

| Deep Si etcher | Plasma-Therm | SLR-770-10R-B | |

| Inductive coupled plasma (ICP) etcher | Oxford Instruments | PlasmaPro System100 Cobra | |

| Reactive ion etching (RIE) etcher | Applied Materials | P-5000 | |

| Boundary element method (BEM) software | CPO Ltd. | Charged Particle Optics | |

| Single crystaline (100) silicon wafer | STC | 4SWP02 | 100 mm / (100) / P-type / SSP / 525±25 μm |

| metal tubes | Mcmaster-carr | 89935K69 | 316 Stainless Steel Tubing, 0.042" OD, 0.004" Wall Thickness |

| Yb piece | Goodfellow | YB005110 | Ytterbium wire, purity 99.9% |

| enriched 171Yb | Oak Ridge National Laboratory | Yb-171 | https://www.isotopes.gov/catalog/product.php?element=Ytterbium |

| tantalum foil | The Nilaco Corporation | TI-453401 | 0.25x130x100mm 99.5% |

| Kapton-insulated copper wire | Accu-glass | 18AWG (silver plated copper wire kapton insulted) | |

| residual gas analyzer (RGA) | SRS | RGA200 | |

| turbo pump | Agilent | Twistorr84 FS | |

| all-metal valve | KJL | manual SS All-Metal Angle Valves (CF flanged) | |

| Leak detector (used as a rough pump) | Varian | PD03 | |

| ion gauges | Agilent | UHV-24p | |

| ion pump | Agilent | VacIon Plus 20 | |

| NEG pump | SAES Getters | CapaciTorr D400 | |

| spherical octagon | Kimball Physics | MCF600-SphOct-F2C8 | |

| ZIF socket | Tactic Electronics | P/N 100-4680-002A | |

| multi-pin feedthroughs | Accu-Glass | 6-100531 | |

| 25 D-sub gender adapters | Accu-Glass | 104101 | |

| Recessed viewport | Culham Centre for Fusion Energy | 100CF 316LN+20.9 Re-Entrant 316 (Custom order) | Disc material: 60cv Fused Silica 4mm THK, TWE Lambda 1/10, 20/10 Scratch-Dig |

| Recessed viewport AR coating | LaserOptik | AR355nm/0-6° HT370-650nm/0-36° on UHV (Custom order) | AR coating was performed in the middle of the fabrication of the recessed viewport |

| Digital-analog converter | AdLink | PCIe-6216V-GL | |

| 369.5nm laser | Toptica | TA-SHG Pro | |

| 369.5nm laser | Moglabs | ECD004 + 370LD10 + DLC102/HC | |

| 399nm laser | Toptica | DL 100 | |

| 935nm laser | Toptica | DL 100 | |

| 369.5nm & 399nm optical fiber | Coherent | NUV-320-K1 | Patch cables are connectorized by Costal Connections. |

| 935nm optical fiber | GouldFiber Optics | PSK-000626 | 50/50 fiber beam splitter made of Corning HI-780 single mode fiber to combine 935nm and 638nm together. |

| Wavelength meter | High Finesse | WSU-2 | |

| temporary mirror | Thorlabs | PF10-03-P01 | |

| Dichroic mirror | Semrock | FF647-SDi01-25x36 | |

| 369.5nm & 399nm collimator | Micro Laser Systems | FC5-UV-T/A | |

| 935nm collimator | Schäfter + Kirchhoff | 60FC-0-M8-10 | |

| 369.5nm focusing lens | CVI | PLCX-25.4-77.3-UV-355-399 | Focal length: ~163mm @ 369.5nm |

| 399nm & 935nm focusing lens | CVI | PLCX-25.4-64.4-UV-355-399 | Focal length: ~137mm @ 399nm, ~143mm @ 935nm |

| imaging lens | Photon Gear | P/N 15470 | |

| 369.5nm bandpass filter | Semrock | FF01-370/6-25 | |

| 399nm bandpass filter | Semrock | FF01-395/11-25 | |

| IR filter | Semrock | FF01-650/SP-25 | |

| EMCCD camera | Andor Technology | DU-897U-CS0-EXF | |

| PMT | Hamamatsu | H10682-210 |

참고문헌

- Wineland, D. J. Nobel Lecture: Superposition, entanglement, and raising Schrödinger's cat. Rev Mod Phys. 85 (3), 1103 (2013).

- Blatt, R., Wineland, D. Entangled states of trapped atomic ions. Nature. 453 (7198), 1008-1015 (2008).

- Leibfried, D., Blatt, R., Monroe, C., Wineland, D. Quantum dynamics of single trapped ions. Rev Mod Phys. 75 (1), 281 (2003).

- Paul, W. Electromagnetic traps for charged and neutral particles. Rev Mod Phys. 62 (3), 531 (1990).

- Rosenband, T., et al. Frequency ratio of Al+ and Hg+ single-ion optical clocks; metrology at the 17th decimal place. Science. 319 (5871), 1808-1812 (2008).

- Dawson, P. H. . Quadrupole mass spectrometry and its applications. , (2013).

- Ladd, T. D., Jelezko, F., Laflamme, R., Nakamura, Y., Monroe, C., O'Brien, J. L. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Monz, T., et al. Realization of a scalable Shor algorithm. Science. 351 (6277), 1068-1070 (2016).

- Debnath, S., Linke, N. M., Figgatt, C., Landsman, K. A., Wright, K., Monroe, C. Demonstration of a small programmable quantum computer with atomic qubits. Nature. 536 (7614), 63-66 (2016).

- Blatt, R., Roos, C. F. Quantum simulations with trapped ions. Nature Phys. 8 (4), 277-284 (2012).

- Kielpinski, D., Monroe, C., Wineland, D. J. Architecture for a large-scale ion-trap quantum computer. Nature. 417 (6890), 709-711 (2002).

- Moehring, D. L., et al. Design, fabrication and experimental demonstration of junction surface ion traps. New J Phys. 13 (7), 075018 (2011).

- Wright, K., et al. Reliable transport through a microfabricated X-junction surface-electrode ion trap. New J Phys. 15 (3), 033004 (2013).

- Amini, J. M., et al. Toward scalable ion traps for quantum information processing. New J Phys. 12 (3), 033031 (2010).

- Sterling, R. C., et al. Fabrication and operation of a two-dimensional ion-trap lattice on a high-voltage microchip. Nat Commun. 5, (2014).

- Kumph, M., et al. Operation of a planar-electrode ion-trap array with adjustable RF electrodes. New J Phys. 18 (2), 023047 (2016).

- Mielenz, M., et al. Arrays of individually controlled ions suitable for two-dimensional quantum simulations. Nat Commun. 7, (2016).

- Stick, D., Hensinger, W. K., Olmschenk, S., Madsen, M. J., Schwab, K., Monroe, C. Ion trap in a semiconductor chip. Nat Phys. 2 (1), 36-39 (2006).

- Harty, T. P., et al. High-fidelity preparation, gates, memory, and readout of a trapped-ion quantum bit. Phys Rev Lett. 113 (22), 220501 (2014).

- Cho, D., Hong, S., Lee, M., Kim, T. A review of silicon microfabricated ion traps for quantum information processing. Micro Nano Sys Lett. 3 (1), 1-12 (2015).

- Weidt, S., et al. Trapped-ion quantum logic with global radiation fields. Phys Rev Lett. 117 (22), 220501 (2016).

- Monroe, C., Kim, J. Scaling the ion trap quantum processor. Science. 339 (6124), 1164-1169 (2013).

- Brown, K. R., Kim, J., Monroe, C. Co-designing a scalable quantum computer with trapped atomic ions. npj Quantum Inf. 2, 16034 (2016).

- Lekitsch, B., et al. Blueprint for a microwave trapped-ion quantum computer. Science Adv. 3 (2), e1601540 (2017).

- Reichel, J., Vuletic, V. . Atom chips. , (2011).

- Ghosh, P. K., ed, ,. 1. s. t. . Ion Traps. , (1995).

- Wesenberg, J. H. Electrostatics of surface-electrode ion traps. Phys Rev A. 78 (6), 063410 (2008).

- House, M. G. Analytic model for electrostatic fields in surface-electrode ion traps. Phys Rev A. 78 (3), 033402 (2008).

- Hong, S., Lee, M., Cheon, H., Kim, T., Cho, D. I. Guidelines for Designing Surface Ion Traps Using the Boundary Element Method. Sensors. 16 (5), 616 (2016).

- Allcock, D. T. C., et al. Implementation of a symmetric surface-electrode ion trap with field compensation using a modulated Raman effect. New J Phys. 12 (5), 053026 (2010).

- Chiaverini, J., et al. Surface-electrode architecture for ion-trap quantum information processing. Quantum Inf Comput. 5 (6), 419-439 (2005).

- Allcock, D. T. C., et al. Heating rate and electrode charging measurements in a scalable, microfabricated, surface-electrode ion trap. Appl Phys B. 107 (4), 913-919 (2012).

- . Demonstration of a microfabricated surface electrode ion trap Available from: https://arxiv.org/abs/1008.0990 (2010)

- Allcock, D. T. C., et al. Reduction of heating rate in a microfabricated ion trap by pulsed-laser cleaning. New J Phys. 13 (12), 123023 (2011).

- Mount, E., et al. Single qubit manipulation in a microfabricated surface electrode ion trap. New J Phys. 15 (9), 093018 (2013).

- Siverns, J. D., Simkins, L. R., Weidt, S., Hensinger, W. K. On the application of radio frequency voltages to ion traps via helical resonators. Appl Phys B. 107 (4), 921-934 (2012).

- Kleinert, M., Dahl, M. E. G., Bergeson, S. Measurement of the Yb I 1S0−1P1 transition frequency at 399 nm using an optical frequency comb. Phys Rev A. 94 (5), 052511 (2016).

- Olmschenk, S., Younge, K. C., Moehring, D. L., Matsukevich, D. N., Maunz, P., Monroe, C. Manipulation and detection of a trapped Yb+ hyperfine qubit. Phys Rev A. 76 (5), 052314 (2007).

- Sansonetti, J. E., Martin, W. C., Young, S. L. . Handbook of Basic Atomic Spectroscopic Data. , (2013).

- Kern, W. . Thin film processes II. , (2012).

- Streed, E. W., Weinhold, T. J., Kielpinski, D. Frequency stabilization of an ultraviolet laser to ions in a discharge. Appl Phys Lett. 93 (7), 071103 (2008).

재인쇄 및 허가

JoVE'article의 텍스트 или 그림을 다시 사용하시려면 허가 살펴보기

허가 살펴보기더 많은 기사 탐색

This article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. 판권 소유