Method Article

Metodi sperimentali per intrappolare gli ioni utilizzando microfabbricati trappole ioniche in superficie

In questo articolo

Riepilogo

Questa carta presenta una metodologia di microfabbricazione per superficie trappole ioniche, nonché una dettagliata procedura sperimentale per gli ioni di itterbio di intrappolamento in un ambiente di temperatura.

Abstract

Gli ioni intrappolati in un quadripolo trappola Paul sono stati considerati uno dei candidati fisici forti per implementare l'elaborazione di informazione quantistica. Ciò è dovuto il loro tempo di coerenza lungo e la loro capacità di manipolare e rilevare bit quantistici individuali (qubit). In anni più recenti, microfabbricati superficie trappole ioniche hanno ricevuto maggiore attenzione per le piattaforme di qubit integrata su larga scala. Questa carta presenta una metodologia di microfabbricazione per trappole ioniche utilizzando la tecnologia di sistema micro-elettro-meccanici (MEMS), compreso il metodo di fabbricazione per un 14 µm di spessore strato dielettrico e metallo sporgenza strutture in cima lo strato dielettrico. In aggiunta, una procedura sperimentale per intrappolare ioni di itterbio (Yb) dell'isotopo 174 (174Yb+) utilizzando 369,5 nm, 399 nm, e 935 nm diodo laser è descritto. Queste metodologie e procedure coinvolgono molte discipline scientifiche e ingegneristiche, e questa carta presenta in primo luogo le procedure sperimentali. I metodi descritti in questa carta possono essere facilmente esteso per l'intrappolamento di ioni Yb dell'isotopo 171 (171Yb+) e per la manipolazione di qubits.

Introduzione

Una trappola di Paul può confinare le particelle cariche, tra cui gli ioni nello spazio vuoto, usando una combinazione di un campo elettrico statico e un campo elettrico variabile oscillante a radio frequenza (RF), e gli stati quantistici degli ioni confinati nella trappola può essere misurati e controllato1,2,3. Tali trappole ioniche sono stati originariamente sviluppati per applicazioni di misura precisi, tra cui orologi ottici e spettroscopia di massa4,5,6. Negli ultimi anni, queste trappole ioniche sono anche stati attivamente Esplorate come una piattaforma fisica per implementare l'elaborazione dell'informazione quantistica attribuita alle caratteristiche desiderabili di ioni intrappolati, come lunghi tempi di coerenza, isolamento ideale in un ultra-alta ambiente di vuoto (UHV) e la fattibilità di singolo qubit manipolazione7,8,9,10. Dal Kielpinski et al. 11 proposto un'architettura scalabile trappola ionica che può essere utilizzata per sviluppare i computer quantistici, vari tipi di trappole di superficie, tra cui svincolo trappole12,13, multizona trappola chip14e 2-d matrice trappole15,16,17, sono stati sviluppati utilizzando semiconduttori derivato dal processo di microfabbricazione metodi18,19,20,21 . Informazione quantistica su larga scala sistemi basati sulla superficie di elaborazione trappole sono stati anche discussi22,23,24.

Questa carta presenta metodi sperimentali per gli ioni di cattura mediante trappole ioniche superficie microfabbricati. Più specificamente, una procedura per fabbricare superficie trappole ioniche e una procedura dettagliata per gli ioni di intrappolamento utilizzando le trappole fabbricate sono descritti. Inoltre, le descrizioni dettagliate delle varie tecniche pratiche per predisporre il sistema sperimentale e intrappolare gli ioni sono fornite nel Documento complementare.

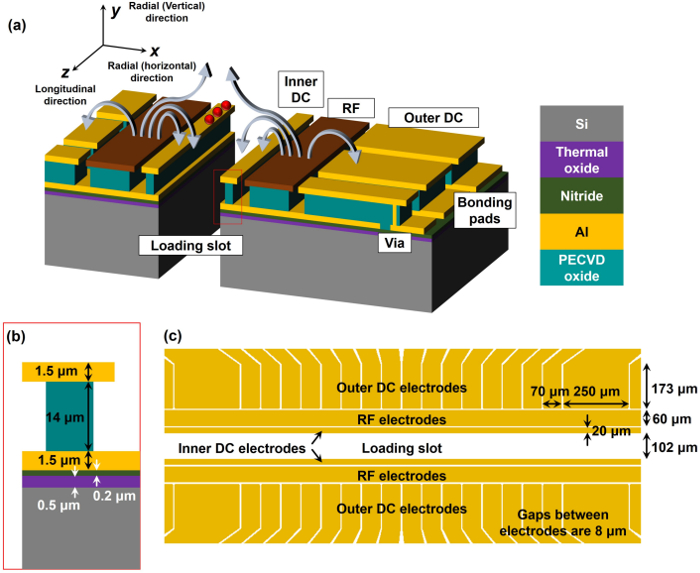

La metodologia per microfabricating una superficie trappola ionica è dato nel passaggio 1. La figura 1 Mostra uno schema semplificato di un superficie trappola ionica. I campi elettrici generati dalla tensione applicata agli elettrodi nel piano trasversa sono indicati anche25. Una tensione di RF è applicata alla coppia di elettrodi RF, mentre tutti gli altri elettrodi sono tenuti a terra RF; il potenziale di ponderomotrice26 generato dalla tensione RF limita gli ioni nella direzione radiale. La tensione di corrente continua (DC) applicata agli elettrodi multipli DC fuori gli elettrodi RF confinare gli ioni nella direzione longitudinale. I binari interni tra gli elettrodi di RF sono progettati per aiutare inclinare gli assi principali del potenziale totale nel piano trasversa. La metodologia per la progettazione di un insieme di tensione DC è incluso nel Documento complementare. Inoltre, più dettagli per progettare i parametri geometrici essenziali di superficie trappola ionica chip si trovano in27,28,29,30,31.

Il metodo di fabbricazione introdotto nel passaggio 1 è stato progettato considerando i seguenti aspetti. In primo luogo, lo strato dielettrico tra lo strato di elettrodo e lo strato di terra dovrebbe essere sufficientemente spesso per impedire la ripartizione elettrica tra gli strati. Generalmente, lo spessore dovrebbe essere sopra 10 µm. Durante la deposizione dello strato dielettrico spessa, dello stress residuo da pellicole depositate possa causare inchinandosi del substrato o danni dei film depositati. Così, controllare la tensione residua è uno delle tecniche chiave nella fabbricazione delle superficie trappole dello ione. In secondo luogo, l'esposizione delle superfici dielettriche alla posizione dello ione deve essere minimizzato perché randagi cariche possono essere indotte sul materiale dielettrico da laser sparsi ultravioletto (UV), che nei risultati di girare in uno spostamento casuale dello ione di posizione. L'area esposta può essere ridotto di progettazione di strutture di elettrodo di sporgenza. È stato segnalato che in superficie trappole ioniche con elettrodo strapiombi sono resistenti alla carica in condizioni sperimentali tipiche32. Terzo, tutti i materiali, tra cui varie pellicole depositate, dovrebbero essere in grado di resistere a 200 ° C, cottura per circa 2 settimane, e la quantità di emissione di gas da tutti i materiali deve essere compatibile con ambienti di UHV. Il design della trappola ionica superficiale chip microfabbricati in questa carta è basato sul design di trappola da33, che è stato utilizzato con successo in vari esperimenti32,33,34, 35. si noti che questo disegno include uno slot nel mezzo il chip per caricamento atomi neutri, che vengono poi foto ionizzata per il trapping.

Dopo il montaggio del chip trappola ionica, il chip è montato e collegato elettricamente al vettore chip utilizzando fili di oro incollaggio. Il trasportatore di chip viene quindi installato in una camera in UHV. Una procedura dettagliata per la preparazione di un package di chip di trappola e il design della camera UHV sono forniti nel Documento complementare.

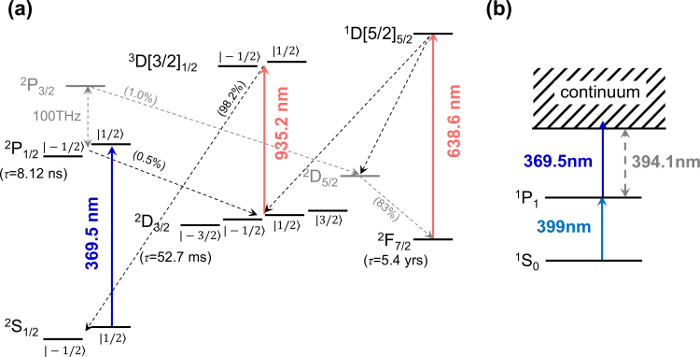

Preparazione delle attrezzature ottiche ed elettriche, nonché le procedure sperimentali per gli ioni di intrappolamento, sono spiegati in dettaglio nel passaggio 2. Gli ioni intrappolati dal ponderomotrice potenziali sono generalmente soggetti a fluttuazioni del campo elettrico circostante, che continuamente aumenta l'energia cinetica media degli ioni. Raffreddamento a laser basato su effetto Doppler può essere utilizzato per rimuovere l'eccesso di energia dal movimento degli ioni. La figura 2 Mostra i diagrammi semplificati di livello di energia di un ione di Yb+ 174e un atomo neutro 174di Yb. Doppler raffreddamento di 174Yb+ ioni richiede un 369,5-nm e un laser di 935-nm, mentre foto-ionizzazione degli atomi Yb neutro 174richiede un laser 399-nm. Punti 2.2 e 2.3 descrivono un metodo efficiente per allineare questi laser per il chip di superficie trappola ionica e una procedura per trovare le giuste condizioni per foto-ionizzazione. Dopo i componenti ottici ed elettrici sono preparati, intrappolando gli ioni è relativamente semplice. La sequenza sperimentale per gli ioni dell'intrappolamento è presentata al punto 2.4.

Protocollo

1. fabbricazione del pacchetto Chip trappola ionica

- microfabbricazione del chip superficie trappola ionica.

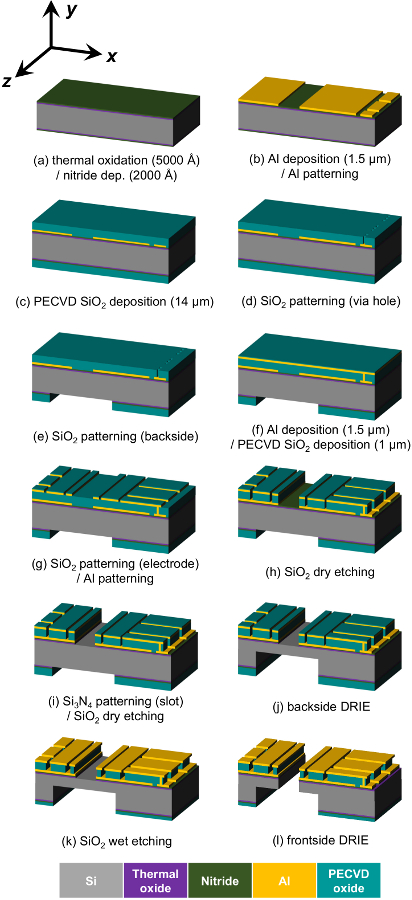

Nota: Le condizioni di processo descritte in questa sezione forniscono solo un riferimento approssimativo, poiché i parametri ottimali per ogni processo possono variare notevolmente per attrezzature diverse. Le condizioni di temperatura sono fornite solo per i processi ad alta temperatura, quali l'ossidazione e la deposizione chimica da vapore. Il processo di fabbricazione avviene utilizzando wafer di silicio 100 mm di diametro.- Preparare un singolo silicio cristallino wafer con uno spessore di 500-525 µm e pulirlo utilizzando soluzione piranha per 15 min.

- Termicamente ossidare il wafer di silicio in un tubo di fornace per formare SiO 2 dielettrici strati di 0,5 µm di spessore su entrambi i lati.

Nota: Questi strati possono isolare elettricamente il substrato di silicio dal livello del terreno. I parametri di processo utilizzati nell'umido-ossidazione erano: tasso di flusso di 2 O di 6.500 sccm, N 2 flusso tasso di 5.000 sccm, tasso di flusso di 2 H di 7.000 sccm, temperatura di 900 ° C e tempo di 4,5 h (vedere la tabella di processo Materiali per particolari dell'apparecchiatura). - Depositare 0,2 µm di spessore Si 3 N 4 strati su entrambi i lati del wafer utilizzando un processo di deposizione (LPCVD) a bassa pressione di vapore chimico ( Figura 3a) per proteggere gli strati di ossido termico durante la bagnato-acquaforte processo illustrato nella Figura 3 k.

Nota: I parametri di processo utilizzati nel processo di LPCVD sono: tasso di flusso 2 SiCl 2 H di 30 sccm, NH 3 velocità di flusso di 100 sccm, pressione di 200 mTorr e temperatura di processo di 785 ° C. Ciò si traduce in un tasso di deposizione di 40 Å / min (vedere la Tabella materiali particolari attrezzature). - Depositare uno strato di Al/Cu (1%) µm di spessore 1,5 sul wafer utilizzando un processo per sputtering e i seguenti parametri: velocità di flusso di Ar di 40 sccm, pressione di mTorr 2 e RF potenza di 300 w.

Nota: In questo modo un tasso di deposizione di 130 Å / min (vedere la Tabella materiali particolari attrezzature).

Nota: Questo strato fornisce un piano di massa per evitare la perdita di RF attraverso il substrato di silicio e fornisce anche i punti di contatto per i rilievi di wire-bonding. La lega di alluminio con 1% di rame è usata per prevenire la formazione di whisker durante il processo di cottura per ottenere un ambiente UHV. Questa composizione è essenziale per la prevenzione di whisker. - Spin uno strato di photoresist positivo di 2 µm di spessore sul wafer e litograficamente modello per definire la protezione aereo e wire-bonding pastiglie di RF.

Nota: I parametri di processo per il photoresist 2 µm di spessore sono: velocità di 5.000 giri di centrifuga, spin tempo di 40 s, pre-cuocere temperatura di 95 ° C, tempo di pre-cuocere di 90 s, energia di esposizione di 144 mJ/cm 2, sviluppare tempo di 60 s, post-cuocere temperatura di 110 ° C e post-cuocere tempo di 5 min (Vedi Tabella materiali chimici e attrezzature particolari). - Modello 1.5 µm di spessore Al/Cu (1%) livello, mediante un processo a secco-acquaforte convenzionale (acquaforte reattiva dello ione (RIE) o plasma accoppiato induttivo (ICP) incisione), con il photoresist modellato punto 1.1.5 come la maschera di acquaforte.

Nota: Un incisore ICP deve essere utilizzato con i seguenti parametri di processo: BCl 3 portata di 20 sccm, Cl 2 portata di 30 sccm, pressione di 5 mTorr e potenza RF di 750 w. Ciò si traduce in un tasso di etch di 3.600 Å/min (vedere la Tabella materiali particolari attrezzature). - Rimuovere il photoresist utilizzato nel processo di incenerimento passo 1.1.6 usung un O 2 plasma ( Figura 3b).

Nota: I parametri di processo per il processo di incenerimento sono: 2 in portata di 150 sccm, pressione di 0,75 mTorr e RF potenza di 300 W (Vedi la Tabella materiali particolari attrezzature) di O. - Depositare uno strato di 2 SiO µm di spessore 14 su entrambi i lati del wafer utilizzando plasma enhanced chemical vapor deposition (PECVD) processi ( Figura 3C).

Nota: I parametri di processo utilizzati nel processo PECVD sono: SiH 4 portata di 540 sccm, pressione di 1,9 Torr, processo temperatura di 350 ° C e potenza RF di 750 w. Ciò si traduce in un tasso di deposizione di 3.000 Å / min (vedere la Tabella materiali particolari attrezzature). Poiché depositando il 14 µm di spessore SiO 2 strato è uno dei processi più difficili, i dettagli sono ulteriormente descritti nella discussione. - Spin uno strato di photoresist positivo di 6 µm di spessore sulla parte anteriore del wafer e litograficamente modello per definire tramite fori per collegare elettricamente DC elettrodi le pastiglie di wire-bonding.

Nota: I parametri di processo per il photoresist 6 µm di spessore sono: velocità di 5.000 giri di centrifuga, girare tempo di 40 s, pre-cuocere temperatura di 95 ° C, tempo di pre-cuocere di 5 min, energia di esposizione di 900 mJ/cm 2, sviluppare tempo di 10 min, post-cuocere temperatura di 110 ° C e post-cuocere tempo di 5 min (Vedi Tabella materiali chimici e attrezzature particolari). - Modello il 14 µm-spessore SiO 2 strato sulla parte anteriore del wafer utilizzando un processo convenzionale di RIE, con il photoresist modellato nel passaggio 1.1.9 come la maschera di acquaforte.

Nota: I parametri di processo per SiO 2 acquaforte sono: CHF 3 tasso di flusso di 25 sccm, la CF 4 portata di 5 sccm, portata di 50 sccm per Ar, pressione di 130 mTorr e RF potenza di 600 w. Ciò si traduce in un tasso di etch di 3.600 Å/min (vedere la Tabella materiali particolari attrezzature). - Rimuovere il photoresist utilizzato nel passaggio 1.1.10 con un processo di incenerimento O plasma di 2. Immergere la cialda in un solvente riscaldato o sottoporre ad ultrasuoni e prima lampeggiante ( figura 3d).

- Spin uno strato di photoresist positivo di 6 µm di spessore sul retro della cialda e litograficamente modello per formare una maschera di ossido duro per l'acquaforte reattiva profonda dello ione (DRIE) di substrato di silicio ( Figura 3j).

- Strato di pattern 14 µm di spessore SiO 2 sul retro del wafer utilizzando un processo convenzionale di RIE, con il photoresist modellato nel passaggio 1.1.12 come la maschera di acquaforte.

- Rimuovere il photoresist utilizzato nel passaggio 1.1.13 con un processo di incenerimento di O 2 plasma ( Figura 3e).

- Depositare uno strato di Al/Cu (1%) µm di spessore 1.5, che è usato come elettrodo utilizzando un processo per sputtering.

- Depositare uno strato di 2 di 1 µm di spessore SiO sul wafer utilizzando un processo PECVD ( Figura 3f).

- Spin uno strato di photoresist positivo di 2 µm di spessore sul wafer e litograficamente modello per definire gli elettrodi.

- Modello 1.5 µm di spessore Al/Cu (1%) strato e 1 µm di spessore SiO 2 livello utilizzando un ICP convenzionale di mordenzatura con il photoresist modellato nel passaggio 1.1.17 come la maschera di acquaforte.

- Rimuovere il photoresist utilizzato nel passaggio 1.1.18 con un processo di incenerimento di O 2 plasma ( Figura 3 g).

- Spin uno strato di photoresist positivo di 6 µm di spessore sul wafer e litograficamente modello per definire i 14 modelli di pilastro µm di spessore ossido.

- Modello 14 µm di spessore SiO 2 strato utilizzando un processo convenzionale di RIE, con il photoresist modellato nel passaggio 1.1.20 come la maschera di acquaforte.

- Rimuovere il photoresist utilizzato nel passaggio 1.1.21 con un processo di incenerimento di O 2 plasma ( Figura 3 h).

- Spin uno strato di photoresist positivo di 6 µm di spessore sul wafer e litograficamente modello per esporre la fessura di caricamento.

- Modello di SiO 2 e processo di strati di Si 3 N 4 utilizzando un RIE convenzionale, con il photoresist modellato nel passaggio 1.1.23 come la maschera di acquaforte.

- Rimuovere il photoresist utilizzato nel passaggio 1.1.24 con un processo di incenerimento di O 2 plasma ( Figura 3i).

- Modello il substrato di silicio dal didietro del wafer utilizzando un processo DRIE ( Figura 3j).

Nota: La profondità di etch dovrebbe essere misurata ripetutamente per impedire la penetrazione del substrato di silicio dal didietro. La destinazione etch profondità è di circa 450-470 µm. Il processo DRIE è stato effettuato con iterazioni di C 4 F 8 deposizione per 5 s, C, 4 F 8 etch per 3 s e Si etch per 5 s. Nel passo di deposizione di C 4 F 8, le portate di C 4 F 8, SF 6 e Ar erano 100, 0,5 e 30 sccm, rispettivamente. Si noti che Ar è usato per accelerare il tasso di etch di C 4 F 8 e Si, ma è applicato anche nella fase di deposizione C 4, F 8, con la stessa portata, per stabilizzare la condizione di pressione. In C 4 F 8 etch passo, le portate sono state modificate per 0,5, 50 e 30 sccm, rispettivamente. Nel Si etch passo, i tassi di flusso di 0,5, 100 e 30 sccm, rispettivamente, sono stati utilizzati. La potenza RF e la pressione dell'alloggiamento sono impostate su 825 W e 23 mTorr in tutte le fasi. Per queste condizioni, il tasso di etch del Si era 1 µm per ogni ciclo (Vedi la Tabella materiali per particolari dell'apparecchiatura). - Dadi la cialda in pezzi di 10 mm x 10 mm utilizzando un affettatrici.

- Staccare il nastro dadini dallo stampo immergendolo in acetone per 5 min, pulire lo stampo immergendolo in acqua deionizzata (DI) per 10 min e alcool isopropilico (IPA) per 2 min asciugare per 2 min a 110 ° C.

- Etch i fianchi dei pilastri dell'ossido per fabbricare strutture di sporgenza elettrodo utilizzando un bagnato ossido mordenzatura per 60 s in un mordenzante di ossido tamponata (BOE), che è (NH 4 F:HF = 6:1) ( Figura 3 k). Pulire lo stampo immergendolo in acqua DI corrente per 10 min e IPA per 2 min asciugare per 2 min a 110 ° C.

- Penetrare lo ione a forma di fessura, foro di caricamento dalla parte anteriore dello stampo usando un processo DRIE.

Nota: Il processo di fabbricazione dei chip trappola ionica è completo in questa fase ( Figura 3 l).

2. Preparazione di ottica e di apparecchiature elettriche e di cattura ioni

Nota: il chip fabbricato trappola è confezionato con un vettore di chip, e il vettore di chip è installato in una camera in UHV. Mentre le procedure per la realizzazione del pacchetto di trappola-chip e per preparare la camera in UHV sono fornite nel Documento integrativo, in questa sezione vengono descritti i dettagli per l'impostazione di apparecchiature elettriche ed ottiche e per gli ioni dell'intrappolamento.

- Preparazione dei collegamenti elettrici.

- Connetti un convertitore di multi-canale digitale-analogico (DAC) per il passante sul retro della camera UHV per applicare tensione agli elettrodi di controllo DC corrispondenti.

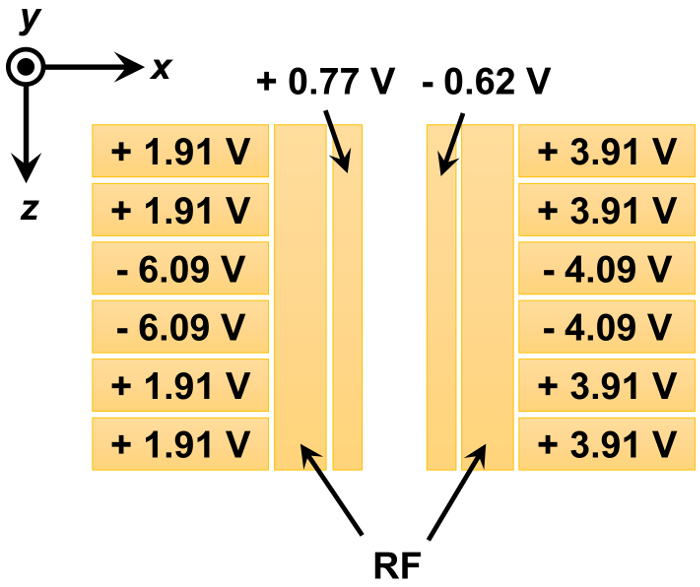

Nota: La Figura 4 Mostra un esempio della tensione applicata al chip trappola. Il metodo dettagliato per la progettazione di tali un set di tensione DC è descritto nel Documento complementare. - Collegare un generatore di corrente ad un pin di forno nel passante posteriore.

- Aggiungere un Accoppiatore direzionale tra un generatore RF e il risonatore elicoidale. Collegare il segnale dal generatore RF alla porta di uscita dell'accoppiatore direzionale. Inoltre, collegare la porta di ingresso dell'accoppiatore direzionale alla porta di ingresso del risonatore elicoidale.

Nota: Questa configurazione consente il monitoraggio la potenza riflessa dalla risonatore elicoidale 36. - Regolare la posizione del tappo risonatore elicoidale e la scansione la frequenza del generatore per trovare la frequenza a cui la riflessione è minimo. Ripetere questo passaggio finché non viene trovato il minimo globale.

Nota: La frequenza al minimo globale è la frequenza di risonanza. Uso di un analizzatore di spettro con un generatore di tracking opzione o misura del parametro 11 S con un analizzatore di rete può semplificare il processo di scansione per la riflessione minima. Se uno qualsiasi dei collegamenti elettrici con una sorgente di tensione DAC o fonte di corrente per il forno viene modificato, l'impedenza del passante RF è cambiato, e la frequenza di risonanza si sposterà. - Spegnere il generatore RF.

Attenzione: Quando il risonatore elicoidale è l'applicazione di alta tensione RF alla trappola, non modificare i collegamenti elettrici che possono causare cambiamenti di impedenza. Cambiamenti improvvisi di impedenza possono facilmente masterizzare i fili di incollaggio del chip.

- Connetti un convertitore di multi-canale digitale-analogico (DAC) per il passante sul retro della camera UHV per applicare tensione agli elettrodi di controllo DC corrispondenti.

- Allineamento del laser 369.5 nm e il sistema di imaging.

- Collimare il laser 369,5-nm da una fibra ottica utilizzando un collimatore e tenta di abbinare l'altezza del collimatore dalla superficie del tavolo ottico all'altezza del chip; make il fascio propaga orizzontalmente.

- Impostare la direzione di propagazione del fascio collimato 369,5-nm verso il chip di trappola, attraverso la finestra sinistra o a destra della camera UHV, come mostrato nella Figura 5. Grossolanamente allinearla in modo tale che il raggio laser si propaga paralleli alla superficie di trappola-chip e quasi tocca la superficie del chip.

- Montare una lente di focalizzazione del laser di 369,5-nm su una fase di traduzione. Posizionare la lente di focalizzazione lungo la direzione di propagazione affinché il laser sarà focalizzato in prossimità della posizione di cattura sopra la superficie del chip e in modo che il laser focalizzato si propaga lungo la superficie di trappola-chip. Regolare la posizione della lente messa a fuoco con la fase di traduzione; la posizione del fuoco del fascio laser seguirà il movimento della lente messa a fuoco.

- Posto un obiettivo di imaging ad alta apertura numerica montato su un palco di traduzione davanti la camera in UHV, considerando la distanza dalla superficie del chip ( Figura 5).

- Allineare il fascio di 369,5-nm con la superficie di trappola-chip in modo che ci è una certa quantità di scattering laser dalla superficie del chip.

Nota: La luce sparsa raccolta dalla lente imaging formerà un'immagine sfumata intorno all'aereo di immagine della lente. Questa immagine generalmente può essere osservata, anche con carta fluorescente quando la zona è sufficientemente buio. - Regolare la posizione della lente imaging, fino a quando l'immagine sulla carta fluorescente diventa nitida.

- Posto un dispositivo di carica-accoppiato elettrone-moltiplicato (EMCCD) montato su una fase di traduzione, considerando la posizione dell'aereo imaging della lente, trovato nel passaggio precedente.

- Montare un filtro a infrarossi (IR) davanti il EMCCD per bloccare la radiazione di corpo nero dal forno quando il forno viene riscaldato per evaporazione.

- Montare un filtro passa-banda 369,5-nm davanti il EMCCD per bloccare la luce di sfondo.

- Confronta l'immagine della EMCCD con la disposizione degli elettrodi. Regolare la posizione dell'EMCCD e la lente di immagine fino a quando gli elettrodi possono essere visto con il EMCCD. Allineare la lente imaging sia il EMCCD finché l'immagine diventa nitida.

- Identificare quali elettrodi vengono mostrati nel EMCCD e allineare il EMCCD per abbinare il suo centro nella posizione prevista dell'intrappolamento.

- Allineare il fascio di 369,5-nm verticalmente in modo che passerà attraverso la posizione di cattura. Per trovare la distanza tra il centro del fascio e la superficie della trappola, spostare il raggio verso la superficie di presa fino a quando la dispersione del fascio è massimizzata.

Nota: Dopo il passaggio 2.2.12, si può presumere che il centro del fascio è proprio sulla superficie del chip. - Dalla simulazione numerica della trappola potenziale 29, trovare l'altezza prevista della posizione di cattura di ioni dalla superficie del chip. Spostare il raggio nm 369.5 dalla superficie del chip dell'altezza prevista utilizzando il micrometro della fase di traduzione di lente. Spostare la lente di imaging e il EMCCD nuovamente con la stessa distanza. Annotare le letture di micrometro della lente imaging e il EMCCD.

- Allineamento dei 399 nm e 935 nm laser e il forno test.

- Sostituire il passa-banda nm 369,5 filtra con un filtro di banda 399 nm. Dalla simulazione numerica della lente imaging, trovare la differenza tra la lunghezza focale di 399-nm luce e quella della luce di 369,5-nm derivanti dall'aberrazione cromatica. Regolare la posizione longitudinale della lente imaging ed EMCCD per rendere i 399-nm focalizzato sull'EMCCD.

- Collimare le travi nm 399 e 935, consegnate da fibre ottiche, con i rispettivi collimatori e regolare l'altezza dei collimatori di fibra per adattarsi all'altezza del chip per rendere entrambi i fasci propaga orizzontalmente.

- Allineare il fascio 399 nm verso la superficie di trappola-chip attraverso un'altra finestra in modo tale che il laser nm 399 sta propagando in direzione opposta da parte 369.5 nm laser. Provare a fare i 399 collimato nm laser sovrapposizione con il laser focalizzato 369.5 nm.

- Il fascio collimato 935 nm si combinano con il laser di nanometro 399 collimato usando uno specchio dicroico e allineare il fascio nm 935 in modo tale che il laser nm 935 Co-si propaga con il laser di 399-nm. Per controllare quanto bene i due fasci sono sovrapposte con a vicenda, deviare quei due fasci con uno specchio temporaneo prima di entrare nella camera e misurare le posizioni delle travi lungo il percorso del fascio utilizzando un profiler del fascio o un foro stenopeico. Se lo spazio è insufficiente per posizionare lo specchio temporaneo tra la camera e la lente di focalizzazione, considerare di mettere la configurazione ottica su un piccolo tagliere ottico; il grado di sovrapposizione può essere controllato in un luogo separato.

- Montare una lente di focalizzazione per entrambi i laser su un palcoscenico di traduzione aggiuntiva e impostare la messa a fuoco tra lo specchio dicroico e lo specchio temporaneo. Stimare la distanza dallo specchio temporaneo per la posizione di cattura e regolate la posizione della lente messa a fuoco in modo che il laser nm 399 è concentrata presso la posizione di cattura ( Figura 6b).

- Verifica se la messa a fuoco del laser nm 399 coincide con la messa a fuoco del laser nm 935. Se i due fuochi non si sovrappongono, finemente allineare il laser nm 935.

- Rimuovere lo specchio temporaneo nel percorso del laser nm 399. Verifica la traccia di 399 nm laser sulla superficie del chip utilizzando EMCCD. Se nessuna traccia del fascio laser 399 nm può essere osservata, spostare il percorso del fascio nm 399 intorno il chip. Inoltre, modificare leggermente la distanza tra la camera e la formazione immagine lente fino a quando l'immagine della superficie del chip diventa nitida.

- Allineare la traccia del fascio 399 nm sulla superficie del chip in modo che passerà la posizione di cattura previsto. Simile all'allineamento del fascio nm 369.5, sposta il fascio di 399-nm verso la superficie del chip fino a quando l'intensità della luce diffusa diventa ingrandita.

- Spostare il fascio di laser nm 399 dalla superficie del chip della stessa altezza utilizzata nel passaggio 2.2.13 utilizzando un micrometro. Spostare la lente di imaging e il EMCCD nuovamente con la stessa distanza.

- Mettere lo specchio temporaneo utilizzato nel passaggio 2.3.4 indietro. Ripetere il passaggio 2.3.6 e quindi rimuovere lo specchio temporaneo.

Nota: Dopo il passaggio 2.3.10, il laser nm 935 può presumere di essere passando per la posizione di cattura sopra la superficie del chip. - Impostare la lunghezza d'onda del laser nm 399 vicino a 1 S 0-1 P 1 transizione di 174 Yb (751.526 GHz). Accendere la corrente per il forno riempito con biofiltri Yb e aumentare gradualmente la corrente.

Nota: In generale, evaporazione non inizia necessariamente alla stessa corrente trovata dall'analizzatore di gas residuo (RGA), come descritto nel Documento complementare, quindi provare diversi valori di correnti fino ad evaporazione è osservare. Solo quando gli atomi neutri di Yb iniziano a evaporare e la frequenza del laser è risonante con 1 S 0-1 P 1 transizione di uno degli isotopi Yb, il Yb neutro atomi inizierà ad assorbire il laser luce e ri-generare tale che la fluorescenza dal Yb può essere osservata con il EMCCD. Generalmente, le frequenze di risonanza misurate con un metro di lunghezza d'onda sono spostate dai valori nominali, che vanno da decine a centinaia di MHz. Pertanto, la frequenza del laser con una gamma di span di 1 GHz e un passo di meno di 50 MHz scansione è consigliata per ogni impostazione corrente,. - Una volta si osserva la fluorescenza risonante da forno naturale, ridurre la corrente fino a quando non è possibile osservare la fluorescenza.

- Scansione laser intorno la prima frequenza risonante e annotare la quantità di fluorescenza a ogni risonanza. Confrontare la distribuzione della forza di fluorescenza e la spaziatura tra le risonanze con i valori da 37. Identificare le frequenze di risonanza per gli isotopi diversi.

Nota: La risonanza di 174 Yb è stata misurata per essere circa 751.52646(2) THz. Tuttavia, questo valore è leggermente spostato dall'effetto di Doppler, e il valore misurato può variare a seconda della precisione del contatore Lunghezza d'onda.

- Intrappolando ioni.

- Sostituire il 399 filtro passabanda nm con il 369.5 filtro passabanda nm e spostare la lente di imaging e il EMCCD nuovamente la posizione ottenuta al passaggio 2.2.13 in modo che la fluorescenza di 369,5-nm emessa da ioni intrappolati possa essere imaged presso il EMCCD. Verificare l'allineamento di tutti i laser ancora una volta ripetuto il passaggio 2.2.12 e utilizzando UV e IR guardato le carte per l'ispezione visiva della sovrapposizione fascio.

- Verifica che le tensioni del DAC unre correttamente impostato. Accendere il generatore di RF con un'impostazione di potenza molto bassa e aumentare gradualmente la potenza in uscita. Inoltre, assicurarsi che la potenza riflessa dal risonatore elicoidale è ancora il minimo analizzando la frequenza RF risonanza.

Attenzione: Assicurarsi che la tensione amplificata il chip trappola non superi la tensione di ripartizione. A pressione atmosferica, la rigidità dielettrica di un SiO 2 film è noto per essere circa 10 7 V/cm, ma questo valore non può essere presupposta nell'ambiente UHV. Anche se la tensione di ripartizione esatta nell'ambiente UHV non è misurata in modo esplicito, lo spacco laterale 8-µm di trappola di chip in un 10 -11-Torr vuoto resiste a 240 V dell'ampiezza di corrente RF nel setup sperimentale. - Impostare la frequenza del laser 399-nm per la frequenza di risonanza di 174 Yb, identificato nel passaggio 2.3.13. Impostare la frequenza del laser per l'isotopo di Yb + 174 935-nm.

Nota: Con un metro di lunghezza d'onda, può essere utilizzato 320.57199(1) THz, ma a causa della precisione limitata di metri di lunghezza d'onda, ci può essere una variazione fino a decine di MHz. - Impostare la frequenza del laser 369,5-nm ad un valore di ~ 100-200 MHz inferiore alla frequenza di risonanza così che, anche se c'è una certa quantità di imprecisione con il metro di lunghezza d'onda, la frequenza sarà ancora rosso-detuned.

Nota: Qui, 200 MHz detuning viene sottratto dalla risonanza prevista quando la frequenza di risonanza prevista di 174 Yb + è di circa 811.29152(1) THz. - Attivare la sorgente di corrente per il forno e l'aumento della corrente lentamente fino a quando raggiunge il valore trovato nel passaggio 2.3.12. Attendere per alcuni minuti. Se nessun ioni sono intrappolato, aumentare la corrente di ~0.1-0.2 A e attendere ancora. Se lo ione non è ancora intrappolato, verificare se la RF riflessa è ancora al minimo e poi aumentare gradualmente la potenza di uscita del generatore RF.

Attenzione: Assicurarsi che la tensione amplificata il chip trappola non superi la tensione di ripartizione previsto. - Brevemente bloccare il laser nm 935 e verificare se vi è alcun cambiamento nell'immagine.

Nota: Se le impostazioni di EMCCD (tra cui l'elettrone-moltiplicando (EM) guadagno, tempo di esposizione e contrasto dell'immagine) non sono all'interno di un intervallo corretto, anche quando un ione è intrappolato, non è facile dire se il cambiamento di intensità in prossimità della regione di intrappolamento è causato da un ione reale intrappolato o dalla variazione la dispersione del laser 369.5 nm. A causa del filtro IR, telecamera EMCCD non può mostrare qualsiasi cambiamento nel 935 laser nm, così bloccando il laser nm 935 non apportare modifiche all'immagine quando non c'è nessun ioni intrappolati. Tuttavia, se un ione è intrappolato, il tasso di dispersione del laser nm 369.5 scende significativamente senza il laser nm 935. Di conseguenza, il cambiamento dell'immagine di EMCCD causato bloccando il 935 laser nm è un buon indicatore del successo di ioni dell'intrappolamento.

Attenzione: Se il laser nm 935 è bloccato per troppo tempo, gli ioni intrappolati ottiene riscaldato e potrebbe sfuggire alla trappola. - Spegnere il forno dopo gli ioni sono intrappolati. Cercare di trovare la risonanza del laser nm 369.5 aumentando gradualmente la frequenza.

Nota: La frequenza si avvicina alla risonanza, aumenterà il tasso di dispersione, ma una volta che la risonanza è attraversata, il laser nm 369.5 inizia riscaldamento lo ione piuttosto che raffreddandolo, che a sua volta causa l'immagine dello ione intrappolato a diventare instabile. Una volta trovata la frequenza di risonanza del laser nm 369.5, ridurre la frequenza del laser da 10 MHz dalla risonanza. - La frequenza del 935 nm laser di scansione fino a quando il tasso di dispersione di 369,5 ottiene ingrandita nm.

- Regolare le posizioni di imaging lente e la fotocamera EMCCD fino a quando l'immagine dello ione affila.

Risultati

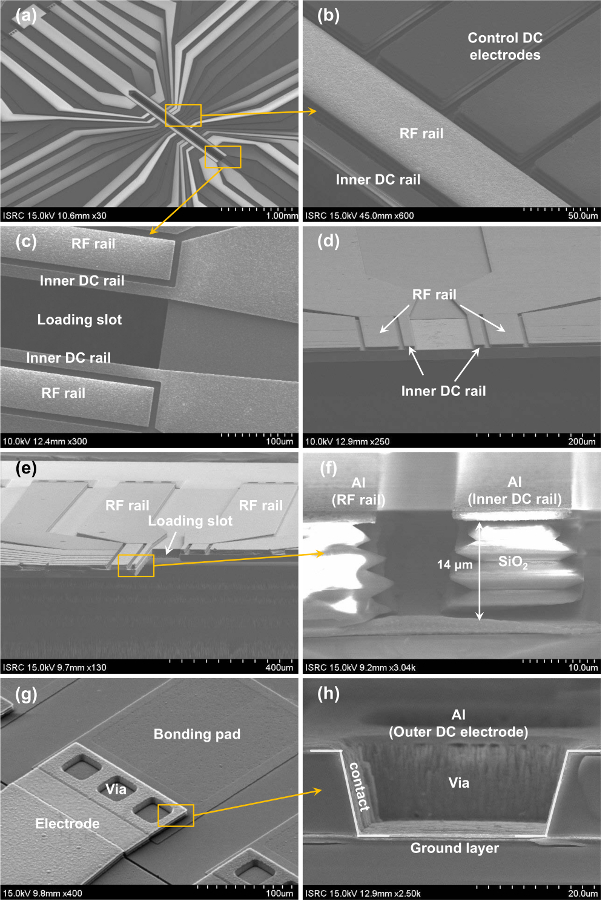

La figura 7 Mostra i micrografi scansione (SEM) del chip fabbricato trappola ionica. La RF elettrodi, elettrodi DC interni, esterno DC elettrodi e fessura di caricamento sono stati fabbricati con successo. Il profilo della parete laterale del pilastro dielettrico è diventato irregolare perché l'ossido PECVD è stato depositato in diversi passaggi. I molteplici passaggi di deposizione sono stati utilizzati per ridurre al minimo gli effetti delle tensioni residue da film di ossido spessa. Questo è ulteriormente descritto nella discussione.

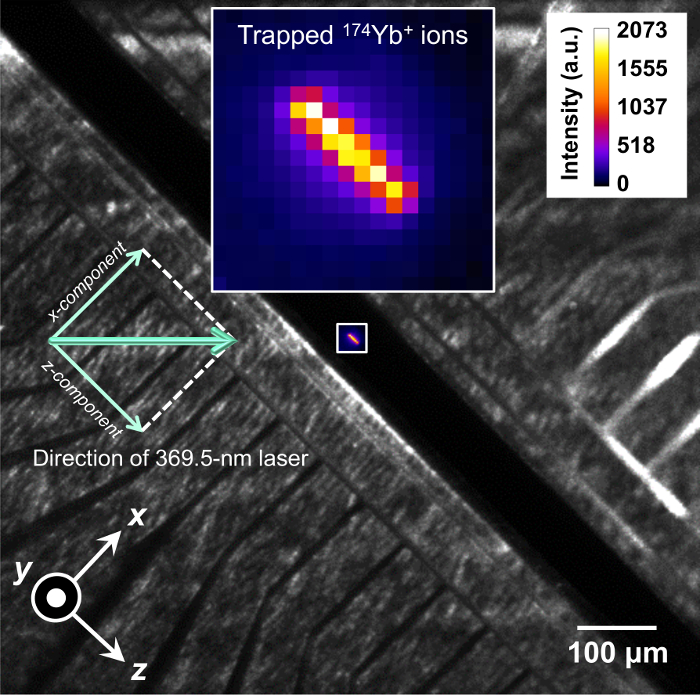

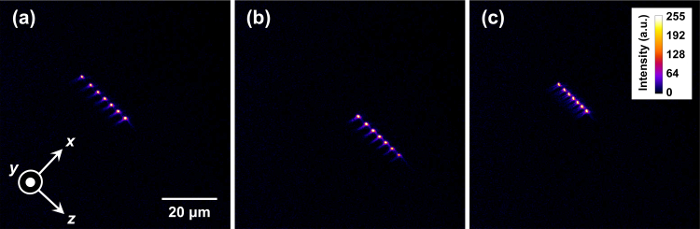

Figura 8 Mostra l'immagine EMCCD di cinque 174Yb+ ioni intrappolati utilizzando il chip di trappola ionica microfabbricati. Gli ioni intrappolati possono durare per più di 24 h con Doppler continuo raffreddamento. Il numero di ioni intrappolati può essere regolato tra 1 e 20 modificando il set di tensione DC applicato. Questa messa a punto sperimentale è molto affidabile e robusto e attualmente è stato in funzione per 50 mesi.

Figura 9 Mostra la marcia degli ioni intrappolati lungo la direzione assiale. La posizione di ioni nella Figura 9b è spostata da quella in figura 9a attraverso la regolazione della posizione del minimo potenziale DC modificando le tensioni CC.

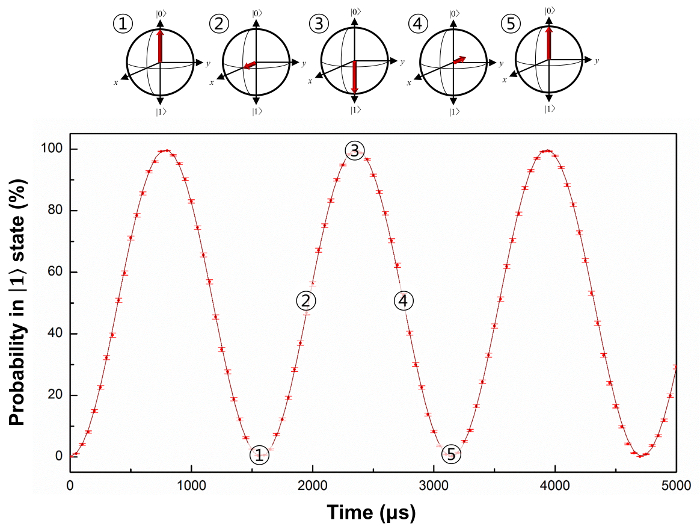

La figura 10 Mostra i risultati preliminari di Rabi oscillazione esperimenti con un ione di Yb+ 171. Per ottenere i risultati, sono state utilizzate le configurazioni aggiuntive descritte nel Documento complementare . I risultati sono stati inclusi per mostrare una potenziale applicazione del setup sperimentale spiegato in questo documento.

Figura 1: schematico della presa dello ione superficie. (un) il rosso punti rappresentano gli ioni intrappolati. Gli elettrodi di marroni e gialli indicano gli elettrodi RF e DC, rispettivamente. Le frecce grigie indicano la direzione del campo elettrico durante la fase positiva della tensione RF. Si noti che lo schema non viene disegnato in scala. dimensioni (b) verticale della struttura dell'elettrodo. dimensioni (c), il laterale della struttura dell'elettrodo. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 2: Diagrammi di livello di energia semplificati di un ione di Yb+ 174e un atomo neutro 174di Yb. (a) quando un 369,5 nm laser è depotenziato a lato rosso (bassa frequenza) della risonanza, una transizione in bicicletta tra 2P1/2 e 2S1/2 riduce l'energia cinetica dello ione a causa l'effetto Doppler effetto. Occasionalmente, un rapporto di ramificazione piccolo ma finito rende il decadimento dell'elettrone da 2P1/2 a 2D3/2, e un laser di 935-nm è tenuto a restituire l'elettrone torna alla transizione principale in bicicletta. L'elettrone può anche decadere in uno stato di7/2 2F una volta all'ora, in media e un laser nm 638 si può pompare fuori dallo stato di7/2 2F, ma questo non è necessario per un semplice sistema38. I valori nella notazione ket rappresentano le proiezioni del momento angolare totale J lungo l' asse di quantizzazione m.J. (b) per ionizzare atomi neutri evaporati dal forno, un processo di assorbimento a due fotoni è stato usato39. Un laser di nanometro 399 eccitato un elettrone a 1P1 stato, e il fotone 369.5 nm per raffreddamento Doppler aveva più energia del necessario per rimuovere l'elettrone eccitato dal ione. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 3: flusso del processo di fabbricazione di una superficie trappola ionica. (un) termico ossidazione a crescere un 5.000 Å spessore SiO2 livello e LPCVD di uno strato di 2.000 Å spessore Si3N4 . (b) deposizione e ICP acquaforte di uno strato di Al sputtered di 1,5 µm di spessore. (c), deposizione di un 14 strato2 SiO di µm di spessore su entrambi i lati del wafer utilizzando processi PECVD. (d) Patterning 14 µm di spessore SiO2 strato depositato sulla parte anteriore del wafer utilizza un processo RIE (e) di Patterning del 14 µm-spessore SiO2 strato depositato sul retro del wafer utilizza un processo RIE. (f), deposizione di un 1.5 µm spessore polverizzato Al layer e uno strato di2 di 1 µm di spessore PECVD SiO. processo di Patterning del 1,5 µm di spessore Al livello utilizza un processo ICP e 1 µm di spessore SiO2 livello utilizzando un RIE (g). (h) Patterning del 14 µm-spessore SiO2 strato depositato sulla parte anteriore del wafer utilizza un processo RIE. (i) processo di Patterning 5.000 Å spessore SiO2 strato di e 2.000 Å di spessore Si3N4 livello utilizzando un RIE. (j), DRIE del substrato di silicio 450 µm dal retro del wafer. (k) bagnato-acquaforte del SiO2 livello sugli elettrodi Al e le pareti laterali dei pilastri dielettrici. (l) penetrazione del substrato di silicio dalla parte anteriore attraverso un processo DRIE. Si noti che gli schemi non vengono disegnati in scala. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 4: un esempio della tensione DC impostata usata per intrappolare gli ioni. Le tensioni applicate per i binari interni possono compensare per il campo elettrico asimmetrico in direzione orizzontale per inclinare gli assi principali del potenziale totale nel piano trasversa. La frequenza di trappola assiale generata dall'insieme di tensione è stato 550 kHz. Clicca qui per visualizzare una versione più grande di questa figura.

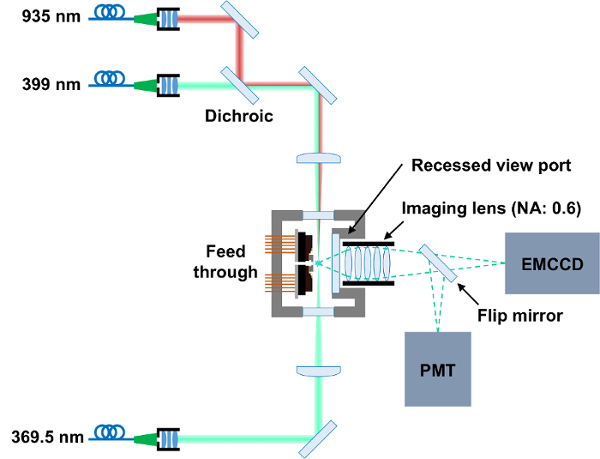

Figura 5: schematica dell'apparato ottico. Tre diodi laser sono allineati per sovrapporsi alla posizione di cattura. Finestra ad incasso della camera UHV consente l'imaging obiettivo di essere collocato più vicino possibile al chip in superficie. Un flip-specchio posizionato tra la lente imaging e il EMCCD consente il monitoraggio selettivo della fluorescenza dello ione utilizzando un tubo di fotone moltiplicato (PMT) o un EMCCD. Clicca qui per visualizzare una versione più grande di questa figura.

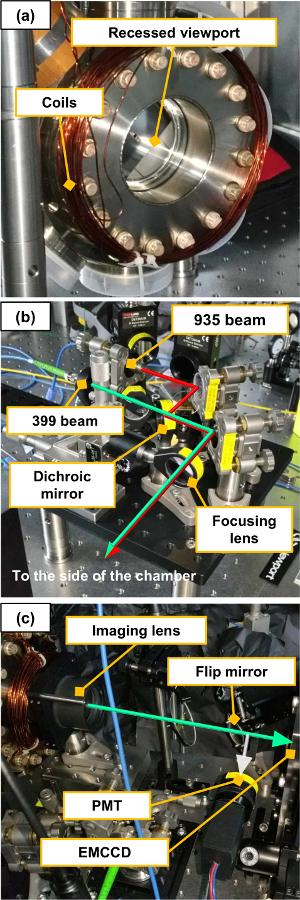

Figura 6: immagini dell'apparato ottico costruito. (un) A bobina è avvolta intorno finestra anteriore della camera per generare un campo magnetico, che può rompere i livelli di energia degenerati di ioni di itterbio. (b), l'installazione di ottica per sterzo i 399 nm e 935 nm travi. Le linee rosse e verdi indicano il percorso del fascio della 935 nm e 399 laser nm, rispettivamente. (c) la configurazione dell'imaging sistema, tra cui il flip-mirror, la lente di imaging, il EMCCD e il pagam. Il percorso della fluorescenza emessa da ioni intrappolati può essere determinato dal flip-specchio. Le frecce verdi e bianche indicano il percorso della fluorescenza quando monitorati dal EMCCD e la PMT, rispettivamente. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 7: risultati di fabbricazione della presa dello ione superficie. (un) Panoramica del layout del circuito integrato. (b) una vista ingrandita del layout del circuito integrato, che mostra il più elettrodi DC esterni. (c) una vista ingrandita del layout di chip, che mostra la fessura di caricamento. (d) una sezione trasversale vista della regione dell'intrappolamento prima di penetrare la fessura di caricamento. (e) una sezione trasversale vista della regione dell'intrappolamento dopo avere penetrato la fessura di caricamento. (f) A ingrandita vista di sezione trasversale del pilastro dell'ossido. I pilastri di ossido sono frastagliate pareti, e le lunghezze dello sbalzo non sono sufficienti, che è attribuito al tasso etch non uniforme del SiO2 in corrispondenza delle interfacce tra i separatamente depositato 3,5 µm di spessore SiO2 strati. (g), una vista dall'alto di un rilievo di wire-bonding di un elettrodo di DC. (h), A vista di sezione trasversale di una via. Profili inclinati dei pilastri ossido consentono il collegamento dell'elettrodo DC e lo strato di terra durante la deposizione dello strato sul fianco del pilastro ossido invece di riempimento la via i fori con un processo di elettrodeposizione. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 8: immagine An EMCCD di cinque ioni di Yb+ 174intrappolati sul chip trappola ionica microfabbricati. L'immagine della struttura dell'elettrodo superficiale trappola è stata presa separatamente, e le immagini dello ione intrappolato e degli elettrodi sono state combinate per chiarezza. La leggenda di intensità si applica solo ai pixel nella casella. La freccia spessa indica il percorso del fascio del laser 369.5 nm e le frecce sottili rappresentano i componenti x e z della quantità di moto del fotone. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 9: regolazione del potenziale assiale degli ioni intrappolati in una catena lineare. (un) sette ioni al centro della trappola. (b) gli ioni sono stati trasportati decine di micrometri. (c) la stringa di ioni spremuto in direzione assiale. Questa figura è meglio visto come un film, che è caricato separatamente. Clicca qui per visualizzare una versione più grande di questa figura.

Figura 10: Risultati sperimentali di oscillazioni di Rabi tra i | 0  e | 1

e | 1  Stati. | 0

Stati. | 0 è definito come il 2S1/2| F = 0, mF= 0

è definito come il 2S1/2| F = 0, mF= 0 statale dello ione 171Yb+ , e | 1

statale dello ione 171Yb+ , e | 1 è definito come il 2S1/2| F = 1, mF= 0

è definito come il 2S1/2| F = 1, mF= 0 stato. L'oscillazione di Rabi è indotta da un forno a microonde 12,6428-GHz. Bloch sfere sopra la trama mostrano gli stati quantici corrispondenti ai tempi differenti. Clicca qui per visualizzare una versione più grande di questa figura.

stato. L'oscillazione di Rabi è indotta da un forno a microonde 12,6428-GHz. Bloch sfere sopra la trama mostrano gli stati quantici corrispondenti ai tempi differenti. Clicca qui per visualizzare una versione più grande di questa figura.

Documento supplementare: Clicca qui per scaricare questo documento.

Discussione

Questa carta ha presentato un metodo per gli ioni di cattura mediante trappole ioniche superficie microfabbricati. La costruzione di un sistema di intercettazione degli ioni richiede esperienze in vari campi di ricerca, ma precedentemente non è stata descritta in dettaglio. Questa carta fornite procedure dettagliate per microfabricating un chip di trappola anche per quanto riguarda la costruzione di un apparato sperimentale per intrappolare gli ioni per la prima volta. Questa carta inoltre fornite procedure dettagliate per intrappolare gli ioni 174Yb+ e la sperimentazione con gli ioni intrappolati.

Un ostacolo significativo affrontato nelle procedure di microfabbricazione è la deposizione dello strato dielettrico, con uno spessore di oltre 10 µm. Durante il processo di deposizione dello strato dielettrico spesso, tensioni residue possono accumularsi, che può causare danni alla pellicola dielettrica o persino rompere il wafer. Per ridurre la tensione residua, che è generalmente alla compressione, un tasso di deposizione lento dovrebbe essere usato40. Nel nostro caso, una sollecitazione di compressione di 110,4 MPa è stata misurata con le condizioni di deposizione di 540 sccm di portata SiH4 gas, 140 W RF di potenza e 1,9 Torr di pressione allo spessore del film da 5 µm. Tuttavia, queste condizioni di processo forniscono solo un riferimento approssimativo, poiché queste condizioni possono variare significativamente per attrezzature diverse. Al fine di ridurre gli effetti dello stress accumulato, 3,5 µm di spessore SiO2 film erano depositati alternativamente su entrambi i lati del wafer nel metodo presentato. Lo spessore dello strato dielettrico può essere ridotta se una minore ampiezza di tensione RF e quindi una minore profondità di trappola è scelto. Tuttavia, una minore profondità di trappola conduce facilmente alla fuga degli ioni intrappolati, quindi la realizzazione di strati dielettrici più spessi, in grado di sopportare tensioni superiori di RF, è più desiderabile.

Ci sono alcune limitazioni per il metodo di fabbricazione presentato in questa carta. Le lunghezze degli strapiombi non sono sufficienti per nascondere completamente i fianchi dielettrici da ioni intrappolati, come mostrato in Figura 7f. Inoltre, le pareti laterali dei pilastri dell'ossido sono frastagliate, aumentando la superficie esposta dei fianchi dielettrici rispetto al pilastro verticale ossido. Ad esempio, nel caso il fianco della rotaia interna DC accanto allo slot di caricamento con una sporgenza di uniforme di 5 µm, si calcola che il 33% della superficie del dielettrica è esposto nella posizione di ioni intrappolati dei fianchi verticali. Nel caso di bordo frastagliato, oltre il 70% della zona di muro laterale è esposto. Questi risultati non ideali fabbricazione possono indurre ulteriori campi di dispersione dai dielettrici esposti, ma gli effetti non sono stati misurati quantitativamente. Tuttavia, il chip fabbricato come riportato sopra è stato utilizzato con successo in intrappolamento dello ione e gli esperimenti di manipolazione del qubit. Inoltre, il chip di trappola presentato in questa carta ha esposto i fianchi di silicio nei pressi della slot di caricamento. Ossido nativo può crescere sulle superfici di silicio e può provocare ulteriori campi di dispersione. Pertanto, si consiglia di proteggere il substrato di silicio con un ulteriore strato di metallo, come in33.

Per intercettare gli ioni 174Yb+ , le frequenze dei laser dovrebbero essere stabilizzate entro poche decine di MHz, e diversi metodi sono discussi in configurazioni avanzate38,41. Tuttavia, per l'installazione semplice discussa in questa carta, intrappolamento iniziale è possibile solo con la stabilizzazione mediante un misuratore di lunghezza d'onda.

Questa carta ha fornito un protocollo per intrappolare gli ioni di Yb+ 174utilizzando un chip di superficie trappola ionica microfabbricati. Anche se il protocollo per intrappolare gli ioni 171Yb+ non è discusso in particolare, la messa a punto sperimentale descritto in questo documento può essere utilizzato anche per intrappolare gli ioni 171Yb+ e per modificare lo stato del qubit di 171 Ioni di Yb+ per ottenere Rabi oscillazione risultati (mostrato in Figura 10). Questo può essere fatto aggiungendo diversi Modulatori ottici per l'output dei laser e utilizzando il programma di installazione di un forno a microonde, come descritto nel Documento complementare.

In conclusione, i metodi sperimentali e i risultati presentati in questa carta consente di sviluppare varie applicazioni di informazione quantistica utilizzando trappole ioniche superficiale.

Divulgazioni

Gli autori non hanno nulla a rivelare.

Riconoscimenti

Questa ricerca è stato parzialmente sostenuta da Ministero della scienza, ICT, e futuro pianificazione (MSIP), Corea del sud, sotto informazioni Technology Research Center (ITRC) supporto programma (IITP-2017-2015-0-00385) e l'ICT R & D programma (10043464, sviluppo di tecnologia di ripetitore di Quantum per l'applicazione di sistemi di comunicazione), sotto la supervisione dell'Istituto per informazioni & promozione di tecnologia di comunicazioni (IITP).

Materiali

| Name | Company | Catalog Number | Comments |

| photoresist used for 2-μm spin coating | AZ Materials | AZ7220 | Discontinued. Easily replaced by other alternative photoresist product. |

| photoresist used for 6-μm spin coating | AZ Materials | AZ4620 | Discontinued. Easily replaced by other alternative photoresist product. |

| ceramic chip carrier | NTK | IPKX0F1-8180BA | |

| epoxy compound | Epotek | 353ND | |

| Plasma enhanced chemical vapor deposition (PECVD) system | Oxford Instruments | PlasmaPro System100 | |

| Low pressure chemical vapor deposition (LPCVD) system | Centrotherm | E-1200 | |

| Furnace | Seltron | SHF-150 | |

| Sputter | Muhan Vacuum | MHS-1500 | |

| Manual aligner | Karl-Suss | MA-6 | |

| Deep Si etcher | Plasma-Therm | SLR-770-10R-B | |

| Inductive coupled plasma (ICP) etcher | Oxford Instruments | PlasmaPro System100 Cobra | |

| Reactive ion etching (RIE) etcher | Applied Materials | P-5000 | |

| Boundary element method (BEM) software | CPO Ltd. | Charged Particle Optics | |

| Single crystaline (100) silicon wafer | STC | 4SWP02 | 100 mm / (100) / P-type / SSP / 525±25 μm |

| metal tubes | Mcmaster-carr | 89935K69 | 316 Stainless Steel Tubing, 0.042" OD, 0.004" Wall Thickness |

| Yb piece | Goodfellow | YB005110 | Ytterbium wire, purity 99.9% |

| enriched 171Yb | Oak Ridge National Laboratory | Yb-171 | https://www.isotopes.gov/catalog/product.php?element=Ytterbium |

| tantalum foil | The Nilaco Corporation | TI-453401 | 0.25x130x100mm 99.5% |

| Kapton-insulated copper wire | Accu-glass | 18AWG (silver plated copper wire kapton insulted) | |

| residual gas analyzer (RGA) | SRS | RGA200 | |

| turbo pump | Agilent | Twistorr84 FS | |

| all-metal valve | KJL | manual SS All-Metal Angle Valves (CF flanged) | |

| Leak detector (used as a rough pump) | Varian | PD03 | |

| ion gauges | Agilent | UHV-24p | |

| ion pump | Agilent | VacIon Plus 20 | |

| NEG pump | SAES Getters | CapaciTorr D400 | |

| spherical octagon | Kimball Physics | MCF600-SphOct-F2C8 | |

| ZIF socket | Tactic Electronics | P/N 100-4680-002A | |

| multi-pin feedthroughs | Accu-Glass | 6-100531 | |

| 25 D-sub gender adapters | Accu-Glass | 104101 | |

| Recessed viewport | Culham Centre for Fusion Energy | 100CF 316LN+20.9 Re-Entrant 316 (Custom order) | Disc material: 60cv Fused Silica 4mm THK, TWE Lambda 1/10, 20/10 Scratch-Dig |

| Recessed viewport AR coating | LaserOptik | AR355nm/0-6° HT370-650nm/0-36° on UHV (Custom order) | AR coating was performed in the middle of the fabrication of the recessed viewport |

| Digital-analog converter | AdLink | PCIe-6216V-GL | |

| 369.5nm laser | Toptica | TA-SHG Pro | |

| 369.5nm laser | Moglabs | ECD004 + 370LD10 + DLC102/HC | |

| 399nm laser | Toptica | DL 100 | |

| 935nm laser | Toptica | DL 100 | |

| 369.5nm & 399nm optical fiber | Coherent | NUV-320-K1 | Patch cables are connectorized by Costal Connections. |

| 935nm optical fiber | GouldFiber Optics | PSK-000626 | 50/50 fiber beam splitter made of Corning HI-780 single mode fiber to combine 935nm and 638nm together. |

| Wavelength meter | High Finesse | WSU-2 | |

| temporary mirror | Thorlabs | PF10-03-P01 | |

| Dichroic mirror | Semrock | FF647-SDi01-25x36 | |

| 369.5nm & 399nm collimator | Micro Laser Systems | FC5-UV-T/A | |

| 935nm collimator | Schäfter + Kirchhoff | 60FC-0-M8-10 | |

| 369.5nm focusing lens | CVI | PLCX-25.4-77.3-UV-355-399 | Focal length: ~163mm @ 369.5nm |

| 399nm & 935nm focusing lens | CVI | PLCX-25.4-64.4-UV-355-399 | Focal length: ~137mm @ 399nm, ~143mm @ 935nm |

| imaging lens | Photon Gear | P/N 15470 | |

| 369.5nm bandpass filter | Semrock | FF01-370/6-25 | |

| 399nm bandpass filter | Semrock | FF01-395/11-25 | |

| IR filter | Semrock | FF01-650/SP-25 | |

| EMCCD camera | Andor Technology | DU-897U-CS0-EXF | |

| PMT | Hamamatsu | H10682-210 |

Riferimenti

- Wineland, D. J. Nobel Lecture: Superposition, entanglement, and raising Schrödinger's cat. Rev Mod Phys. 85 (3), 1103 (2013).

- Blatt, R., Wineland, D. Entangled states of trapped atomic ions. Nature. 453 (7198), 1008-1015 (2008).

- Leibfried, D., Blatt, R., Monroe, C., Wineland, D. Quantum dynamics of single trapped ions. Rev Mod Phys. 75 (1), 281 (2003).

- Paul, W. Electromagnetic traps for charged and neutral particles. Rev Mod Phys. 62 (3), 531 (1990).

- Rosenband, T., et al. Frequency ratio of Al+ and Hg+ single-ion optical clocks; metrology at the 17th decimal place. Science. 319 (5871), 1808-1812 (2008).

- Dawson, P. H. . Quadrupole mass spectrometry and its applications. , (2013).

- Ladd, T. D., Jelezko, F., Laflamme, R., Nakamura, Y., Monroe, C., O'Brien, J. L. Quantum computers. Nature. 464 (7285), 45-53 (2010).

- Monz, T., et al. Realization of a scalable Shor algorithm. Science. 351 (6277), 1068-1070 (2016).

- Debnath, S., Linke, N. M., Figgatt, C., Landsman, K. A., Wright, K., Monroe, C. Demonstration of a small programmable quantum computer with atomic qubits. Nature. 536 (7614), 63-66 (2016).

- Blatt, R., Roos, C. F. Quantum simulations with trapped ions. Nature Phys. 8 (4), 277-284 (2012).

- Kielpinski, D., Monroe, C., Wineland, D. J. Architecture for a large-scale ion-trap quantum computer. Nature. 417 (6890), 709-711 (2002).

- Moehring, D. L., et al. Design, fabrication and experimental demonstration of junction surface ion traps. New J Phys. 13 (7), 075018 (2011).

- Wright, K., et al. Reliable transport through a microfabricated X-junction surface-electrode ion trap. New J Phys. 15 (3), 033004 (2013).

- Amini, J. M., et al. Toward scalable ion traps for quantum information processing. New J Phys. 12 (3), 033031 (2010).

- Sterling, R. C., et al. Fabrication and operation of a two-dimensional ion-trap lattice on a high-voltage microchip. Nat Commun. 5, (2014).

- Kumph, M., et al. Operation of a planar-electrode ion-trap array with adjustable RF electrodes. New J Phys. 18 (2), 023047 (2016).

- Mielenz, M., et al. Arrays of individually controlled ions suitable for two-dimensional quantum simulations. Nat Commun. 7, (2016).

- Stick, D., Hensinger, W. K., Olmschenk, S., Madsen, M. J., Schwab, K., Monroe, C. Ion trap in a semiconductor chip. Nat Phys. 2 (1), 36-39 (2006).

- Harty, T. P., et al. High-fidelity preparation, gates, memory, and readout of a trapped-ion quantum bit. Phys Rev Lett. 113 (22), 220501 (2014).

- Cho, D., Hong, S., Lee, M., Kim, T. A review of silicon microfabricated ion traps for quantum information processing. Micro Nano Sys Lett. 3 (1), 1-12 (2015).

- Weidt, S., et al. Trapped-ion quantum logic with global radiation fields. Phys Rev Lett. 117 (22), 220501 (2016).

- Monroe, C., Kim, J. Scaling the ion trap quantum processor. Science. 339 (6124), 1164-1169 (2013).

- Brown, K. R., Kim, J., Monroe, C. Co-designing a scalable quantum computer with trapped atomic ions. npj Quantum Inf. 2, 16034 (2016).

- Lekitsch, B., et al. Blueprint for a microwave trapped-ion quantum computer. Science Adv. 3 (2), e1601540 (2017).

- Reichel, J., Vuletic, V. . Atom chips. , (2011).

- Ghosh, P. K., ed, ,. 1. s. t. . Ion Traps. , (1995).

- Wesenberg, J. H. Electrostatics of surface-electrode ion traps. Phys Rev A. 78 (6), 063410 (2008).

- House, M. G. Analytic model for electrostatic fields in surface-electrode ion traps. Phys Rev A. 78 (3), 033402 (2008).

- Hong, S., Lee, M., Cheon, H., Kim, T., Cho, D. I. Guidelines for Designing Surface Ion Traps Using the Boundary Element Method. Sensors. 16 (5), 616 (2016).

- Allcock, D. T. C., et al. Implementation of a symmetric surface-electrode ion trap with field compensation using a modulated Raman effect. New J Phys. 12 (5), 053026 (2010).

- Chiaverini, J., et al. Surface-electrode architecture for ion-trap quantum information processing. Quantum Inf Comput. 5 (6), 419-439 (2005).

- Allcock, D. T. C., et al. Heating rate and electrode charging measurements in a scalable, microfabricated, surface-electrode ion trap. Appl Phys B. 107 (4), 913-919 (2012).

- . Demonstration of a microfabricated surface electrode ion trap Available from: https://arxiv.org/abs/1008.0990 (2010)

- Allcock, D. T. C., et al. Reduction of heating rate in a microfabricated ion trap by pulsed-laser cleaning. New J Phys. 13 (12), 123023 (2011).

- Mount, E., et al. Single qubit manipulation in a microfabricated surface electrode ion trap. New J Phys. 15 (9), 093018 (2013).

- Siverns, J. D., Simkins, L. R., Weidt, S., Hensinger, W. K. On the application of radio frequency voltages to ion traps via helical resonators. Appl Phys B. 107 (4), 921-934 (2012).

- Kleinert, M., Dahl, M. E. G., Bergeson, S. Measurement of the Yb I 1S0−1P1 transition frequency at 399 nm using an optical frequency comb. Phys Rev A. 94 (5), 052511 (2016).

- Olmschenk, S., Younge, K. C., Moehring, D. L., Matsukevich, D. N., Maunz, P., Monroe, C. Manipulation and detection of a trapped Yb+ hyperfine qubit. Phys Rev A. 76 (5), 052314 (2007).

- Sansonetti, J. E., Martin, W. C., Young, S. L. . Handbook of Basic Atomic Spectroscopic Data. , (2013).

- Kern, W. . Thin film processes II. , (2012).

- Streed, E. W., Weinhold, T. J., Kielpinski, D. Frequency stabilization of an ultraviolet laser to ions in a discharge. Appl Phys Lett. 93 (7), 071103 (2008).

Ristampe e Autorizzazioni

Richiedi autorizzazione per utilizzare il testo o le figure di questo articolo JoVE

Richiedi AutorizzazioneThis article has been published

Video Coming Soon