Method Article

Scrittura e bassa temperatura Caratterizzazione di nanostrutture di ossido

In questo articolo

Riepilogo

Oxide nanostructures provide new opportunities for science and technology. The interfacial conductivity between LaAlO3 and SrTiO3 can be controlled with near-atomic precision using a conductive atomic force microscopy technique. The protocol for creating and measuring conductive nanostructures at LaAlO3/SrTiO3 interfaces is demonstrated.

Abstract

Oxide nanoelectronics is a rapidly growing field which seeks to develop novel materials with multifunctional behavior at nanoscale dimensions. Oxide interfaces exhibit a wide range of properties that can be controlled include conduction, piezoelectric behavior, ferromagnetism, superconductivity and nonlinear optical properties. Recently, methods for controlling these properties at extreme nanoscale dimensions have been discovered and developed. Here are described explicit step-by-step procedures for creating LaAlO3/SrTiO3 nanostructures using a reversible conductive atomic force microscopy technique. The processing steps for creating electrical contacts to the LaAlO3/SrTiO3 interface are first described. Conductive nanostructures are created by applying voltages to a conductive atomic force microscope tip and locally switching the LaAlO3/SrTiO3 interface to a conductive state. A versatile nanolithography toolkit has been developed expressly for the purpose of controlling the atomic force microscope (AFM) tip path and voltage. Then, these nanostructures are placed in a cryostat and transport measurements are performed. The procedures described here should be useful to others wishing to conduct research in oxide nanoelectronics.

Introduzione

Eterostrutture Ossido 1-5 mostrano una notevole varietà di fenomeni fisici emergenti che sono sia scientificamente interessante e potenzialmente utile per le applicazioni 4. In particolare, l'interfaccia tra LaAlO 3 (LAO) e SrTiO 3 (STO) 6 può esibire isolante, conduzione, superconduttori 7, ferroelettrici come 8 e 9 comportamento ferromagnetico. Nel 2006, Thiel et al hanno dimostrato 10 che c'è una transizione netta isolante-metallo come lo spessore dello strato LAO viene aumentata, con uno spessore critico di 4 celle unitarie (4uc). Successivamente è stato dimostrato che le strutture 3uc-LAO/STO presentano una transizione isteresi che può essere controllato localmente con un conduttore microscopio a forza atomica (AFM-c) sonda 11.

Le proprietà delle interfacce ossido come LaAlO 3/3 SrTiO dipendono dalla assenza o presenza di condurreelettroni all'interfaccia. Questi elettroni possono essere controllate utilizzando migliori elettrodi di gate 12,13, schiena Portone 10, superficie adsorbati 14 strati ferroelettrici 15,16 e c-AFM litografia 11. Una caratteristica unica di c-AFM litografia è che molto piccole caratteristiche nanoscala possono essere creati.

Gating top elettrico, in combinazione con la reclusione bidimensionale, viene spesso utilizzato per creare punti quantici di semiconduttori III-V 17. In alternativa, nanofili semiconduttori quasi-unidimensionali possono essere gated elettricamente dalla vicinanza. I metodi per produrre queste strutture sono in termini di tempo e generalmente irreversibile. Al contrario, la tecnica litografia c-AFM è reversibile, nel senso che una nanostruttura può essere creato per un esperimento, e poi "cancellata" (simile ad una lavagna). Generalmente, scrittura c-AFM viene eseguita con tensioni positive applicate alla punta AFM, mentre, cancellandoviene eseguita utilizzando tensioni negative. Il tempo necessario per creare una particolare struttura dipende dalla complessità del dispositivo, ma è di solito meno di 30 min; maggior parte del tempo viene speso cancellando la tela. La risoluzione spaziale tipica è di circa 10 nanometri, ma con la sintonizzazione corretta caratteristiche piccolo come 2 nanometri possono essere creati 18.

Una descrizione dettagliata della procedura di fabbricazione su scala nanometrica segue. Il dettaglio fornito qui dovrebbe essere sufficiente a consentire esperimenti simili da eseguire da ricercatori interessati. Il metodo qui descritto presenta numerosi vantaggi rispetto agli approcci litografiche tradizionali utilizzati per creare nanostrutture elettronici nei semiconduttori.

Il metodo di litografia c-AFM qui descritto è parte di una classe molto più ampia di iniziative litografia a base di scansione a sonda, tra cui la scansione di ossidazione anodica 19, dip-pen nanolitografia 20, patterning piezoelettrico21, e così via. La tecnica c-AFM qui descritto, insieme con l'uso di interfacce ossido nuovi, può produrre alcune delle strutture elettroniche massima precisione con una varietà senza precedenti di proprietà fisiche.

Protocollo

1. Ottenere LAO / STO Eterostrutture

- Ottenere un eterostruttura ossido costituito da 3.4 celle elementari di LAO coltivati da deposizione laser pulsata su TiO substrati STO 2-terminati. Dettagli di crescita campione sono descritti in rif. 22.

2. Fotolitografica Trattamento dei campioni

Creare contatti elettrici per l'interfaccia LAO / STO, con cuscinetti di legame per tele di cablaggio ad un chip carrier. Le singole fasi di lavorazione sono descritte in dettaglio di seguito.

- Spin fotosensibile

- Spin photoresist sui campioni a 600 rpm per 5 secondi, poi a 4000 rpm per 30 sec. Lo strato fotosensibile sarà spessore di circa 2 micron. Cuocere i campioni a 95 ° C per 1 min.

- Esporre photoresist utilizzando un allineatore maschera con luce 320 nm per 100 sec con una dose di 5 mW / cm 2.

- Sviluppare il photoresist in sviluppatore fotosensibile for 1 min.

- Ion fresatura

- Utilizzare un mulino ioni Ar + per rimuovere i 15 nm di materiale (LAO e STO) nelle zone non coperte da photoresist. Porre i campioni con un angolo di 22,5 ° rispetto alla direzione perpendicolare al fascio di ioni Ar + in entrata. Se la velocità di attacco Ar + non è tarato, eseguire una corsa di taratura per garantire la corretta quantità di materiale viene rimosso. Determinare la profondità di incisione con AFM o profilmetry equivalente.

- DC sputtering di Ti e Au

- Cassetta 4 nm Ti, poi 25 nm Au sui campioni in modo che l'Au fa contatto elettrico con lo strato STO esposto. La pressione sputtering è nell'intervallo 2-6 x 10 -7 Torr, e lo sputtering avviene con il campione a temperatura ambiente. Pre-polverizzazione catodica Ti per 10 min con otturatore chiuso a 100 W, poi otturatore aperto e polverizzazione catodica per 20 secondi a 100 W. Al termine, immediatamente pre-sputter Au per 1 min a 50 W poi polverizzare Au per 30 sec per i campioni a 50 W. CaliBrate il tempo per produrre gli spessori Ti e Au desiderati.

- Lift-off

- Utilizzare lavaggio ultrasonico Acetone / IPA per rimuovere photoresist dalla superficie dei campioni.

- Secondo strato

- Un secondo processo litografico, escluso il punto 4 (ie., Escludendo la fresatura di ioni), viene utilizzato per creare i collegamenti dei cavi d'oro ai singoli pad legame. I due modelli devono essere ben allineate per garantire che essi non producono cortocircuiti.

- Pulizia al plasma.

- Un IPC Barrel Etcher viene utilizzato per rimuovere il photoresist residuo nella trincea pattern. Lo strumento utilizzato al 100 W e 1 Torr argon per 1 min

3. Wire James Bond un campione prepararsi per la scrittura

- Montare il campione LAO / STO in un chip carrier (Figura 2A) con 28 pin disponibili.

- Struttura legame Wire

NOTA: Utilizzare un bonder filo per fare c elettricaollegamenti tra i rilievi di legame sul campione e il chip carrier. Attaccare 1 mil (25 micron) fili d'oro tra i contatti elettrici e il chip carrier. Scrivi nanostrutture

4. Scrivere Nanostrutture

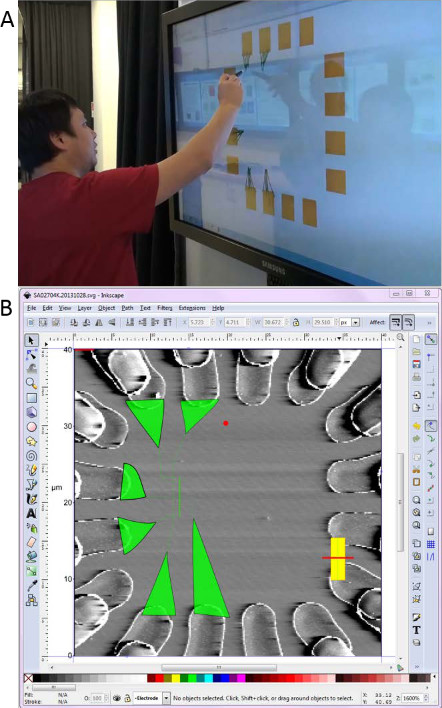

- Creare uno schizzo informale della nanostruttura conduttrice (Figura 3A).

- Aprire le Scalable Vector Graphics (SVG), montaggio (Figura 3B).

- Utilizzare un modello o definire le dimensioni della finestra in base a quella dell'immagine AFM.

- Caricare l'immagine AFM del campione nell'editor SVG.

- Creare elementi di nanostrutture sovrapposte l'immagine AFM su.

- Caricare il file SVG nel programma nanolitografia.

- Eseguire il software di litografia per creare una nanostruttura conduttrice.

- Suggerimento Utilizzare V = +10 V per creare nanostrutture, e mancia V = -10 V per cancellare nanostrutture.

- Spostare la punta c-AFM ad una velocità compresa tra 200 nm / sec a 2 micron / sec.

5. Raffreddare dispositivo e prendere le misure

- Spegnere tutte le luci bianche e utilizzare filtri rosso / sorgenti luminose.

- Estrarre il campione dal sistema AFM.

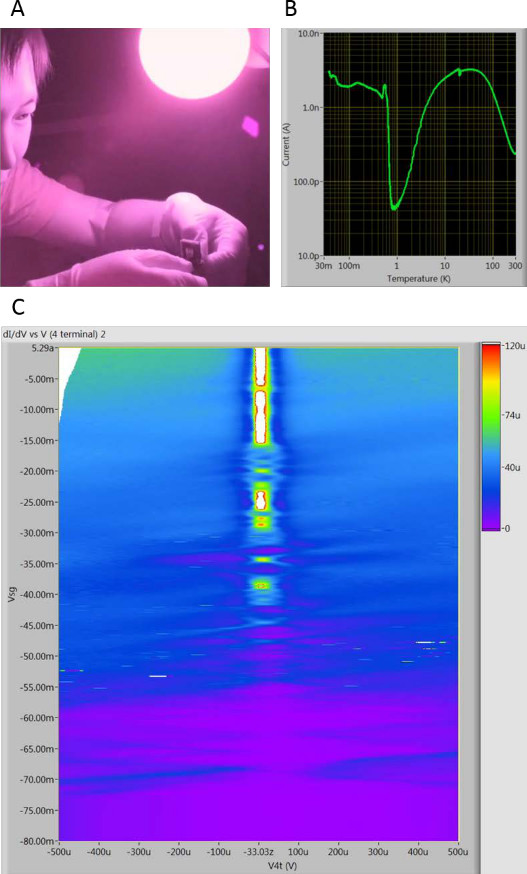

- Caricare il campione in frigorifero diluizione (A).

- Misurare la resistenza in funzione della temperatura (B) come il campione viene raffreddato.

- Misurare le proprietà di trasporto a basse temperature (C).

Risultati

I risultati mostrati qui sono rappresentative del comportamento dei trasporti che può essere esposto da questa classe di nanostrutture, ed è stato descritto altrove in dettaglio 23-26. In questo esempio, una cavità nanofili è stato costruito (figura 4) da una eterostruttura LAO cella 3,3 unità / STO. Percorsi conduttivi (in verde) sono tipicamente 10 nm di larghezza, come determinato dal nanowire "tagliando" esperimenti 11. La velocità di punta e la tensione per ogni segmento è configurabile in modo indipendente dal pannello di litografia anteriore (Figura 4B), così come la velocità di scrittura di punta. "Elettrodi virtuali" che si interfacciano con i contatti interfacciali assicurano che vi sia una connessione elettrica altamente conduttivo sulle nanostrutture.

Dopo la nanostruttura è scritto, è trasferito al frigorifero diluizione. L'esposizione alla luce o al di sotto di 550 nm produrrà photoconduction indesiderato, quindi è important trasferire il dispositivo al buio o con l'ausilio di un rosso "camera oscura" luce (Figura 5A). I collegamenti elettrici devono essere effettuate a temperatura ambiente, e come con la maggior parte delle nanostrutture di semiconduttori, grande attenzione dovrebbero essere prese quando si cambia i collegamenti elettrici a temperature criogeniche. Se i dispositivi vengono sottoposti a scariche elettrostatiche, molto probabilmente diventerà isolante. Sorprendentemente, la funzionalità può essere recuperato da "bicicletta" la temperatura di 300 K e raffreddamento di nuovo.

Durante cooldown, è di routine per monitorare la resistenza a due terminali, e anche la resistenza a quattro terminali, in funzione della temperatura. Per queste misure una tensione alternata (tipicamente ~ 1 mV) viene applicato ad una bassa frequenza (<10 Hz) a uno degli elettrodi, mentre la corrente alternata è misurata con un amplificatore di transimpedenza. Lock-in demodulazione e il filtraggio viene eseguita utilizzando un amplificatore lock-in casa-sviluppato. Il cu acrrent viene monitorata in funzione della temperatura (Figura 5B).

Una volta che il dispositivo viene raffreddata alla temperatura di base del frigorifero diluizione (50 mK), misure di trasporto a quattro terminali vengono eseguite (Figura 5C). Per le misurazioni di corrente viene prelevato attraverso il canale principale del dispositivo, mentre la tensione ai capi del dispositivo viene misurata simultaneamente. Invece di misurare con un amplificatore lock-in, un pieno corrente-tensione (IV) traccia viene misurata. Questo metodo contiene più informazioni e la conduzione differenziale può essere calcolato tramite differenziazione numerica. Per il particolare dispositivo, la conduzione differenziale è misurata in funzione del lato sg-gate tensione V. Questa porta consente il potenziale chimico del dispositivo da modificare. Il trasporto attraverso il dispositivo mostra una forte dipendenza non monotona, indicando regioni in cui Coulomb blocco avviene per i valori più piccoli, e strong la superconduttività per i più grandi valori di V sg. Dettagli sulla interpretazione fisica per questa classe di dispositivi saranno descritte altrove.

.. Figura 1, fasi di lavorazione fotolitografiche Fase 1: centrifuga fotosensibile. Fase 2: esporre photoresist utilizzando la maschera allineatore. Fase 3: sviluppare fotosensibile. Fase 4: fresatura di ioni. Fase 5: DC sputtering a depositare Ti e Au. Fase 6: lift-off. Fase 7: depositare il secondo strato. Fase 8: pulizia plasma.

Figura 2. Immagini di lithographically fantasia eterostrutture LAO / STO. (A) Immagine che mostra 5mm x 5mm campione filo legato a un chip carrier. (B) Ottico d'immagine che mostra i rilievi di legame e una delle tele. (C) Close-up di un'unica tela. cliccate qui per vedere una versione più grande di questa figura.

Figura 3. (A) progettazione informale dei LAO / STO nanostruttura. (B) disposizione precisa di nanostrutture utilizzando un open-source di grafica vettoriale scalabile (SVG) montaggio.

Figura 4. (A) litografia pannello anteriore per c-AFM patterning. (B) la posizione e la tensione di punta c-AFM Screenshot dal simulatore 3D che mostra.w.jove.com/files/ftp_upload/52058/52058fig4large.jpg "target =" _blank "> Clicca qui per vedere una versione più grande di questa figura.

Figura 5. (A) LAO / STO nanostruttura essendo inserito in diluizione frigorifero. (B) Controllo di resistenza campione viene raffreddato da 300 K a 50 mK. (C) Controllo di conduttanza differenziale a quattro terminali di dispositivo in funzione della Vsg tensione cancello laterale e tensione ai capi del dispositivo (V4T). Grafico di intensità visualizzato in unità di siemens (S), e le tensioni sono visualizzati in unità di volt (V).

Discussione

Successful creation of nanostructures depends on several critical steps. It is important that the LAO/STO samples are grown with a thickness that is known to be at the boundary between the insulating and conductive phase. (Details of sample growth fall outside the scope of this paper, but are crucial for overall success.) Second, it is important to have relative humidity within the range 25-45% for successful c-AFM writing. Values below 25% are unlikely to produce conductive nanostructures, while too high humidity will generally produce uncontrollably large features. Also, temperature control of the AFM is important if the c-AFM tip needs to achieve precise registry over long periods of time. Once the nanostructures are created, they must be placed in a vacuum environment if experiments lasting longer than a few hours are to be performed. For the experiments described here, the structure is created and within minutes transferred to a vacuum environment.

It is recommend before writing that a “writing test” be performed on all relevant electrodes. In such a test, two virtual electrodes are first created, and a single nanowire is written while simultaneously monitoring the conductance. A similar test of erasure can be performed by “cutting” the nanowire shortly afterwards. If the nanostructure is decaying rapidly, the issue is most likely due either to the interfacial contacts or the canvas itself. To distinguish between these two effects, a four-terminal measurement of the conductance should be performed, and the two-terminal conductance should be compared with the four-terminal conductance as a function of time. If the two-terminal conductance is decaying more rapidly than the four-terminal conductance, then the issue is related to the electrical contacts to the interface. If the four-terminal conductance is decaying at a comparable rate, then most likely the canvas is not suitable and should be replaced.

There are natural limitations of the current method for creating nanostructures. Specifically, the writing speed for the smallest devices is limited to a few hundred nanometers per second. Speeds far above that value lead to unpredictable results. Use of parallel writing techniques are possible27,28, but are not highly developed and have their own drawbacks. The size of nanostructures that can be created is naturally limited by the scan range of the AFM being used. A high-quality AFM with closed-loop feedback in the two scan directions is highly recommended. Tracking of point-like objects on the sample surface should be performed to monitor temporal drift of the sample.

Once creation of conductive nanostructures at oxide interfaces has been mastered, there are a wide range of experimental directions that can be explored. Using this technique, a wide variety of nanostructures and devices have already been demonstrated, including nanowires18, tunnel barriers29, rectifying junctions30, field-effect transistors18, single-electron transistors31, superconducting nanowires32, nanoscale optical detectors33, and nanoscale THz emitters and detectors34.

Divulgazioni

The authors have nothing to disclose.

Riconoscimenti

The long-standing collaboration with Chang-Beom Eom at the University of Wisconsin-Madison, who provided the LAO/STO samples, is gratefully acknowledged. Video editing assistance from Christopher Solis is greatly appreciated. This work is supported by NSF (DMR-1104191, DMR-1124131), ARO (W911NF-08-1-0317), and AFOSR (FA9550-10-1-0524, FA9550-12-1-0268, FA9550-12-1-0057).

Materiali

| Name | Company | Catalog Number | Comments |

| Equipment | |||

| Contact Aligner | Karl-Suss | MA6 | |

| Spinner | Solitec | 5110C | |

| Ion Mill | Commonwealth Scientific | 8C | |

| Sputtering System | Leybold-Heraeus | Z-650 | |

| Barrel Etcher | Branson/IPC | 3000C | |

| Wire Bonder | Westbond | 7700E | |

| AFM | Asylum Research | MFP-3D | |

| Dilution Refrigerator | Quantum Design | P850 | |

| Ultrasonic Wash Machine | Fisher Scientific | 15-335-6 | |

| Current Amplifier | Femto | DLPCA-200 | |

| Materials | |||

| LaAlO3/SrTiO3 | Prof. Chang-Beom Eom | 5 mm x 1 mm with ~3.4 unit cells of LAO (See Reference 18) | |

| Photoresist | AZ Electronic Materials | P4210 | |

| Developer | AZ Electronic Materials | 400K | |

| Acetone | Fisher Scientific | A929SK-4 | |

| Isopropyl Alcohol | Fisher Scientific | A459-1 | |

| Deionized Water | Fisher Scientific | 23-290-065 | |

| Gold Wire | DuPont | 5771 | 1 mm diameter |

| Chip Carrier | NTK Technologies | IRK28F1-5451D |

Riferimenti

- Sulpizio, J. A., Ilani, S., Irvin, P., Levy, J. i. . Annual Review of Materials Research, in press. , (2014).

- Mannhart, J., Blank, D. H. A., Hwang, H. Y., Millis, A. J., Triscone, J. M. Two-Dimensional Electron Gases at Oxide Interfaces. Mrs Bulletin. 33, 1027-1034 (2008).

- Zubko, P., Gariglio, S., Gabay, M., Ghosez, P., Triscone, J. -. M., Langer, J. S. Annual Review of Condensed Matter Physics. Interface Physics in Complex Oxide Heterostructures. , 141-165 (2011).

- Bogorin, D. F., Irvin, P., Cen, C., Levy, J. i., Tsymbal, E. Y., Dagotto, E. R. A., Chang-Beom, E., Ramesh, R. . Multifunctional Oxide Heterostructures. 13, (2012).

- Granozio, F. M., Koster, G., Rijnders, G. Functional Oxide Interfaces. MRS Bulletin. 38, 1017-1023 (2013).

- Ohtomo, A., Hwang, H. Y. A high-mobility electron gas at the LaAlO3/SrTiO3 heterointerface. Nature. 427, 423-426 (2004).

- Reyren, N., et al. Superconducting interfaces between insulating oxides. Science. 317, 1196-1199 (2007).

- Bark, C. W., et al. Switchable Induced Polarization in LaAlO3/SrTiO3 Heterostructures. Nano Letters. 12, 1765-1771 (2012).

- Brinkman, A., et al. Magnetic effects at the interface between non-magnetic oxides. Nature Materials. 6, 493-496 (2007).

- Thiel, S., Hammerl, G., Schmehl, A., Schneider, C. W., Mannhart, J. Tunable quasi-two-dimensional electron gases in oxide heterostructures. Science. 313, 1942-1945 (2006).

- Cen, C., et al. Nanoscale control of an interfacial metal-insulator transition at room temperature. Nature Materials. 7, 298-302 (2008).

- Singh-Bhalla, G., et al. Built-in and induced polarization across LaAlO3/SrTiO3 heterojunctions. Nature Physics. 7, 80-86 (2011).

- Li, L., et al. Very Large Capacitance Enhancement in a Two-Dimensional Electron System. Science. 332, 825-828 (2011).

- Xie, Y., Hikita, Y., Bell, C., Hwang, H. Y. Control of electronic conduction at an oxide heterointerface using surface polar adsorbates. Nature Communications. 2, 494 (2011).

- Bark, C. W., et al. Tailoring a two-dimensional electron gas at the LaAlO3/SrTiO3 (001) interface by epitaxial strain. PNAS. 108, 4720-4724 (2011).

- Tra, V. T., et al. . Adv Mater. 25, 3357-3364 (2013).

- Cronenwett, S. M., Oosterkamp, T. H., Kouwenhoven, L. P. A Tunable Kondo Effect in Quantum Dots. Science. 281, 540-544 (1998).

- Cen, C., Thiel, S., Mannhart, J., Levy, J. Oxide Nanoelectronics on Demand. Science. 323, 1026-1030 (2009).

- Kalinin, S. V., Gruverman, A. . Scanning probe microscopy: electrical and electromechanical phenomena at the nanoscale. 1, (2007).

- Piner, R. D., Zhu, J., Xu, F., Hong, S. H., Mirkin, C. A. 'Dip-pen' nanolithography. Science. 283, 661-663 (1999).

- Ahn, C. H., et al. Nonvolatile Electronic Writing of Epitaxial Pb(Zr0.52Ti0.48)O3/SrRuO3 Heterostructures. Science. 276, 1100-1103 (1997).

- Bi, F., et al. 'Water-cycle' mechanism for writing and erasing nanostructures at the LaAlO3/SrTiO3 interface. Applied Physics Letters. 97, 173110 (2010).

- Cheng, G., et al. Anomalous Transport in Sketched Nanostructures at the LaAlO3/SrTiO3 Interface. Phys Rev X. 3, 011021 (2013).

- Veazey, J. P., et al. Nonlocal current-voltage characteristics of gated superconducting sketched oxide nanostructures. Europhys Lett. 103, 57001 (2013).

- Veazey, J. P., et al. Oxide-based platform for reconfigurable superconducting nanoelectronics. Nanotechnology. 24, 375201 (2013).

- Irvin, P., et al. Anomalous High Mobility in LaAlO3/SrTiO3 Nanowires. Nano Letters. 13, 364-368 (2013).

- Salaita, K., et al. Massively Parallel Dip–Pen Nanolithography with 55 Two-Dimensional Arrays. Angewandte Chemie. 118, 7378-7381 (2006).

- Li, S., et al. Parallel Conductive-AFM Lithography on LaAlO3/SrTiO3 Interfaces. Ieee T Nanotechnol. 12, 518-520 (2013).

- Cen, C., Bogorin, D. F., Levy, J. Thermal activation and quantum field emission in a sketch-based oxide nanotransistor. Nanotechnology. 21, 475201 (2010).

- Bogorin, D. F., et al. Nanoscale rectification at the LaAlO3/SrTiO3 interface. Applied Physics Letters. 97, 013102 (2010).

- Cheng, G., et al. Sketched Oxide Single-Electron Transistor. Nature Nanotech. 6, 343-347 (2011).

- Joshua, A., Ruhman, J., Pecker, S., Altman, E., Ilani, S. Gate-tunable polarized phase of two-dimensional electrons at the LaAlO3/SrTiO3 interface. PNAS. 110, 9633 (2013).

- Irvin, P., et al. Rewritable Nanoscale Oxide Photodetector. Nature Photon. 4, 849-852 (2010).

- Ma, Y., et al. Broadband Terahertz Generation and Detection at 10 nm Scale. Nano Letters. 13, 2884-2888 (2013).

Ristampe e Autorizzazioni

Richiedi autorizzazione per utilizzare il testo o le figure di questo articolo JoVE

Richiedi AutorizzazioneThis article has been published

Video Coming Soon