A subscription to JoVE is required to view this content. Sign in or start your free trial.

Method Article

الحساب النظري والتحقق التجريبي لتقليل الخلع في طبقات الجرمانيوم فوق المحورية مع فراغات نصف أسطوانية على السيليكون

In This Article

Summary

تم اقتراح الحساب النظري والتحقق التجريبي لتقليل كثافة خلع الخيوط (TD) في طبقات الجرمانيوم الفوقية مع فراغات نصف أسطوانية على السيليكون. يتم تقديم الحسابات القائمة على تفاعل TDs والسطح عبر قوة الصورة وقياسات TD وملاحظات المجهر الإلكتروني النافذ ل TDs.

Abstract

كان تقليل كثافة خلع الخيوط (TDD) في الجرمانيوم الفوقي (Ge) على السيليكون (Si) أحد أهم التحديات لتحقيق دوائر ضوئية متكاملة متجانسة. تصف هذه الورقة طرق الحساب النظري والتحقق التجريبي لنموذج جديد للحد من TDD. تصف طريقة الحساب النظري انحناء خلع الخيوط (TDs) بناء على تفاعل TDs وأسطح النمو غير المستوية للنمو الفوقي الانتقائي (SEG) من حيث قوة صورة الخلع. يكشف الحساب أن وجود فراغات على أقنعة SiO2 يساعد على تقليل TDD. يتم وصف التحقق التجريبي بواسطة الجرمانيوم (Ge) SEG ، باستخدام طريقة ترسيب بخار كيميائي عالي الفراغ وملاحظات TD ل Ge المزروع عن طريق النقش والمجهر الإلكتروني المقطعي (TEM). يقترح بشدة أن تخفيض TDD سيكون بسبب وجود فراغات شبه أسطوانية فوق أقنعة SiO2 SEG ودرجة حرارة النمو. للتحقق التجريبي ، تتشكل طبقات Ge الفوقية مع الفراغات شبه الأسطوانية نتيجة لطبقات SEG من Ge واندماجها. تقوم TDDs التي تم الحصول عليها تجريبيا بإعادة إنتاج TDDs المحسوبة بناء على النموذج النظري. تكشف ملاحظات TEM المستعرضة أن كلا من إنهاء وتوليد TDs يحدث في فراغات شبه أسطوانية. تكشف ملاحظات TEM لعرض الخطة عن سلوك فريد من نوعه ل TDs في Ge مع فراغات نصف أسطوانية (على سبيل المثال ، يتم ثني TDs لتكون موازية لأقنعة SEG والركيزة Si).

Introduction

اجتذب Epitaxial Ge on Si اهتمامات كبيرة كمنصة جهاز فوتوني نشطة حيث يمكن ل Ge اكتشاف / إصدار الضوء في نطاق الاتصالات الضوئية (1.3-1.6 ميكرومتر) وهو متوافق مع تقنيات معالجة Si CMOS (أشباه الموصلات المعدنية التكميلية). ومع ذلك ، نظرا لأن عدم تطابق الشبكة بين Ge و Si يصل إلى 4.2٪ ، تتشكل خلع الخيوط (TDs) في طبقات Ge الفوقية على Si بكثافة ~ 109 / سم2. يتدهور أداء الأجهزة الضوئية Ge بواسطة TDs لأن TDs تعمل كمراكز توليد حاملة في أجهزة الكشف الضوئي Ge (PDs) والمعدلات (MODs) ، وكمراكز إعادة تركيب الناقل في ثنائيات الليزر (LDs). في المقابل ، سيزيدون تيار التسرب العكسي (تسرب J) في PDs و MODs1،2،3 ، وتيار العتبة (Jth) في LDs4،5،6.

تم الإبلاغ عن محاولات مختلفة لتقليل كثافة TD (TDD) في Ge on Si (الشكل التكميلي 1). يحفز التلدين الحراري حركة TDs مما يؤدي إلى تقليل TDD ، عادة إلى 2 × 107 / سم2. العيب هو الاختلاط المحتمل بين Si و Ge وانتشار المنشطات في Ge مثل الفوسفور7،8،9 (الشكل التكميلي 1 أ). تزيد الطبقة العازلة المتدرجة SiGe 10،11،12 من السماكات الحرجة وتمنع توليد المواد الصلبة الذائبة مما يؤدي إلى تقليل TDD ، عادة إلى 2 × 10 6 / سم2. العيب هنا هو أن المخزن المؤقت السميك يقلل من كفاءة اقتران الضوء بين أجهزة Ge وأدلة موجات Si تحتها (الشكل التكميلي 1 ب). ملائمة نسبة العرض إلى الارتفاع (ART) 13،14،15 هي طريقة نمو فوقي انتقائي (SEG) وتقلل من TDs عن طريق محاصرة TDs في الجدران الجانبية لخنادق SiO 2 السميكة ، عادة إلى <1 × 10 6 / سم 2. تستخدم طريقة ART قناع SiO 2 سميك لتقليل TDD في Ge على أقنعة SiO2 ، والتي تقع أعلى بكثير من Si ولها نفس العيب (الشكل التكميلي 1b ، 1c). يشبه نمو Ge على بذور عمود Si والتلدين16،17،18 طريقة ART ، مما يتيح محاصرة TD بنسبة عرض إلى ارتفاع عالية نمو Ge ، إلى <1 × 10 5 / سم2. ومع ذلك ، فإن التلدين بدرجة حرارة عالية للاندماج Ge له نفس العيوب في الشكل التكميلي 1a-c (الشكل التكميلي 1 د).

لتحقيق نمو فوقي منخفض TDD Ge على Si خال من عيوب الطرق المذكورة أعلاه ، اقترحنا تخفيض TDD الناجم عن الالتحام 19,20 بناء على الملاحظتين الرئيسيتين التاليتين اللتين تم الإبلاغ عنهما حتى الآن في نمو SEG Ge7،15،21،22،23 : 1) تنحني TDs لتكون طبيعية لأسطح النمو (يتم ملاحظتها بواسطة المجهر الإلكتروني النافذ المستعرض (TEM)) ، و 2) يؤدي اندماج طبقات SEG Ge إلى تكوين فراغات نصف أسطوانية فوق أقنعة SiO2.

لقد افترضنا أن TDs عازمة بسبب قوة الصورة من سطح النمو. في حالة Ge على Si ، تولد قوة الصورة 1.38 GPa و 1.86 GPa إجهادات القص للخلع اللولبي وخلع الحواف على مسافات 1 نانومتر بعيدا عن الأسطح الحرة ،على التوالي 19. إجهادات القص المحسوبة أكبر بكثير من إجهاد بيرلز البالغ 0.5 جيجا باسكال المبلغ عنه لخلع 60 درجة في Ge24. يتنبأ الحساب بانخفاض TDD في طبقات Ge SEG على أساس كمي وهو يتفق جيدا مع نمو SEGGe 19. يتم إجراء ملاحظات TEM ل TDs لفهم سلوكيات TD في نمو SEG Ge المقدم على Si20. إن تقليل TDD الناجم عن قوة الصورة خال من أي تلدين حراري أو طبقات عازلة سميكة ، وبالتالي فهو أكثر ملاءمة لتطبيق الجهاز الضوئي.

في هذه المقالة ، نصف طرقا محددة للحساب النظري والتحقق التجريبي المستخدم في طريقة تخفيض TDD المقترحة.

Protocol

1. إجراء الحساب النظري

- حساب مسارات TD. في الحساب ، افترض أن أقنعة SEG رقيقة بما يكفي لتجاهل تأثير ART على تقليل TDD.

- تحديد أسطح النمو والتعبير عنها بالمعادلة (المعادلات). على سبيل المثال ، عبر عن التطور الزمني لمقطع عرضي دائري الشكل لطبقة SEG Ge باستخدام معلمة تطور الوقت n = i ، ارتفاعات SEG Ge (h i) ونصف قطر SEG Ge (ri) ، كما هو موضح في الفيديو التكميلي 1a و Eq. (1):

- حدد الاتجاهات الطبيعية لموقع تعسفي على أسطح النمو. بالنسبة للمقطع العرضي المستدير الشكل SEG Ge ، صف الخط الطبيعي عند (x i ، yi) ك

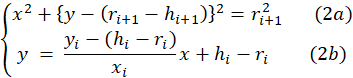

، كما هو موضح في الفيديو التكميلي 1b كخط أحمر. بعد ذلك ، احصل على حافة TD (x i + 1 ، y i + 1) من النقطة (x i ، y i) عن طريق حل المعادلات الآنية التالية:

، كما هو موضح في الفيديو التكميلي 1b كخط أحمر. بعد ذلك ، احصل على حافة TD (x i + 1 ، y i + 1) من النقطة (x i ، y i) عن طريق حل المعادلات الآنية التالية:

- احسب مسار TD واحد اعتمادا على موقع إنشاء TD (x 0 ، 0) ، كما هو موضح في الفيديو التكميلي 1c. بمعنى آخر ، يمكن حساب مسار TD التعسفي بالطريقة الموضحة أعلاه.

- احسب TDD بافتراض أن TDs تخترق السطح السفلي وتساهم في تقليل TDD (أي أن TDs أسفل النقطة التي تتجمع فيها طبقات SEG Ge محاصرة بواسطة فراغات نصف أسطوانية ولا تظهر أبدا على السطح العلوي).

- تحديد أسطح النمو والتعبير عنها بالمعادلة (المعادلات). على سبيل المثال ، عبر عن التطور الزمني لمقطع عرضي دائري الشكل لطبقة SEG Ge باستخدام معلمة تطور الوقت n = i ، ارتفاعات SEG Ge (h i) ونصف قطر SEG Ge (ri) ، كما هو موضح في الفيديو التكميلي 1a و Eq. (1):

2. إجراء التحقق التجريبي

- إعداد قناع SEG

- قبل تصنيع أقنعة SEG ، حدد مناطق نمو Ge من خلال إعداد ملف تصميم. في العمل الحالي ، قم بإعداد أنماط الخط والفضاء المحاذاة إلى [110] الاتجاه ومناطق نافذة Si ذات الشكل المربع بعرض 4 مم باستخدام برنامج تجاري (على سبيل المثال ، AutoCAD).

- تحديد تصميم أقنعة SEG (على وجه الخصوصنافذة Wوقناع W) باستخدام البرنامج. نافذة W هي عرض النافذة (عرض البذور Si)وقناع W هو عرض قناع SiO2 ، بحيث يمكن أن تتحد طبقات SEG Ge مع الطبقات المجاورة لها. حددنافذة Wوقناع W عن طريق رسم مستطيلات بالنقر فوق فتح بنية → ملف → مستطيل أو خط متعدد.

ملاحظة: يصبح عرض المستطيلاتنافذة W ، ويصبح الفاصل الزمني للمستطيلاتقناع W. في العمل الحالي ، القيم الدنيالنافذة Wوقناع W هي 0.5 ميكرومتر و 0.3 ميكرومتر ، على التوالي ، والتي تقيدها الدقة في نظام الطباعة الحجرية EB المستخدم. - كمراجع ، ارسم مناطق نافذة Si مربعة الشكل بعرض 4 مم D ، وتعتبر مناطق البطانية. انقر فوق فتح بنية → الملف → مستطيل أو متعدد الخطوط لرسم نافذة Si ذات الشكل المربع. استخدم المخططات الموضحة في الشكل 1 لإعداد أنماط الخط والمسافة ومنطقة البطانية المربعة 4 مم.

- تحضير ركائز B-doped p-Si (001) بمقاومة 1-100 Ω∙cm. في العمل الحالي ، استخدم ركائز Si مقاس 4 بوصات. نظف أسطح الركيزة بمحلول سمكة البيرانا (خليط من 20 مل من 30٪ H 2 O2 و 80 مل من 96٪ H2 SO4) حسب الضرورة.

- افتح الغطاء على فرن الأنبوب وقم بتحميل ركائز Si في الفرن باستخدام قضيب زجاجي. في العمل الحالي ، أكسدة 10 ركائز سي في وقت واحد.

- ابدأ في نفخ غاز N2 الجاف في الفرن عن طريق فتح صمام الغاز. بعد ذلك ، اضبط معدل تدفق الغاز على 0.5 لتر / م عن طريق التحكم في الصمام.

- اضبط درجة حرارة التلدين عن طريق تغيير البرنامج. في العمل الحالي ، استخدم "خطوة النمط (الوضع 2)" واضبط درجة حرارة العملية على 900 درجة مئوية. ثم قم بتشغيل البرنامج عن طريق الضغط على الوظيفة → التشغيل.

- عندما تصل درجة الحرارة إلى 900 درجة مئوية ، أغلق صمام N 2 الجاف ، وافتح صمام O 2 الجاف (تدفق O2 = 1 لتر / م) ، واحتفظ به لمدة ساعتين.

ملاحظة: قم بتنفيذ الخطوات 2.1.9-2.1.16 في غرفة صفراء. - قم بتغطية ركائز Si المؤكسدة بخافض للتوتر السطحي (OAP) باستخدام طبقة دوارة ثم اخبزها على حرارة 110 درجة مئوية لمدة 90 ثانية على لوح تسخين.

- بعد طلاء الفاعل بالسطح ، قم بتغطية ركائز Si بمقاومة للضوء (على سبيل المثال ، ZEP520A) باستخدام طبقة دوارة ثم اخبزيها على حرارة 180 درجة مئوية لمدة 5 دقائق على لوح تسخين.

- قم بتحميل ركائز Si بالسطح ومقاومة الضوء في كاتب شعاع الإلكترون (EB).

- اقرأ ملف التصميم (المعد في الخطوة 2.1.2) في كاتب EB وقم بعمل ملف عملية (ملف WEC). اضبط كمية الجرعة على 120 μC / سم2 في ملف WEC. عند انتهاء تحميل الركيزة ، قم بإجراء التعرض EB بالنقر فوق زر التعرض الفردي .

- قم بتفريغ الركيزة من كاتب EB بالنقر فوق حمل الرقاقة → تفريغها عند انتهاء التعرض.

- قم بإعداد مطور مقاوم للضوء (ZED) وشطف للمطور (ZMD) في غرفة المسودة. اغمس ركائز Si المكشوفة في المطور لمدة 60 ثانية في درجة حرارة الغرفة.

- قم بإزالة ركائز Si من المطور ، ثم جفف الركيزة بغاز N2 .

- ضع ركائز Si المطورة على لوح تسخين لتخبز على حرارة 110 درجة مئوية لمدة 90 ثانية.

- اغمس ركائز Si في حمض الهيدروفلوريك المخزن (BHF-63SE) لمدة 1 دقيقة لإزالة جزء من طبقات SiO2 المعرضة للهواء نتيجة التعرض ل EB وتطوره.

- قم بإزالة المقاومة الضوئية من ركائز Si عن طريق غمسها في مزيل عضوي مقاوم للضوء (على سبيل المثال ، Hakuri-104) لمدة 15 دقيقة.

- اغمس ركائز Si في حمض الهيدروفلوريك المخفف بنسبة 0.5٪ لمدة 4 دقائق لإزالة الأكسيد الأصلي الرقيق في مناطق النافذة ولكن للاحتفاظ بأقنعة SiO2 . ثم قم بالتحميل على غرفة ترسيب البخار الكيميائي فائقة الفراغ (UHV-CVD) لتنمو Ge. ويبين الشكل 2 نظام UHV-CVD المستخدم في هذا العمل.

- نمو Ge الفوقي

- قم بتحميل ركيزة Si بأقنعة SEG (ملفقة كما في الخطوة 2.1) في غرفة قفل التحميل.

- اضبط درجة حرارة المخزن المؤقت / درجة النمو الرئيسية في علامة التبويب الوصفة المعروضة على كمبيوتر التشغيل. حدد مدد النمو الرئيسي ل Ge بحيث تتحد طبقات SEG Ge مع الطبقات المجاورة. لتحديد فترات النمو الرئيسي ، ضع في اعتبارك معدل نمو Ge على مستويات {113} ، والذي يحدد النمو في الاتجاه داخل الطائرة / الجانبي26. في العمل الحالي ، حدد مدد النمو الرئيسي على أنها 270 دقيقة و 150 دقيقة ل 650 درجة مئوية و 700 درجة مئوية ، على التوالي.

- انقر فوق ابدأ في النافذة الرئيسية ، ثم يتم نقل الركيزة Si تلقائيا إلى غرفة النمو.

ملاحظة: تتم معالجة البروتوكول الخاص بنمو Ge الفوقي (الخطوات 2.2.4-2.2.7) تلقائيا. - تنمو Ge buffer على ركيزة Si المحملة عند درجة حرارة منخفضة (≈380 درجة مئوية). استخدم GeH 4 المخفف عند 9٪ في Ar كمصدر للغاز وحافظ على الضغط الجزئي ل GeH4 لمدة 0.5 باسكال أثناء نمو المخزن المؤقت.

- تنمو الطبقة الرئيسية Ge عند درجة حرارة مرتفعة. حافظ على الضغط الجزئي ل GeH4 لمدة 0.8 باسكال أثناء النمو الرئيسي. في العمل الحالي ، استخدم درجتي حرارة مختلفتين من 650 و 700 درجة مئوية لدرجة حرارة النمو الرئيسية من أجل مقارنة SEG Ge مع مقطع عرضي دائري الشكل ومع مقطع عرضي {113} الأوجه25.

ملاحظة: كان معدل نمو Ge على المستوى (001) 11.7 نانومتر / دقيقة بغض النظر عن درجة الحرارة. - من أجل تصور تطور SEG Ge واندماجها ، قم بإجراء نمو Ge مع الإدخال الدوري لطبقات ترسيم Si0.3Ge0.7 بسمك 10 نانومتر على ركيزة Si أخرى. تم تشكيل طبقات Si0.3Ge0.7 باستخدام غازات Si2H6 و GeH4. أثناء نمو طبقة Si0.3Ge 0.7 ، اضبط الضغط الجزئي لغاز Si2H6 عند 0.02 باسكال والضغط الجزئي لغاز GeH4 عند0.8 باسكال.

- نظرا لأن ركيزة Si يتم نقلها تلقائيا من غرفة النمو إلى غرفة قفل الحمل ، قم بتهوية غرفة قفل الحمل وتفريغ ركيزة Si يدويا.

- قياسات كثافة حفرة الحفر (EPD)

- حل 32 ملغ من I2 في 67 مل من CH3COOH باستخدام آلة التنظيف بالموجات فوق الصوتية.

- امزج I2-إذابة CH 3 COOH ، و 20 مل من HNO3، و 10 مل من HF.

- اغمس ركائز Si المزروعة Ge في محلول CH 3 COOH/ HNO3 / HF / I2 لمدة 5-7 ثوان من أجل تشكيل حفر محفورة.

- راقب أسطح Ge المحفورة باستخدام مجهر بصري (عادة 100x) لضمان تشكيل الحفر المحفورة بنجاح.

- استخدم مجهر القوة الذرية (AFM) لحساب الحفر المحفورة. ضع عينة Ge المحفورة على مرحلة AFM ، ثم اقترب من المسبار بالنقر فوق نهج تلقائي.

- حدد منطقة المراقبة باستخدام مجهر بصري مدمج مع AFM ، وقم بمسح خمس مناطق مختلفة 10 ميكرومتر × 10 ميكرومتر. يتم تحديد عامل التخميد السعة تلقائيا.

- ملاحظات TEM

- التقط عينات TEM من طبقات Ge المدمجة / البطانية باستخدام شعاع أيون Ge مركز (طريقة أخذ العينات الدقيقة FIB)27.

- تلميع عينات TEM في نظام طحن أيون باستخدام أيونات Ar. في العمل الحالي ، عينات TEM رقيقة للملاحظات المقطعية لتكون 150-500 نانومتر في الاتجاه [110] ، ولملاحظات عرض الخطة 200 نانومتر في الاتجاه [001].

- بالنسبة لعينات TEM ذات العرض المخطط ، قم بحماية الأسطح العلوية لطبقات Ge بطبقات غير متبلورة ، ثم قم بالتخفيف من الجانب السفلي (الركيزة) لطبقات Ge.

- قم بإجراء ملاحظات TEM تحت جهد تسارع يبلغ 200 كيلو فولت. قم بإجراء ملاحظات TEM (STEM) للمسح المقطعي الساطع من أجل مراقبة عينات TEM السميكة (500 نانومتر).

- بالنسبة ل Ge المدمجة مع طبقات ترسيم Si 0.3 Ge0.7 ، قم بإجراء ملاحظات STEM للحقل المظلم الحلقي عالي الزاوية (HAADF) تحت جهد تسارع يبلغ 200 كيلو فولت.

النتائج

الحساب النظري

يوضح الشكل 3 المسارات المحسوبة ل TDs في 6 أنواع من طبقات Ge المدمجة: هنا ، نحدد نسبة الفتحة (APR) لتكوننافذة W / (نافذة W +قناع W). يوضح الشكل 3 أ أصل SEG مستدير الشكل مدمج Ge من APR...

Discussion

في العمل الحالي ، تم عرض TDD من 4 × 107 / سم2 تجريبيا. لمزيد من تخفيض TDD ، هناك أساسا 2 خطوات حاسمة داخل البروتوكول: إعداد قناع SEG ونمو Ge فوق المحوري.

يشير نموذجنا الموضح في الشكل 4 إلى أنه يمكن تقليل TDD أقل من 107 / سم2 في Ge المندمجة عندما يكون APR ،

Disclosures

ليس لدى المؤلفين ما يكشفون عنه.

Acknowledgements

تم دعم هذا العمل ماليا من قبل الجمعية اليابانية لتعزيز العلوم (JSPS) KAKENHI (17J10044) من وزارة التعليم والثقافة والرياضة والعلوم والتكنولوجيا (MEXT) ، اليابان. تم دعم عمليات التصنيع من قبل "منصة تكنولوجيا النانو" (المشروع رقم 12024046) ، MEXT ، اليابان. ياماشيتا والسيدة س. هيراتا، من جامعة طوكيو، على مساعدتهما في ملاحظات فريق الخبراء التقني.

Materials

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

References

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Reprints and Permissions

Request permission to reuse the text or figures of this JoVE article

Request PermissionExplore More Articles

This article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. All rights reserved