Un abonnement à JoVE est nécessaire pour voir ce contenu. Connectez-vous ou commencez votre essai gratuit.

Method Article

Calcul théorique et vérification expérimentale pour la réduction de la dislocation dans les couches épitaxiales de germanium avec vides semi-cylindriques sur silicium

Dans cet article

Résumé

Le calcul théorique et la vérification expérimentale sont proposés pour une réduction de la densité de dislocation du filetage (TD) dans les couches épitaxiales de germanium avec des vides semi-cylindriques sur silicium. Les calculs basés sur l’interaction des TD et de la surface via la force d’image, les mesures TD et les observations de TD au microscope électronique à transmission sont présentés.

Résumé

La réduction de la densité de dislocation du filetage (TDD) dans le germanium épitaxial (Ge) sur silicium (Si) a été l’un des défis les plus importants pour la réalisation de circuits photoniques intégrés monolithiquement. Le présent document décrit les méthodes de calcul théorique et de vérification expérimentale d’un nouveau modèle de réduction du TDD. La méthode de calcul théorique décrit la flexion des dislocations de filetage (TD) basée sur l’interaction des TD et des surfaces de croissance non planaires de croissance épitaxiale sélective (SEG) en termes de force d’image de dislocation. Le calcul révèle que la présence de vides sur les masques SiO2 aide à réduire les TDD. La vérification expérimentale est décrite par le germanium (Ge) SEG, à l’aide d’une méthode de dépôt chimique en phase vapeur sous ultravide et d’observations TD du Ge cultivé par gravure et microscope électronique à transmission transversale (MET). Il est fortement suggéré que la réduction du TDD serait due à la présence de vides semi-cylindriques sur les masques SEG SiO2 et à la température de croissance. Pour la vérification expérimentale, des couches épitaxiales de Ge avec des vides semi-cylindriques sont formées à la suite du SEG des couches de Ge et de leur coalescence. Les TDD obtenus expérimentalement reproduisent les TDD calculés sur la base du modèle théorique. Les observations transversales de la TEM révèlent que la terminaison et la génération de TD se produisent à des vides semi-cylindriques. Les observations de TEM en plan révèlent un comportement unique des TD dans Ge avec des vides semi-cylindriques (c’est-à-dire que les TD sont pliés pour être parallèles aux masques SEG et au substrat Si).

Introduction

Epitaxial Ge on Si a suscité un intérêt substantiel en tant que plate-forme de dispositifs photoniques actifs puisque Ge peut détecter / émettre de la lumière dans la gamme de communication optique (1,3-1,6 μm) et est compatible avec les techniques de traitement CMOS (semi-conducteur à oxyde métallique complémentaire). Cependant, comme l’inadéquation du réseau entre Ge et Si est aussi grande que 4,2%, des dislocations de filetage (TD) se forment dans les couches épitaxiales Ge sur Si à une densité de ~109/cm2. Les performances des dispositifs photoniques Ge sont détériorées par les TD parce que les TD fonctionnent comme des centres de génération de porteurs dans les photodétecteurs Ge () et les modulateurs (MOD), et comme des centres de recombinaison de porteuses dans les diodes laser (LD). À leur tour, ils augmenteraient le courant de fuite inverse (fuite J) dans les et les MOD 1,2,3, et le courant de seuil (Jth) dans les LD 4,5,6.

Diverses tentatives ont été signalées pour réduire la densité de TD (TDD) dans Ge on Si (figure supplémentaire 1). Le recuit thermique stimule le mouvement des TD conduisant à la réduction de TDD, généralement à 2 x 107/cm2. L’inconvénient est le mélange possible de Si et de Ge et la diffusion de dopants dans Ge tels que le phosphore 7,8,9 (figure supplémentaire 1a). La couche tampon graduée SiGe 10,11,12 augmente les épaisseurs critiques et supprime la génération de TD conduisant à la réduction des TDD, généralement à 2 x 10 6/cm2. L’inconvénient ici est que le tampon épais réduit l’efficacité du couplage de lumière entre les dispositifs Ge et les guides d’ondes Si en dessous (Figure supplémentaire 1b). Le piégeage au format d’image (ART)13,14,15 est une méthode de croissance épitaxiale sélective (SEG) qui réduit les DT en piégeant les TD sur les parois latérales des tranchées épaisses de SiO 2, généralement à <1 x 10 6/cm 2. La méthode ART utilise un masque SiO 2 épais pour réduire le TDD dans Ge par rapport aux masques SiO2, qui se situe bien au-dessus du Si et présente le même inconvénient (Figure supplémentaire 1b,1c). La croissance de Ge sur les graines du pilier Si et le recuit 16,17,18 sont similaires à la méthode ART, permettant le piégeage TD par rapport d’aspect élevé Croissance Ge, à <1 x 10 5/cm2. Cependant, le recuit à haute température pour la coalescence Ge présente les mêmes inconvénients dans la figure supplémentaire 1a-c (figure supplémentaire 1d).

Pour obtenir une croissance épitaxiale Ge TDD faible sur Si qui est exempte des inconvénients des méthodes mentionnées ci-dessus, nous avons proposé une réduction TDD induite par coalescence 19,20 sur la base des deux observations clés suivantes rapportées jusqu’à présent dans la croissance SEG Ge 7,15,21,22,23 : 1) les TD sont pliés pour être perpendiculaires aux surfaces de croissance (observés par le microscope électronique à transmission transversale (MET)), et 2) la coalescence des couches de SEG Ge entraîne la formation de vides semi-cylindriques sur les masques SiO2.

Nous avons supposé que les TD sont pliés en raison de la force d’image de la surface de croissance. Dans le cas de Ge sur Si, la force d’image génère des contraintes de cisaillement de 1,38 GPa et 1,86 GPa pour les dislocations de vis et les luxations de bord à des distances de 1 nm des surfaces libres, respectivement19. Les contraintes de cisaillement calculées sont significativement plus grandes que la contrainte de Peierls de 0,5 GPa rapportée pour des dislocations de 60° dans Ge24. Le calcul prévoit la réduction TDD des couches de GES SEG sur une base quantitative et est en bon accord avec la croissance du SEG Ge19. Les observations TEM des TD sont effectuées pour comprendre les comportements de la TD dans la croissance SEG Ge présentée sur Si20. La réduction TDD induite par la force d’image est exempte de tout recuit thermique ou couche tampon épaisse, et est donc plus adaptée à l’application de dispositifs photoniques.

Dans cet article, nous décrivons des méthodes spécifiques pour le calcul théorique et la vérification expérimentale utilisés dans la méthode de réduction TDD proposée.

Protocole

1. Procédure de calcul théorique

- Calculer les trajectoires des TD. Dans le calcul, supposons que les masques SEG sont suffisamment minces pour ignorer l’effet TAR sur la réduction du TDD.

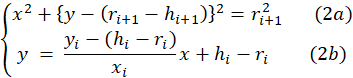

- Déterminer les surfaces de croissance et les exprimer par équation(s). Par exemple, exprimez l’évolution temporelle d’une section transversale de forme ronde d’une couche SEG Ge avec le paramètre d’évolution temporelle n = i, les hauteurs SEG Ge (h i) et les rayons SEG Ge (r i), comme indiqué dans la vidéo supplémentaire 1a et Eq. (1):

- Déterminez les directions normales d’un emplacement arbitraire sur les surfaces de croissance. Pour la section transversale de forme ronde SEG Ge, décrire la ligne normale à (x i , yi) comme

, représentée dans la vidéo supplémentaire 1b par une ligne rouge. Ensuite, obtenez le bord de la TD (x i+1, y i+1) à partir du point (x i , y i) en résolvant les équations simultanées suivantes:

, représentée dans la vidéo supplémentaire 1b par une ligne rouge. Ensuite, obtenez le bord de la TD (x i+1, y i+1) à partir du point (x i , y i) en résolvant les équations simultanées suivantes:

- Calculez une trajectoire d’un TD en fonction de l’emplacement de la génération de TD (x 0, 0), comme illustré dans la vidéo supplémentaire 1c. En d’autres termes, une trajectoire pour une TD arbitraire peut être calculée par la méthode décrite ci-dessus.

- Calculer le TDD en supposant que les TD pénètrent jusqu’à la surface inférieure et contribuent à la réduction du TDD (c.-à-d. que les TD en dessous du point où les couches SEG Ge fusionnent sont piégées par des vides semi-cylindriques et n’apparaissent jamais sur la surface supérieure).

- Déterminer les surfaces de croissance et les exprimer par équation(s). Par exemple, exprimez l’évolution temporelle d’une section transversale de forme ronde d’une couche SEG Ge avec le paramètre d’évolution temporelle n = i, les hauteurs SEG Ge (h i) et les rayons SEG Ge (r i), comme indiqué dans la vidéo supplémentaire 1a et Eq. (1):

2. Procédure de vérification expérimentale

- Préparation du masque SEG

- Avant la fabrication des masques SEG, définissez les zones de croissance Ge en préparant un fichier de conception. Dans le présent travail, préparer des motifs de ligne et d’espace alignés sur la direction [110] et des zones de fenêtre Si de forme carrée de 4 mm de largeur à l’aide d’un logiciel commercial (par exemple, AutoCAD).

- Déterminez la conception des masques SEG (en particulier Wwindow et Wmask) à l’aide du logiciel. La fenêtre W est la largeur de lafenêtre (largeur de la graine Si) et le masque W est la largeur dumasque SiO2 , de sorte que les couches SEG Ge peuvent fusionner avec leurs couches adjacentes. Déterminez lafenêtre W et lemasque W en dessinant des rectangles en cliquant sur ouvrir le fichier → la structure → rectangle ou polyligne.

Remarque : La largeur des rectangles devient lafenêtre W et l’intervalle des rectangles devient Wmask. Dans le présent travail, les valeurs minimales de lafenêtre W et dumasque W sont respectivement de 0,5 μm et 0,3 μm, qui sont limitées par la résolution dans le système de lithographie EB utilisé. - À titre de référence, dessinez des zones de fenêtre Si de forme carrée de 4 mm de largeur D, considérées comme les zones de couverture. Cliquez sur Ouvrir le fichier → la structure → rectangle ou polyligne pour dessiner la fenêtre Si de forme carrée. Utilisez les schémas illustrés à la figure 1 pour préparer les motifs de ligne et d’espace et la zone de couverture carrée de 4 mm.

- Préparer des substrats p-Si (001) dopés au B avec une résistivité de 1-100 Ω∙cm. Dans le présent travail, utilisez des substrats Si de 4 pouces. Nettoyez les surfaces du substrat avec une solution de Piranha (un mélange de 20 mL de 30% H 2 O 2 et 80 mL de 96% H2 SO4) au besoin.

- Ouvrez le couvercle d’un four tubulaire et chargez les substrats de Si dans le four à l’aide d’une tige de verre. Dans le présent travail, oxyder les substrats de 10 Si à la fois.

- Commencez à sécher le gazN2 dans le four en ouvrant la vanne de gaz. Ensuite, réglez le débit de gaz à 0,5 L/m en contrôlant la vanne.

- Réglez la température de recuit en changeant le programme. Dans le présent travail, utiliser « pas de modèle (mode 2) » et régler la température du procédé à 900 °C. Ensuite, exécutez le programme en poussant la fonction → exécutez.

- Lorsque la température atteint 900 °C, fermer la vanne N 2 sèche, ouvrir la vanne sèche O 2 (débit O 2 = 1 L/m) et conserver pendant2 h.

REMARQUE : Effectuez les étapes 2.1.9 à 2.1.16 dans une pièce jaune. - Enduire les substrats de Si oxydés d’un tensioactif (OAP) à l’aide d’un enrobage d’essorage, puis cuire au four à 110 °C pendant 90 s sur une plaque chauffante.

- Après l’enrobage du tensioactif, enduire les substrats de Si d’une résine photosensible (par exemple, ZEP520A) à l’aide d’un enrobage de spin, puis cuire à 180 °C pendant 5 minutes sur une plaque chauffante.

- Chargez les substrats de Si avec le tensioactif et la résine photosensible dans un émetteur à faisceau d’électrons (EB).

- Lisez le fichier de conception (préparé à l’étape 2.1.2) dans le graveur EB et créez un fichier d’opération (fichier WEC). Fixer la quantité de dose à 120 μC/cm2 dans le fichier WEC. Lorsque le chargement du substrat se termine, effectuez l’exposition EB en cliquant sur le bouton d’exposition unique .

- Déchargez le substrat de l’émetteur EB en cliquant sur la plaquette transporter → décharger à la fin de l’exposition.

- Préparez un révélateur de résine photosensible (ZED) et un rinçage pour le révélateur (ZMD) dans une chambre de tirage. Trempez les substrats de Si exposés dans le révélateur pendant 60 s à température ambiante.

- Retirez les substrats de Si du révélateur, puis séchez le substrat avec du gazN2 .

- Placer les substrats de Si développés sur une plaque chauffante pour cuire à 110 °C pendant 90 s.

- Trempez les substrats de Si dans un acide fluorhydrique tamponné (BHF-63SE) pendant 1 min afin d’éliminer une partie des couches deSiO2 exposées à l’air à la suite de l’exposition et du développement de l’EB.

- Retirer la résine photosensible des substrats de Si en plongeant dans un dissolvant de résine photosensible organique (par exemple, Hakuri-104) pendant 15 min.

- Trempez les substrats de Si dans de l’acide fluorhydrique dilué à 0,5% pendant 4 min pour éliminer le mince oxyde natif dans les zones vitrées mais pour conserver les masques SiO2 . Ensuite, chargez sur une chambre de dépôt chimique en phase vapeur sous ultravide (UHV-CVD) pour développer du Ge. La figure 2 montre le système UHV-CVD utilisé dans le présent travail.

- Croissance épitaxiale de GE

- Chargez le substrat Si avec des masques SEG (fabriqués comme à l’étape 2.1) dans une chambre de verrouillage de charge.

- Réglez la température de croissance de la mémoire tampon/principale dans l’onglet Recette affiché sur l’ordinateur d’exploitation. Déterminer les durées de croissance principale de Ge afin que les couches SEG Ge fusionnent avec les couches adjacentes. Pour décider des durées de la croissance principale, considérons le taux de croissance de Ge sur les plans {113}, qui détermine la croissance dans la direction dans le plan / latéral26. Dans le présent travail, fixer les durées de la croissance principale à 270 min et 150 min pour 650 °C et 700 °C, respectivement.

- Cliquez sur Démarrer dans la fenêtre principale, puis le substrat Si est automatiquement transféré dans la chambre de croissance.

NOTE: Le protocole sur la croissance épitaxiale de Ge (étapes 2.2.4-2.2.7) est automatiquement traité. - Cultiver le tampon Ge sur le substrat de Si chargé à basse température (≈380 °C). Utiliser GeH 4 dilué à 9% dans Ar comme gaz source et maintenir la pression partielle de GeH4 pendant 0,5 Pa pendant la croissance tampon.

- Cultiver la couche principale de Ge à une température élevée. Maintenir la pression partielle de GeH4 pendant 0,8 Pa pendant la croissance principale. Dans le présent travail, utiliser deux températures différentes de 650 et 700 °C pour la température de croissance principale afin de comparer SEG Ge avec une section transversale de forme ronde et avec une section transversale à {113} facettes25.

NOTE: Le taux de croissance de Ge sur le plan (001) était de 11,7 nm/min indépendamment de la température. - Afin de visualiser l’évolution du SEG Ge et leur coalescence, effectuer la croissance de Ge avec insertion périodique de couches de démarcation Si 0,3 Ge0,7de 10 nm d’épaisseur sur un autre substrat Si. Des couches de Si0,3 Ge 0,7ont été formées à l’aide de gaz Si2H6 et GeH4. Au cours de la croissance de la couche de Si0,3Ge 0,7, régler la pression partielle du gaz Si2H6 à 0,02 Pa et la pression partielle du gaz GeH4 à0,8 Pa.

- Comme le substrat de Si est automatiquement transféré de la chambre de croissance à la chambre de verrouillage de charge, évacuez la chambre de verrouillage de charge et déchargez le substrat Si manuellement.

- Mesures de densité de fosse de gravure (EPD)

- Dissoudre 32 mg deI2 dans 67 mL deCH3COOH à l’aide d’une machine de nettoyage à ultrasons.

- Mélanger le COOHCH3dissous I2, 20 mL de HNO3 et 10 mL de HF.

- Trempez les substrats de Si cultivés en Ge-S dans la solutionCH3COOH/HNO3/HF/I2 pendant 5-7 s afin de former des noyaux gravés.

- Observez les surfaces Ge gravées avec un microscope optique (généralement 100x) pour vous assurer que les fosses gravées sont formées avec succès.

- Utilisez un microscope à force atomique (AFM) pour compter les fosses gravées. Placez l’échantillon Ge gravé sur une platine AFM, puis approchez la sonde en cliquant sur l’approche automatique.

- Décidez de la zone d’observation à l’aide d’un microscope optique intégré à un AFM et balayez cinq zones différentes de 10 μm x 10 μm. Le facteur d’amortissement d’amplitude est déterminé automatiquement.

- Observations TEM

- Prélever des échantillons TEM dans les couches de Ge coalescées/matelassées à l’aide d’un faisceau d’ions Ge focalisé (méthode de microéchantillonnage FIB)27.

- Polir les échantillons TEM dans un système de broyage ionique à l’aide d’ions Ar. Dans le présent travail, éclaircir les échantillons TEM pour que les observations en coupe transversale soient de 150 à 500 nm dans la direction [110] et pour les observations en vue en plan à 200 nm dans la direction [001].

- Pour les spécimens TEM en plan, protéger les surfaces supérieures des couches Ge avec des couches amorphes, puis amincir du côté inférieur (substrat) des couches Ge.

- Effectuer des observations TEM sous une tension d’accélération de 200 kV. Effectuer des observations transversales de TEM à balayage en champ clair (STEM) afin d’observer des échantillons TEM épais (500 nm).

- Pour un Ge fusionné avec des couches de démarcation Si0,3 Ge0,7, effectuer des observations STEM en champ noir annulaire à angle élevé (HAADF) en coupe transversale sous une tension d’accélération de 200 kV.

Résultats

Calcul théorique

La figure 3 montre les trajectoires calculées des TD dans 6 types de couches Ge coalescées : ici, nous définissons le rapport d’ouverture (APR) comme étant W fenêtre/(Wfenêtre +W masque). La figure 3a montre un GE de forme ronde d’origine SEG coalescé Ge de TAEG = 0,8. Ici, 2/6 TDs sont piég...

Discussion

Dans le présent travail, des TDD de 4 x 107/cm2 ont été montrés expérimentalement. Pour une réduction supplémentaire du TDD, il y a principalement 2 étapes critiques dans le protocole: la préparation du masque SEG et la croissance épitaxiale de GE.

Notre modèle illustré à la figure 4 indique que le TDD peut être réduit en dessous de 107/cm2 dans le Ge coalescé lorsque le TAEG, Wfenêtre/(W...

Déclarations de divulgation

Les auteurs n’ont rien à divulguer.

Remerciements

Ce travail a été soutenu financièrement par la Société japonaise pour la promotion de la science (JSPS) KAKENHI (17J10044) du ministère de l’Éducation, de la Culture, des Sports, de la Science et de la Technologie (MEXT), Japon. Les procédés de fabrication ont été soutenus par « Nanotechnology Platform » (projet n° 12024046), MEXT, Japon. Les auteurs tiennent à remercier M. K. Yamashita et Mme S. Hirata, de l’Université de Tokyo, de leur aide concernant les observations TEM.

matériels

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

Références

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Réimpressions et Autorisations

Demande d’autorisation pour utiliser le texte ou les figures de cet article JoVE

Demande d’autorisationThis article has been published

Video Coming Soon