需要订阅 JoVE 才能查看此. 登录或开始免费试用。

Method Article

硅上半圆柱空隙锗外延层位错还原的理论计算和实验验证

摘要

提出了降低硅上半圆柱空隙的锗外延层螺纹位错(TD)密度的理论计算和实验验证。给出了基于TD与表面相互作用的计算方法,通过像力、TD测量和透射电子显微镜对TD的观测。

摘要

降低硅(Si)上外延锗(Ge)的螺纹位错密度(TDD)是实现单片集成光子电路的最重要挑战之一。本文介绍了一种降低TDD的新模型的理论计算和实验验证方法。理论计算方法描述了基于TDs与选择性外延生长(SEG)的非平面生长表面在位错成像力方面的相互作用的螺纹位错(TDs)的弯曲。计算表明,SiO2 掩模上空隙的存在有助于降低TDD。采用超高真空化学气相沉积法和TD观察生长的锗(Ge)SEG通过蚀刻和横截面透射电子显微镜(TEM)对生长的Ge进行实验验证。强烈建议TDD降低是由于SiO2 SEG掩模和生长温度上存在半圆柱形空隙。为了进行实验验证,由于Ge层的SEG及其聚结作用,形成了具有半圆柱形空隙的外延Ge层。实验得到的TDDs基于理论模型再现了计算出的TDD。横断面透射电镜观察表明,TD的终止和生成都发生在半圆柱形空隙处。平面透射电镜观测揭示了具有半圆柱形空隙的Ge中TD的独特行为(即TD弯曲以平行于SEG掩模和Si衬底)。

引言

Si上的外延锗作为有源光子器件平台引起了广泛兴趣,因为Ge可以检测/发射光通信范围(1.3-1.6μm)内的光,并且与Si CMOS(互补金属氧化物半导体)加工技术兼容。然而,由于Ge和Si之间的晶格失配高达4.2%,因此在Si上的Ge外延层中以~109 / cm2的密度形成螺纹位错(TDs)。由于TD在Ge光电探测器(PD)和调制器(MOD)中充当载流子生成中心,在激光二极管(LDs)中充当载流子复合中心,因此锗光子器件的性能会因TD而恶化。反过来,它们会增加PD和MOD1,2,3中的反向泄漏电流(J泄漏)和LDs4,5,6中的阈值电流(J th)。

据报道,已经有各种尝试来降低Si上Ge中的TD密度(TDD)(补充图1)。热退火刺激TD的运动,导致TDD降低,通常为2 x 107 / cm2。缺点是Si和Ge可能混合,并且掺杂剂在Ge中扩散,例如磷7,8,9(补充图1a)。SiGe分级缓冲层10,11,12增加了临界厚度并抑制了TD的产生,导致TDD降低,通常为2 x 106/cm2。这里的缺点是厚缓冲器会降低Ge器件和下方Si波导之间的光耦合效率(补充图1b)。纵横比捕获 (ART)13,14,15 是一种选择性外延生长 (SEG) 方法,通过将 TD 捕获在厚 SiO 2 沟槽的侧壁上来降低 TD,通常为 <1 x 10 6/cm 2。ART方法使用较厚的SiO 2掩模来降低Ge中的TDD,而不是SiO 2掩模,SiO2掩模远高于Si,并且具有相同的缺点(补充图1b,1c)。Si柱晶种上的Ge生长和退火16,17,18与ART方法相似,通过高纵横比Ge生长使TD捕获达到<1 x 105/cm2。然而,用于Ge聚结的高温退火在补充图1a-c(补充图1d)中具有相同的缺点。

为了在硅上实现低TDD的Ge外延生长,而不受上述方法的缺点,我们根据迄今为止在SEG Ge生长7,15,21,22,23中报告的以下两个关键观察结果,提出了聚结诱导的TDD还原19,20:1)TD弯曲成垂直于生长表面(通过横截面透射电子显微镜(TEM)观察),2)SEG Ge层的聚结导致在SiO2掩模上形成半圆柱形空隙。

我们假设TD由于生长表面的成像力而弯曲。在Si上的Ge的情况下,像像力分别在距离自由表面1 nm处产生1.38 GPa和1.86 GPa的螺杆位错和边缘位错的剪切应力19。计算出的剪切应力明显大于Ge24中报告的60°位错的Peierls应力0.5 GPa。该计算预测了Ge SEG层的TDD减少,并且与SEG Ge增长19非常吻合。对TD进行TEM观察以了解Si20上所呈现的SEG Ge生长中的TD行为。镜像力诱导的TDD还原没有任何热退火或厚缓冲层,因此更适合光子器件应用。

本文介绍了TDD还原方法的理论计算和实验验证的具体方法。

研究方案

1. 理论计算程序

- 计算TD的轨迹。在计算中,假设 SEG 掩码足够薄,可以忽略 ART 对 TDD 减少的影响。

- 确定生长表面并用方程表示。例如,使用时间演化参数 n = i、SEG Ge 高度 (h i) 和 SEG Ge 半径 (r i) 表示 SEG Ge 层圆形横截面的时间演变,如补充视频 1a 和等式 (1) 所示:

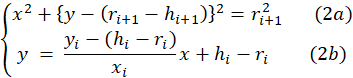

- 确定生长表面上任意位置的法线方向。对于圆形截面SEG Ge,将(x i,yi)处的法线描述为,如

补充视频1b所示为红线。然后,通过求解以下联立方程组,从点(x i , y i)获得TD(x i + 1,yi + 1)的边:

补充视频1b所示为红线。然后,通过求解以下联立方程组,从点(x i , y i)获得TD(x i + 1,yi + 1)的边:

- 根据TD生成的位置(x 0,0)计算一个TD的轨迹,如补充视频1c所示。换句话说,可以通过上述方法计算任意TD的轨迹。

- 假设TD穿透底面并有助于TDD的减少(即,低于SEG Ge层聚结点的TD被半圆柱形空隙捕获并且永远不会出现在顶面)计算TDD。

- 确定生长表面并用方程表示。例如,使用时间演化参数 n = i、SEG Ge 高度 (h i) 和 SEG Ge 半径 (r i) 表示 SEG Ge 层圆形横截面的时间演变,如补充视频 1a 和等式 (1) 所示:

2. 实验验证程序

- 赛格面罩准备

- 在制造 SEG 掩模之前,通过准备设计文件来定义 Ge 生长区域。在本工作中,使用商业软件(例如AutoCAD)准备与[110]方向对齐的线和空间图案以及宽度为4毫米的方形Si窗口区域。

- 使用软件确定SEG掩模(特别是W窗口和W掩模)的设计。W 窗口是窗口宽度(Si 种子宽度),W 掩模是 SiO2 掩模宽度,使得 SEG Ge 层可以与其相邻层合并。通过单击打开的文件→结构→矩形或多段线来绘制矩形来确定 W窗口和 W蒙版。

注意: 矩形的宽度变为 W窗口,矩形的间隔变为 W掩码。在本工作中,W窗口 和W掩模 的最小值分别为0.5 μm和0.3 μm,这受到所采用的EB光刻系统中分辨率的限制。 - 作为参考,绘制宽度为 D 的 4 mm 的方形 Si 窗口区域,视为毯子区域。单击" 打开文件"→结构→矩形或折线 以绘制方形 Si 窗口。使用 图1 所示的原理图准备线和空间图案以及4 mm方形毯区域。

- 制备电阻率为1-100 Ω∙cm的B掺杂p-Si(001)衬底。在本工作中,使用4英寸Si基板。必要时用食人鱼溶液(20 mL 30% H 2 O 2 和 80 mL 96% H2SO4 的混合物)清洁基材表面。

- 打开管式炉的盖子,使用玻璃棒将硅基板装入炉中。在本工作中,一次氧化10个Si基底。

- 通过打开气阀开始将干燥的N2 气体吹入炉中。然后,通过控制阀门将气体流量设置为 0.5 L/m。

- 通过更改程序设置退火温度。在本工作中,使用"图案步骤(模式2)"并将工艺温度设置为900°C。 然后,通过推送 函数运行→程序。

- 当温度达到900°C时,关闭干燥的N2阀,打开干燥的O 2阀(O 2流量= 1L / m),并保持2小时。

注意:在黄色房间中执行步骤 2.1.9-2.1.16。 - 使用旋涂机用表面活性剂(OAP)涂覆氧化的Si基底,然后在110°C下在加热板上烘烤90秒。

- 表面活性剂涂覆后,使用旋涂机用光刻胶(例如ZEP520A)涂覆Si基底,然后在180°C下在加热板上烘烤5分钟。

- 将表面活性剂和光刻胶装入Si基底到电子束(EB)刻录机中。

- 在EB编写器中读取设计文件(在步骤2.1.2中准备)并制作操作文件(WEC文件)。在WEC文件中将剂量设置为120μC / cm2 。基板加载完成后,通过单击单个曝光按钮进行EB 曝光 。

- 通过单击 晶圆进位 从EB写入器卸载基板→在曝光结束时卸载。

- 在通风室中准备光刻胶显影剂(ZED)和冲洗剂(ZMD)。将暴露的Si基底在室温下浸入显影剂中60秒。

- 从显影剂上去除Si基底,然后用N2 气体干燥基板。

- 将显好的Si基板放在加热板上,在110°C下烘烤90秒。

- 将Si基底浸入缓冲氢氟酸(BHF-63SE)中1分钟,以去除由于EB暴露和发育而暴露在空气中的部分SiO2 层。

- 通过浸入有机光刻胶去除剂(例如Hakuri-104)中15分钟,从Si衬底上去除光刻胶。

- 将Si衬底浸入0.5%稀释的氢氟酸中4分钟,以去除窗口区域中的稀天然氧化物,但保留SiO2 掩膜。然后加载到超高真空化学气相沉积(UHV-CVD)室中以生长Ge。 图2 显示了本工作中使用的UHV-CVD系统。

- 外延锗生长

- 将带有SEG掩模的Si衬底(如步骤2.1中制造)装入负载锁定室。

- 在操作计算机上显示的 配方 选项卡中设置缓冲液/主生长温度。确定Ge主要生长的持续时间,以便SEG Ge层与相邻层合并。要确定主要增长的持续时间,请考虑 Ge 在{113}平面上的增长率,它决定了面内/横向方向的增长26。在本工作中,将650°C和700°C的主要生长持续时间分别设置为270分钟和150分钟。

- 在主窗口中单击 开始 ,然后将Si衬底自动转移到生长室中。

注意:外延锗生长方案(步骤2.2.4-2.2.7)将自动处理。 - 在低温(≈380°C)下在负载的Si衬底上生长Ge缓冲液。使用在Ar中稀释9%的GeH 4作为源气,并在缓冲液生长期间将GeH4的分压保持在0.5 Pa。

- 在高温下生长Ge主层。在主要生长期间将GeH4 的分压保持在0.8 Pa。在本工作中,使用650和700 °C两种不同的温度作为主要生长温度,以便将SEG Ge与圆形截面和{113}面截面25进行比较。

注意:(001)平面上Ge的生长速率为11.7nm/min,与温度无关。 - 为了可视化SEG Ge的演变及其聚结,通过在另一个Si衬底上定期插入10nm厚的Si 0.3 Ge0.7分界层来进行Ge生长。Si0.3 Ge 0.7层是使用Si2H6和GeH 4气体形成的。在Si 0.3 Ge 0.7层生长过程中,将Si2H6气体的分压设置为0.02 Pa,将GeH4气体的分压设置为0.8Pa。

- 当Si衬底自动从生长室转移到负载锁定室时,请排放负载锁定室并手动卸载Si衬底。

- 蚀刻坑密度 (EPD) 测量

- 使用超声波清洗机将 32 mg I2 溶解在 67 mL 的 CH3COOH 中。

- 混合I2溶解的CH 3 COOH,20 mL HNO3和10 mLHF。

- 将锗生长的硅基底浸入CH 3 COOH/ HNO3/ HF/ I 2溶液中5-7秒,以形成蚀刻凹坑。

- 用光学显微镜(通常为100倍)观察蚀刻的Ge表面,以确保蚀刻的凹坑成功形成。

- 使用原子力显微镜(AFM)来计数蚀刻的凹坑。将蚀刻的Ge样品放在AFM载物台上,然后单击自动接近 接近探针。

- 使用与AFM集成的光学显微镜确定观察区域,并扫描五个不同的10 μm x 10 μm区域。幅度阻尼因子是自动确定的。

- 透射电镜观测

- 使用聚焦的Ge离子束(FIB微采样方法)从聚结/毯状Ge层中拾取TEM样品27。

- 使用氩离子在离子研磨系统中抛光TEM试样。在本工作中,用于横截面观测的TEM试样在[110]方向上为150-500 nm,在[001]方向上将平面视图观测的透视图样品减薄为200 nm。

- 对于平面透射电镜试样,用非晶层保护Ge层的顶面,然后从Ge层的底部(基底)侧向下变薄。

- 在 200 kV 的加速电压下进行 TEM 观察。执行横截面明场扫描透射电镜 (STEM) 观察,以观察厚 (500 nm) 透射电镜标本。

- 对于具有Si0.3 Ge 0.7分界层的聚结Ge,在200 kV的加速电压下进行横截面高角度环形暗场(HAADF)STEM观测。

结果

理论计算

图3显示了6种聚结Ge层中TD的计算轨迹:在这里,我们将孔径比(APR)定义为W窗口/(W窗口+ W掩模)。图3a显示了APR = 0.8的圆形SEG原点聚结Ge。在这里,2/6 TD 被困住。图3b显示了APR = 0.8的{113}面SEG原点聚结Ge。在这里,...

讨论

在本工作中,实验显示了4 x 107 / cm2 的TDD。为了进一步降低TDD,协议中主要有2个关键步骤:SEG掩膜制备和外延Ge生长。

图4所示的模型表明,当APR,W窗口/(W窗口+ W掩模)小至0.1时,TDD可以降低到107 / cm2在聚结Ge中。为了进一步降低TDD,应准备具有较小APR的SEG口罩。如步骤2.1.2所述,W窗口和W...

披露声明

作者没有什么可透露的。

致谢

这项工作得到了日本文部科学省(MEXT)的日本科学促进会(JSPS)KAKENHI(17J10044)的资助。制造工艺得到了日本文部科学省"纳米技术平台"(项目编号12024046)的支持。作者要感谢东京大学的K. Yamashita先生和平田S. Ms. Hirata女士在TEM观测方面的帮助。

材料

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

参考文献

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

转载和许可

请求许可使用此 JoVE 文章的文本或图形

请求许可探索更多文章

This article has been published

Video Coming Soon

版权所属 © 2025 MyJoVE 公司版权所有,本公司不涉及任何医疗业务和医疗服务。