このコンテンツを視聴するには、JoVE 購読が必要です。 サインイン又は無料トライアルを申し込む。

Method Article

シリコン上に半円筒空隙を有するゲルマニウムエピタキシャル層の転位低減に関する理論計算と実験的検証

要約

シリコン上に半円筒空隙を有するゲルマニウムエピタキシャル層におけるねじ切り転位(TD)密度の低減について、理論計算と実験的検証が提案されています。像力によるTDと表面の相互作用に基づく計算、TD測定、TDの透過型電子顕微鏡観察を示します。

要約

シリコン(Si)上のエピタキシャルゲルマニウム(Ge)のねじ切り転位密度(TDD)の低減は、モノリシックに統合されたフォトニクス回路の実現にとって最も重要な課題の1つです。本稿では,TDD低減のための新規モデルの理論計算方法と実験的検証の手法について述べる.理論計算方法は、転位像力の観点から、選択的エピタキシャル成長(SEG)のTDと非平面成長面の相互作用に基づくねじ切り転位(TD)の曲げを記述します。計算は、SiO2 マスク上のボイドの存在がTDDの減少に役立つことを明らかにしています。実験的検証は、超高真空化学気相成長法を用いたゲルマニウム(Ge)SEGによる、エッチングおよび断面透過型電子顕微鏡(TEM)による成長したGeのTD観察によって記述される。TDDの減少は、SiO2 SEGマスク上の半円筒空隙の存在と成長温度によるものであることが強く示唆されています。実験的検証のために、半円筒形のボイドを有するエピタキシャルGe層が、Ge層のSEGおよびそれらの合体の結果として形成される。実験的に得られたTDDは、理論モデルに基づいて計算されたTDDを再現します。断面TEM観察により、TDの終端と生成の両方が半円筒形の空隙で発生することが明らかになりました。平面図TEM観察により、半円筒形のボイドを持つGe中のTDのユニークな挙動が明らかになりました(つまり、TDはSEGマスクとSi基板に平行になるように曲がっています)。

概要

Si上のエピタキシャルGeは、光通信範囲(1.3〜1.6μm)の光を検出/放出でき、Si CMOS(相補型金属酸化膜半導体)処理技術に適合するため、アクティブフォトニックデバイスプラットフォームとして大きな関心を集めています。しかし、GeとSiの格子不整合は4.2%と大きいため、Si上のGeエピタキシャル層では~109/cm2の密度でねじ切り転位(TD)が形成されます。Geフォトニックデバイスは、TDがGe光検出器(PD)や変調器(MOD)のキャリア生成センターとして、レーザーダイオード(LD)のキャリア再結合センターとして機能するため、TDによって性能が低下します。次に、PDおよびMOD1,2,3の逆リーク電流(Jリーク)とLD4,5,6のスレッショルド電流(Jth)を増加させます。

Si上のGeのTD密度(TDD)を低下させるための様々な試みが報告されている(補足図1)。熱アニーリングはTDの動きを刺激し、TDDを典型的には2 x 107 / cm2に減少させます。欠点は、SiとGeの混合と、リン7,8,9などのGe中のドーパントのアウトディフュージョンの可能性です(補足図1a)。SiGe傾斜バッファ層10,11,12は、臨界厚さを増加させ、TDDの生成を抑制し、TDDを典型的には2 x 106/cm2に減少させる。ここでの欠点は、バッファが厚いため、Geデバイスとその下のSi導波路との間の光結合効率が低下することです(補足図1b)。アスペクト比トラップ(ART)13,14,15は選択的エピタキシャル成長(SEG)法であり、厚いSiO 2トレンチの側壁にTDをトラップすることにより、TDを通常<1 x 10 6 / cm2に低減します。ART法では、厚いSiO 2マスクを使用して、Siのはるか上に位置し、同じ欠点を持つSiO2マスクよりもGeのTDDを低減します(補足図1b、1c)。Siピラーシード上のGe成長とアニーリング16,17,18はART法と同様であり、高アスペクト比Ge成長によるTDトラップを可能にし、<1 x 105 / cm2になります。しかしながら、Ge合一のための高温アニールは、補足図1a〜c(補足図1d)において同じ欠点を有する。

上記の方法の欠点のないSi上で低TDDのGeエピタキシャル成長を達成するために、これまでにSEGGe成長7,15,21,22,23で報告された次の2つの重要な観察結果に基づいて、合体誘起TDD低減19,20を提案しました。:1)TDは成長面に垂直になるように曲げられ(断面透過型電子顕微鏡(TEM)によって観察され)、2)SEG Ge層の合体により、SiO2マスク上に半円筒形の空隙が形成されます。

TDは成長面からのイメージ力によって曲がっていると仮定しました。Si上のGeの場合、イメージ力は、自由表面から1nm離れた距離でのねじ転位とエッジ転位に対してそれぞれ1.38GPaと1.86GPaのせん断応力を生成します19。計算されたせん断応力は、Ge24の60°転位について報告された0.5GPaのパイエルス応力よりも大幅に大きい。この計算は、定量的にGe SEG層のTDD減少を予測し、SEG Geの成長19とよく一致しています。TDのTEM観測は、Si20上で提示されたSEG Ge成長におけるTD挙動を理解するために行われる。画像力誘起TDD低減は、熱アニーリングや厚いバッファ層がないため、フォトニックデバイスアプリケーションに適しています。

本稿では、TDD低減法の提案に採用されている理論計算と実験的検証の具体的手法について述べる。

プロトコル

1. 理論計算手順

- TDの軌道を計算します。計算では、SEGマスクがTDD低減に対するART効果を無視するのに十分なほど薄いと仮定します。

- 成長面を決定し、方程式で表します。たとえば、補足ビデオ1aおよび式(1)に示すように、SEG Ge層の丸い断面の時間発展を、時間発展パラメータn = i、SEG Geの高さ(hi)、およびSEG Ge半径(ri)で表します。

- 成長サーフェス上の任意の位置の法線方向を決定します。丸型断面SEG Geについては、補足動画1bに赤線で示す(xi,yi)

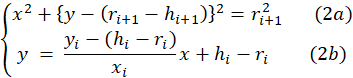

の法線を次のように記述する。次に、次の連立方程式を解いて、点(xi、y i)からTDのエッジ(x i + 1、y i + 1)を取得します。

の法線を次のように記述する。次に、次の連立方程式を解いて、点(xi、y i)からTDのエッジ(x i + 1、y i + 1)を取得します。

- 補足ビデオ 1c に示すように、TD 生成の場所 (x 0, 0) に応じて 1 TD の軌道を計算します。つまり、任意のTDの軌跡は、上述の方法により算出することができる。

- TDが底面に浸透し、TDDの減少に寄与すると仮定してTDDを計算します(つまり、SEG Ge層が合体するポイントより下のTDは半円筒形のボイドに閉じ込められ、上面に現れません)。

- 成長面を決定し、方程式で表します。たとえば、補足ビデオ1aおよび式(1)に示すように、SEG Ge層の丸い断面の時間発展を、時間発展パラメータn = i、SEG Geの高さ(hi)、およびSEG Ge半径(ri)で表します。

2. 実験検証手順

- SEGマスクの準備

- SEGマスクを作製する前に、設計ファイルを準備してGe成長領域を定義します。本研究では、市販のソフトウェア(AutoCADなど)を用いて、[110]方向と幅4mmの正方形状のSi窓領域に整列したラインアンドスペースパターンを準備します。

- ソフトウェアを使用してSEGマスク(特にWウィンドウとWマスク)の設計を決定します。Wウィンドウはウィンドウ幅(Siシード幅)、WマスクはSiO2マスク幅であり、SEG Ge層が隣接する層と合体できるようにします。WウィンドウとWマスクを決定するには、[ファイル→構造を開く]をクリックして長方形を描画し→長方形またはポリラインをクリックします。

注:長方形の幅はWウィンドウになり、長方形の間隔はWマスクになります。本研究では、Wウィンドウ とWマスク の最小値はそれぞれ0.5 μmと0.3 μmであり、採用しているEBリソグラフィシステムの分解能によって制限されています。 - 参考として、ブランケット領域とみなす幅D4mmの正方形のSi窓領域を描く。[ ファイル→構造を四角形またはポリライン→開く ]をクリックして、正方形のSiウィンドウを描画します。図1に示す回路 図 を使用して、ラインアンドスペースパターンと4mm四方のブランケット領域を準備します。

- 抵抗率が1〜100 Ω・cmのBドープp-Si(001)基板を準備します。本研究では、4インチのSi基板を使用します。必要に応じて、ピラニア溶液(20mLの30%H 2 O 2と80 mLの96%H 2SO4の混合物)で基板表面を洗浄します。

- 管状炉の蓋を開け、ガラス棒を使用してSi基板を炉に装填します。本研究では、一度に10枚のSi基板を酸化します。

- ガスバルブを開いて乾燥N2 ガスを炉内に吹き込み始める。次に、バルブを制御してガス流量を0.5 L / mに設定します。

- プログラムを変更して焼鈍温度を設定します。本作業では、「パターン工程(モード2)」を使用し、工程温度を900°Cに設定する。 次に、関数を押してプログラムを実行し →実行します。

- 温度が900°Cに達したら、ドライN 2バルブを閉じ、ドライO 2バルブ(O 2フロー= 1 L / m)を開き、2時間保持します。

注意: 黄色の部屋で手順2.1.9〜2.1.16を実行します。 - 酸化したSi基板をスピンコーターを用いて界面活性剤(OAP)でコーティングし、ホットプレート上で110°Cで90秒間ベークします。

- 界面活性剤塗布後、スピンコーターを用いてSi基板をフォトレジスト(ZEP520Aなど)で塗布し、ホットプレート上で180°Cで5分間ベークします。

- 界面活性剤とフォトレジストを含むSi基板を電子ビーム(EB)ライターにロードします。

- EBライターで設計ファイル(手順2.1.2で用意)を読み込み、オペレーションファイル(WECファイル)を作成します。WECファイルで線量量を120μC/cm2 に設定します。基板の装填が終了したら、 単回 露光ボタンをクリックしてEB露光を行います。

- 露光が終了したら、 ウェーハキャリー→アンロード をクリックして、EBライターから基板をアンロードします。

- ドラフトチャンバーでフォトレジスト現像液(ZED)と現像液用リンス液(ZMD)を準備します。露出したSi基板を現像液に室温で60秒間浸します。

- 現像液からSi基板を取り出し、N2 ガスで基板を乾燥させます。

- 現像したSi基板をホットプレートに載せ、110°Cで90秒間ベークします。

- Si基板を緩衝フッ化水素酸(BHF-63SE)に1分間浸して、EB曝露および現像の結果として空気にさらされたSiO2 層の一部を除去します。

- 有機フォトレジスト除去剤(Hakuri-104など)に15分間浸漬して、Si基板からフォトレジストを除去します。

- Si基板を0.5%希フッ化水素酸に4分間浸して、窓領域の薄い自然酸化物を除去しますが、SiO2 マスクを保持します。次に、超高真空化学気相成長(UHV-CVD)チャンバーにロードしてGeを成長させます。 図2 に本研究で用いたUHV-CVDシステムを示す。

- エピタキシャルGe成長

- SEGマスク(ステップ2.1のように作製)を備えたSi基板をロードロックチャンバーにロードします。

- バッファー/主成長温度は、オペレーションコンピュータに表示される レシピ タブで設定します。SEG Ge層が隣接する層と合体するように、Geの主な成長の期間を決定します。主な成長の期間を決定するために、面内/横方向の成長を決定する{113}面上のGeの成長率を考慮してください26。本研究では、主成長の持続時間を650°Cと700°Cでそれぞれ270分と150分に設定します。

- メインウィンドウで 開始 をクリックすると、Si基板が自動的に成長チャンバーに転送されます。

注:エピタキシャルGe成長に関するプロトコル(ステップ2.2.4-2.2.7)は自動的に処理されます。 - 装填したSi基板上にGeバッファーを低温(≈380°C)で成長させる。原料ガスとしてArで9%に希釈したGeH4を使用し、バッファー成長中はGeH4の分圧を0.5Paに保つ。

- 高温でGeメイン層を成長させます。主成長中はGeH4 の分圧を0.8 Paに保ちます。本研究では、SEG Geを円形の断面と{113}面の断面25と比較するために、主成長温度に650°Cと700°Cの2つの異なる温度を使用します。

注:(001)面でのGeの成長速度は、温度とは無関係に11.7 nm / minでした。 - SEG Geの進化とその合体を可視化するために、別のSi基板上に厚さ10nmのSi0.3Ge0.7境界層を周期的に挿入しながらGe成長を行います。Si0.3 Ge 0.7層は、Si2H6およびGeH4ガスを用いて形成した。Si0.3Ge0.7層成長中は、Si2H6ガスの分圧を0.02Pa、GeH4ガスの分圧を0.8Paとする。

- Si基板は成長チャンバーからロードロックチャンバーに自動的に転送されるため、ロードロックチャンバーをベントし、Si基板を手動でアンロードします。

- エッチングピット密度(EPD)測定

- 超音波洗浄機を用いて、32mgのI2 を67mLのCH3COOHに溶解する。

- I2-溶解したCH3COOH、20mLのHNO3、および10mLのHFを混合する。

- Ge成長したSi基板をCH3COOH / HNO3 / HF / I2 溶液に5〜7秒間浸して、エッチングピットを形成します。

- エッチングされたGe表面を光学顕微鏡(通常は100倍)で観察し、エッチングされたピットが正常に形成されていることを確認します。

- 原子間力顕微鏡(AFM)を使用して、エッチングされたピットをカウントします。エッチングしたGeサンプルをAFMステージに置き、自動 アプローチをクリックしてプローブに近づきます。

- AFMと一体化した光学顕微鏡で観察エリアを決め、10μm×10μmの5つのエリアをスキャンします。振幅減衰係数は自動的に決定されます。

- 電子顕微鏡観察

- 集束Geイオンビーム(FIBマイクロサンプリング法)を使用して、合体/ブランケットGe層からTEM試料をピックアップします27。

- TeM試料をArイオンを用いたイオンミリングシステムで研磨します。本研究では、断面観察では[110]方向に150-500 nm、平面観察では[001]方向に200 nmとするTEM試料を薄くする。

- 平面TEM試料の場合は、Ge層の上面をアモルファス層で保護し、Ge層の下(基板)側から薄くします。

- 加速電圧200kVでTEM観察を行います。厚い(500 nm)TEM試料を観察するために、断面明視野走査TEM(STEM)観察を実行します。

- Si0.3 Ge 0.7境界層と合体したGeの場合、加速電圧200 kVで断面高角環状暗視野(HAADF)STEM観測を行います。

結果

理論計算

図3は、6種類の合体Ge層におけるTDの計算軌跡を示しています。 ここでは、開口率(APR)をWウィンドウ/(Wウィンドウ+Wマスク)と定義します。図3aは、APR=0.8のGeが合体した丸型SEG原点を示す。ここでは、2/6TDがトラップされています。

ディスカッション

本研究では、4 x 107 / cm2 のTDDが実験的に示されました。さらなるTDD低減のために、プロトコル内には主にSEGマスク調製とエピタキシャルGe成長の2つの重要なステップがあります。

図4に示す我々のモデルは、APR、Wウィンドウ/(Wウィンドウ+ Wマスク)が0.1と小さい場合、合体GeでTDDを107/cm2未満に減らすこ...

開示事項

著者は開示するものは何もありません。

謝辞

本研究は、文部科学省の日本学術振興会(JSPS)科研費(17J10044)の助成を受けて行われました。製造プロセスは、文部科学省の「ナノテクノロジープラットフォーム」(プロジェクト番号12024046)によってサポートされました。著者らは、東京大学の山下和彦氏と平田聡氏のTEM観測に協力してくださったことに感謝する。

資料

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

参考文献

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

転載および許可

このJoVE論文のテキスト又は図を再利用するための許可を申請します

許可を申請さらに記事を探す

This article has been published

Video Coming Soon

Copyright © 2023 MyJoVE Corporation. All rights reserved