Aby wyświetlić tę treść, wymagana jest subskrypcja JoVE. Zaloguj się lub rozpocznij bezpłatny okres próbny.

Method Article

Theoretical Calculation and Experimental Verification for Dislocation Reduction in Germanium Epitaxial Layers with Semicylindrical Voids on Silicon

W tym Artykule

Podsumowanie

Theoretical calculation and experimental verification are proposed for a reduction of threading dislocation (TD) density in germanium epitaxial layers with semicylindrical voids on silicon. Calculations based on the interaction of TDs and surface via image force, TD measurements, and transmission electron microscope observations of TDs are presented.

Streszczenie

Reduction of threading dislocation density (TDD) in epitaxial germanium (Ge) on silicon (Si) has been one of the most important challenges for the realization of monolithically integrated photonics circuits. The present paper describes methods of theoretical calculation and experimental verification of a novel model for the reduction of TDD. The method of theoretical calculation describes the bending of threading dislocations (TDs) based on the interaction of TDs and non-planar growth surfaces of selective epitaxial growth (SEG) in terms of dislocation image force. The calculation reveals that the presence of voids on SiO2 masks help to reduce TDD. Experimental verification is described by germanium (Ge) SEG, using an ultra-high vacuum chemical vapor deposition method and TD observations of the grown Ge via etching and cross-sectional transmission electron microscope (TEM). It is strongly suggested that the TDD reduction would be due to the presence of semicylindrical voids over the SiO2 SEG masks and growth temperature. For experimental verification, epitaxial Ge layers with semicylindrical voids are formed as the result of SEG of Ge layers and their coalescence. The experimentally obtained TDDs reproduce the calculated TDDs based on the theoretical model. Cross-sectional TEM observations reveal that both the termination and generation of TDs occur at semicylindrical voids. Plan-view TEM observations reveal a unique behavior of TDs in Ge with semicylindrical voids (i.e., TDs are bent to be parallel to the SEG masks and the Si substrate).

Wprowadzenie

Epitaxial Ge on Si has attracted substantial interests as an active photonic device platform since Ge can detect/emit light in the optical communication range (1.3-1.6 µm) and is compatible with Si CMOS (complementary metal oxide semiconductor) processing techniques. However, since the lattice mismatch between Ge and Si is as large as 4.2%, threading dislocations (TDs) are formed in Ge epitaxial layers on Si at a density of ~109/cm2. The performances of Ge photonic devices are deteriorated by TDs because TDs works as carrier generation centers in Ge photodetectors (PDs) and modulators (MODs), and as carrier recombination centers in laser diodes (LDs). In turn, they would increase reverse leakage current (Jleak) in PDs and MODs1,2,3, and threshold current (Jth) in LDs4,5,6.

Various attempts have been reported to reduce TD density (TDD) in Ge on Si (Supplemental Figure 1). Thermal annealing stimulates movement of TDs leading to the reduction of TDD, typically to 2 x 107/cm2. The drawback is the possible intermixing of Si and Ge and out-diffusion of dopants in Ge such as phosphorus7,8,9 (Supplemental Figure 1a). The SiGe graded buffer layer10,11,12 increases the critical thicknesses and suppresses the generation of TDs leading to the reduction of TDD, typically to 2 x 106/cm2. The drawback here is that the thick buffer reduces light coupling efficiency between Ge devices and Si waveguides underneath (Supplemental Figure 1b). Aspect ratio trapping (ART)13,14,15 is a selective epitaxial growth (SEG) method and reduces TDs by trapping TDs at the sidewalls of thick SiO2 trenches, typically to <1 x 106/cm2. The ART method uses a thick SiO2 mask to reduce TDD in Ge over the SiO2 masks, which locates far above Si and have the same drawback (Supplemental Figure 1b,1c). Ge growth on Si pillar seeds and annealing16,17,18 are similar to the ART method, enabling TD trapping by the high aspect ratio Ge growth, to <1 x 105/cm2. However, high temperature annealing for Ge coalescence has the same drawbacks in Supplemental Figure 1a-c (Supplemental Figure 1d).

To achieve low-TDD Ge epitaxial growth on Si that is free from the drawbacks of the above-mentioned methods, we have proposed coalescence-induced TDD reduction19,20 based on the following two key observations reported so far in SEG Ge growth7,15,21,22,23: 1) TDs are bent to be normal to the growth surfaces (observed by the cross-sectional transmission electron microscope (TEM)), and 2) coalescence of SEG Ge layers results in the formation of semicylindrical voids over the SiO2 masks.

We have assumed that the TDs are bent owing to the image force from the growth surface. In the case of Ge on Si, the image force generates 1.38 GPa and 1.86 GPa shear stresses for screw dislocations and edge dislocations at distances 1 nm away from the free surfaces, respectively19. The calculated shear stresses are significantly larger than the Peierls stress of 0.5 GPa reported for 60° dislocations in Ge24. The calculation predicts TDD reduction in Ge SEG layers on a quantitative basis and is in good agreement with the SEG Ge growth19. TEM observations of TDs are carried out to understand TD behaviors in the presented SEG Ge growth on Si20. The image-force-induced TDD reduction is free from any thermal annealing or thick buffer layers, and thus is more suitable for photonic device application.

In this article, we describe specific methods for the theoretical calculation and experimental verification employed in the proposing TDD reduction method.

Protokół

1. Theoretical calculation procedure

- Calculate trajectories of TDs. In the calculation, assume the SEG masks to be thin enough to ignore the ART effect on TDD reduction.

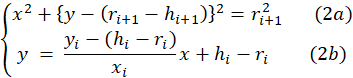

- Determine growth surfaces and express them by equation(s). For instance, express the time evolution of a round-shaped cross-section of a SEG Ge layer with the time evolution parameter n = i, SEG Ge heights (hi) and SEG Ge radii (ri), as shown in the Supplemental Video 1a and Eq. (1):

- Determine normal directions for an arbitrary location on the growth surfaces. For the round-shaped cross-section SEG Ge, describe the normal line at (xi , yi) as

, shown in Supplemental Video 1b as a red line. Then, obtain the edge of the TD (xi+1 , yi+1) from the point (xi , yi) by solving the following simultaneous equations:

, shown in Supplemental Video 1b as a red line. Then, obtain the edge of the TD (xi+1 , yi+1) from the point (xi , yi) by solving the following simultaneous equations:

- Calculate a trajectory of one TD depending on the location of TD generation (x0, 0), as shown in Supplemental Video 1c. In other words, a trajectory for an arbitrary TD can be calculated by the method described above.

- Calculate TDD assuming that TDs penetrate to the bottom surface and contribute to the reduction of TDD (i.e., TDs below the point where SEG Ge layers coalesce are trapped by semicylindrical voids and never appear on the top surface).

- Determine growth surfaces and express them by equation(s). For instance, express the time evolution of a round-shaped cross-section of a SEG Ge layer with the time evolution parameter n = i, SEG Ge heights (hi) and SEG Ge radii (ri), as shown in the Supplemental Video 1a and Eq. (1):

2. Experimental verification procedure

- SEG mask preparation

- Prior to the fabrication of SEG masks, define Ge growth areas by preparing a design file. Inthe present work, prepare line-and-space patterns aligned to the [110] direction and square-shaped Si window areas of 4 mm in width using commercial software (e.g., AutoCAD).

- Determine the design of SEG masks(in particular Wwindow and Wmask)using the software.Wwindow is the window width (Si seed width) and Wmask is the SiO2 mask width, such that SEG Ge layers can coalesce with their adjacent ones. Determine Wwindow and Wmask by drawing rectangles by clicking open file → structure → rectangle or polyline.

NOTE: The width of the rectangles becomes Wwindow, and the interval of the rectangles becomes Wmask. In the present work, the minimum values of Wwindow and Wmask are 0.5 µm and 0.3 µm, respectively, which are restricted by the resolution in the employed EB lithography system. - As references, draw square-shaped Si window areas of 4 mm in width D, regarded as the blanket areas. Click open file → structure → rectangle or polyline to draw the square-shaped Si window. Use the schematics shown in Figure 1 to prepare the line-and-space patterns and the 4 mm square blanket area.

- Prepare B-doped p-Si (001) substrates with the resistivity of 1-100 Ω∙cm. In the present work, use 4-inch Si substrates. Clean the substrate surfaces with Piranha solution (a mixture of 20 mL of 30% H2O2 and 80 mL of 96% H2SO4) as necessary.

- Open the lid on a tube furnace and load the Si substrates into the furnace using a glass rod. In the present work, oxidize 10 Si substrates at one time.

- Start to blow dry N2 gas into the furnace by opening the gas valve. Then, set the gas flow rate to 0.5 L/m by controlling the valve.

- Set the annealing temperature by changing the program. In the present work, use "pattern step (mode 2)" and set the process temperature to 900 °C. Then, run the program by pushing function → run.

- As the temperature reaches 900 °C, close the dry N2 valve, open the dry O2 valve (O2 flow = 1 L/m), and keep for 2 h.

NOTE: Perform steps 2.1.9-2.1.16 in a yellow room. - Coat the oxidized Si substrates with a surfactant (OAP) using a spin coater and then bake at 110 °C for 90 s on a hotplate.

- After the surfactant coating, coat the Si substrates with a photoresist (e.g., ZEP520A) using a spin coater and then bake at 180 °C for 5 min on a hotplate.

- Load the Si substrates with the surfactant and photoresist into an electron beam (EB) writer.

- Read the design file (prepared in step 2.1.2) in the EB writer and make an operation file (WEC file). Set dose quantity as 120 µC/cm2 in the WEC file. As the substrate loading finishes, perform EB exposure by clicking the single exposure button.

- Unload the substrate from the EB writer by clicking wafer carry → unload as the exposure finishes.

- Prepare a photoresist developer (ZED) and a rinse for the developer (ZMD) in a draft chamber. Dip the exposed Si substrates into the developer for 60 s at room temperature.

- Remove the Si substrates from the developer, and then dry the substrate with N2 gas.

- Put the developed Si substrates on a hotplate to bake at 110 °C for 90 s.

- Dip the Si substrates into a buffered hydrofluoric acid (BHF-63SE) for 1 min in order to remove part of the SiO2 layers exposed to the air as the result of EB exposure and development.

- Remove the photoresist from the Si substrates by dipping into an organic photoresist remover (e.g., Hakuri-104) for 15 min.

- Dip the Si substrates into 0.5% diluted hydrofluoric acid for 4 min to remove the thin native oxide in the window regions but to retain the SiO2 masks. Then load onto an ultrahigh-vacuum chemical vapor deposition (UHV-CVD) chamber to grow Ge. Figure 2 shows the UHV-CVD system used in the present work.

- Epitaxial Ge growth

- Load the Si substrate with SEG masks (fabricated as in step 2.1) into a load lock chamber.

- Set the buffer/main growth temperature in the Recipe tab shown on the operation computer. Determine the durations for the main growth of Ge so that SEG Ge layers coalesce with adjacent ones. To decide the durations for the main growth, consider the growth rate of Ge on the {113} planes, which determines the growth in the in-plane/lateral direction26. In the present work, set the durations for the main growth as 270 min and 150 min for 650 °C and 700 °C, respectively.

- Click start in main window, and then the Si substrate is automatically transferred into the growth chamber.

NOTE: Protocol on epitaxial Ge growth (steps 2.2.4-2.2.7) is automatically processed. - Grow Ge buffer on the loaded Si substrate at low-temperature (≈380 °C). Use GeH4 diluted at 9% in Ar as the source gas and keep the partial pressure of GeH4 for 0.5 Pa during the buffer growth.

- Grow Ge main layer at an elevated temperature. Keep the partial pressure of GeH4 for 0.8 Pa during the main growth. In the present work, use two different temperatures of 650 and 700 °C for the main growth temperature in order to compare SEG Ge with a round-shaped cross-section and with a {113}-facetted cross-section25.

NOTE: The growth rate of Ge on the (001) plane was 11.7 nm/min independent of the temperature. - In order to visualize the evolution of SEG Ge and their coalescence, perform Ge growth with periodic insertion of 10-nm-thick Si0.3Ge0.7 demarcation layers on another Si substrate. Si0.3Ge0.7 layers were formed using Si2H6 and GeH4 gases. During the Si0.3Ge0.7-layer growth, set the partial pressure of Si2H6 gas at 0.02 Pa and the partial pressure of GeH4 gas at 0.8 Pa.

- As the Si substrate is automatically transferred from the growth chamber to the load lock chamber, vent the load lock chamber and unload the Si substrate manually.

- Etch pit density (EPD) measurements

- Dissolve 32 mg of I2 in 67 mL of CH3COOH using an ultrasonic cleaning machine.

- Mix the I2-dissolved CH3COOH, 20 mL of HNO3, and 10 mL of HF.

- Dip the Ge-grown Si substrates into the CH3COOH/HNO3/HF/I2 solution for 5-7 s in order to form etched pits.

- Observe the etched Ge surfaces with an optical microscope (typically 100x) to ensure that etched pits are successfully formed.

- Employ an atomic force microscope (AFM) to count the etched pits. Put the etched Ge sample on an AFM stage, and then approach the probe by clicking auto approach.

- Decide the observation area using an optical microscope integrated with an AFM, and scan five different 10 µm x 10 µm areas. The amplitude damping factor is automatically determined.

- TEM observations

- Pick up TEM specimens from the coalesced/blanket Ge layers by using a focused Ge ion beam (FIB micro sampling method)27.

- Polish the TEM specimens in an ion milling system using Ar ions. In the present work, thin down TEM specimens for cross-sectional observations to be 150-500 nm in the [110] direction, and for plan-view observations to be 200 nm in the [001] direction.

- For plan-view TEM specimens, protect the top surfaces of the Ge layers with amorphous layers, and then thin down from the bottom (substrate) side of the Ge layers.

- Perform TEM observations under an acceleration voltage of 200 kV. Perform cross-sectional bright-field scanning TEM (STEM) observations in order to observe thick (500 nm) TEM specimens.

- For a coalesced Ge with Si0.3Ge0.7 demarcation layers, perform cross-sectional high-angle annular dark field (HAADF) STEM observations under an acceleration voltage of 200 kV.

Wyniki

Theoretical Calculation

Figure 3 shows calculated trajectories of TDs in 6 types of coalesced Ge layers: here, we define the aperture ratio (APR) to be Wwindow/(Wwindow + Wmask). Figure 3a shows a round-shaped SEG origin coalesced Ge of APR = 0.8. Here, 2/6 TDs are trapped. Figure 3b

Dyskusje

In the present work, TDD of 4 x 107/cm2 were experimentally shown. For further TDD reduction, there are mainly 2 critical steps within the protocol: SEG mask preparation and epitaxial Ge growth.

Our model shown in Figure 4 indicates that TDD can be reduced lower than 107/cm2 in coalesced Ge when APR, Wwindow/(Wwindow + Wmask), is as small as 0.1. Toward further TDD reduction, SEG masks wi...

Ujawnienia

The authors have nothing to disclose.

Podziękowania

This work was financially supported by Japan Society for the Promotion of Science (JSPS) KAKENHI (17J10044) from the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan. The fabrication processes were supported by "Nanotechnology Platform" (project No. 12024046), MEXT, Japan. The authors would like to thank Mr. K. Yamashita and Ms. S. Hirata, the University of Tokyo, for their help on TEM observations.

Materiały

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

Odniesienia

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Przedruki i uprawnienia

Zapytaj o uprawnienia na użycie tekstu lub obrazów z tego artykułu JoVE

Zapytaj o uprawnieniaPrzeglądaj więcej artyków

This article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. Wszelkie prawa zastrzeżone