JoVE 비디오를 활용하시려면 도서관을 통한 기관 구독이 필요합니다. 전체 비디오를 보시려면 로그인하거나 무료 트라이얼을 시작하세요.

Method Article

실리콘에 반원통형 공극이 있는 게르마늄 에피택셜 층의 전위 감소에 대한 이론적 계산 및 실험적 검증

요약

실리콘에 반원통형 공극이 있는 게르마늄 에피택셜 층에서 나사산 전위(TD) 밀도를 줄이기 위해 이론적 계산 및 실험적 검증이 제안됩니다. 이미지 힘을 통한 TD와 표면의 상호 작용, TD 측정 및 TD의 투과 전자 현미경 관찰을 기반으로 한 계산이 제공됩니다.

초록

실리콘(Si)의 에피택셜 게르마늄(Ge)에서 스레딩 전위 밀도(TDD)의 감소는 모놀리식 집적 포토닉스 회로를 실현하기 위한 가장 중요한 과제 중 하나였습니다. 본 논문은 TDD 감소를 위한 새로운 모델의 이론적 계산 및 실험적 검증 방법을 설명합니다. 이론적 계산 방법은 전위 이미지 힘 측면에서 선택적 에피택셜 성장(SEG)의 TD와 비평면 성장 표면의 상호 작용을 기반으로 하는 스레딩 전위(TD)의 굽힘을 설명합니다. 계산에 따르면 SiO2 마스크에 공극이 존재하면 TDD를 줄이는 데 도움이됩니다. 실험적 검증은 초고진공 화학 기상 증착 방법과 에칭 및 단면 투과 전자 현미경(TEM)을 통해 성장한 Ge의 TD 관찰을 사용하여 게르마늄(Ge) SEG로 설명됩니다. TDD 감소는SiO2 SEG 마스크 및 성장 온도에 대한 반원통형 공극의 존재 때문일 것이라고 강력히 제안된다. 실험적 검증을 위해, 반원통형 공극을 갖는 에피택셜 Ge 층은 Ge 층의 SEG와 그 합체의 결과로 형성된다. 실험적으로 획득된 TDD는 이론적 모델에 기초하여 계산된 TDD를 재현한다. 단면 TEM 관찰은 TD의 종단과 생성이 모두 반원통형 공극에서 발생한다는 것을 보여줍니다. 평면도 TEM 관찰은 반원통형 공극이 있는 Ge에서 TD의 고유한 거동을 보여줍니다(즉, TD는 SEG 마스크 및 Si 기판과 평행하게 구부러짐).

서문

Epitaxial Ge on Si는 광통신 범위 (1.3-1.6 μm)에서 빛을 감지 / 방출 할 수 있고 Si CMOS (Complementary Metal Oxide Semiconductor) 처리 기술과 호환되기 때문에 능동적 인 광자 소자 플랫폼으로 상당한 관심을 끌었습니다. 그러나, Ge와 Si 사이의 격자 불일치가 4.2 %만큼 크기 때문에, 스레딩 전위 (TDs)는 ~ 109 / cm2의 밀도로 Si의 Ge 에피 택셜 층에 형성된다. TD는 Ge 광검출기(PD) 및 변조기(MOD)에서 캐리어 생성 센터로 작동하고 레이저 다이오드(LD)에서 캐리어 재결합 센터로 작동하기 때문에 Ge 광자 장치의 성능이 TD에 의해 저하됩니다. 차례로, 그들은 PD와 MOD들 1,2,3에서 역 누설 전류(J누설)를 증가시킬 것이고, LD들 4,5,6에서 임계 전류(Jth)를 증가시킬 것이다.

Si 상의 Ge에서 TD 밀도(TDD)를 감소시키기 위한 다양한 시도가 보고되었다(보충 그림 1). 열 어닐링은 TD의 움직임을 자극하여 TDD를 일반적으로 2 x 107/cm2로 감소시킵니다. 단점은 Si와 Ge의 혼성 및 인 7,8,9와 같은 Ge의 도펀트의 아웃 확산 가능성이다 (보충 그림 1a). SiGe 등급 버퍼층(10,11,12)은 임계 두께를 증가시키고 TD의 생성을 억제하여 TDD를 감소시키며, 일반적으로 2 x 10 6/cm2로 감소시킨다. 여기서 단점은 두꺼운 버퍼가 Ge 장치와 그 아래의 Si 도파관 사이의 광 결합 효율을 감소시킨다는 것입니다(보충 그림 1b). 종횡비 트래핑(ART)13,14,15는 선택적 에피택셜 성장(SEG) 방법이며 두꺼운 SiO2 트렌치의 측벽에 TD를 트래핑하여 TD를 감소시킵니다(일반적으로 <1 x 10 6/cm2). ART 방법은 두꺼운 SiO 2 마스크를 사용하여 SiO2 마스크에 비해 Ge의 TDD를 감소시키는데, 이는 Si보다 훨씬 위에 위치하며 동일한 단점을 가지고 있습니다 (보충 그림 1b, 1c). Si 필라 시드에서의 Ge 성장 및 어닐링 16,17,18은 ART 방법과 유사하며, <1 x 10 5/cm2의 높은 종횡비 Ge 성장에 의한 TD 트래핑을 가능하게 합니다. 그러나, Ge 유착을 위한 고온 어닐링은 보충도 1a-c(보충도 1d)에서 동일한 단점을 갖는다.

상술한 방법들의 단점이 없는 Si 상에서 낮은 TDD Ge 에피택셜 성장을 달성하기 위해, 본 발명자들은 SEG Ge 성장 7,15,21,22,23에서 지금까지 보고된 다음의 두 가지 주요 관찰에 기초하여 유착 유도 TDD 감소 19,20을 제안하였다 : 1) TD는 성장 표면에 수직으로 구부러져 (단면 투과 전자 현미경 (TEM)으로 관찰), 2) SEG Ge 층의 합체로 인해 SiO2 마스크 위에 반원통형 공극이 형성됩니다.

우리는 TD가 성장 표면의 이미지 힘으로 인해 구부러져 있다고 가정했습니다. Si 상의 Ge의 경우, 이미지 힘은 자유 표면으로부터 1nm 떨어진 거리에서 나사 전위 및 에지 전위에 대해 각각 1.38GPa 및 1.86GPa 전단 응력을 생성한다(19). 계산된 전단 응력은 Ge24에서 60° 전위에 대해 보고된 0.5GPa의 Peierls 응력보다 훨씬 큽니다. 이 계산은 정량적으로 GE SEG 층의 TDD 감소를 예측하며 SEG Ge 성장과 잘 일치한다19. TD의 TEM 관찰은 Si20에서 제시된 SEG Ge 성장에서 TD 거동을 이해하기 위해 수행됩니다. 이미지 힘에 의한 TDD 감소는 열 어닐링 또는 두꺼운 버퍼 층이 없으므로 광자 장치 애플리케이션에 더 적합합니다.

이 기사에서는 제안된 TDD 감소 방법에 사용된 이론적 계산 및 실험적 검증을 위한 특정 방법을 설명합니다.

프로토콜

1. 이론적 계산 절차

- TD의 궤적을 계산합니다. 계산에서 SEG 마스크가 TDD 감소에 대한 ART 효과를 무시할 수 있을 만큼 얇다고 가정합니다.

- 성장 표면을 결정하고 방정식으로 표현합니다. 예를 들어, 보충 비디오 1a 및 식 (1)에 표시된 대로 시간 진화 매개변수 n = i, SEG Ge 높이(h i) 및 SEG Ge 반지름(r i)을 사용하여 SEG Ge 레이어의 둥근 모양 단면의 시간 진화를 표현합니다.

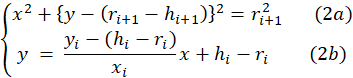

- 성장 표면의 임의 위치에 대한 수직 방향을 결정합니다. 둥근 형상 단면 SEG Ge의 경우, (xi, yi)에서의 법선 선을 보충 비디오 1b에 빨간색 선으로 표시한 바와 같이

설명한다. 그런 다음 다음 동시 방정식을 풀어 점 (xi, yi)에서 TD의 가장자리 (xi+1 , yi +1)를 구합니다.

설명한다. 그런 다음 다음 동시 방정식을 풀어 점 (xi, yi)에서 TD의 가장자리 (xi+1 , yi +1)를 구합니다.

- 보충 비디오 1c에 표시된 대로 TD 생성 위치(x 0, 0)에 따라 하나의 TD의 궤적을 계산합니다. 즉, 임의의 TD에 대한 궤적은 전술한 방법에 의해 계산될 수 있다.

- TD가 바닥면으로 침투하여 TDD의 감소에 기여한다고 가정하여 TDD를 계산합니다(즉, SEG Ge 층이 합쳐지는 지점 아래의 TD는 반원통형 공극에 의해 갇히고 상단 표면에 나타나지 않음).

- 성장 표면을 결정하고 방정식으로 표현합니다. 예를 들어, 보충 비디오 1a 및 식 (1)에 표시된 대로 시간 진화 매개변수 n = i, SEG Ge 높이(h i) 및 SEG Ge 반지름(r i)을 사용하여 SEG Ge 레이어의 둥근 모양 단면의 시간 진화를 표현합니다.

2. 실험적 검증 절차

- SEG 마스크 준비

- SEG 마스크를 제작하기 전에 설계 파일을 준비하여 Ge 성장 영역을 정의합니다. 현재 작업에서는 상용 소프트웨어(예: AutoCAD)를 사용하여 [110] 방향에 정렬된 선과 공간 패턴과 폭 4mm의 사각형 모양의 Si 창 영역을 준비합니다.

- 소프트웨어를 사용하여 SEG 마스크(특히 W창 및 W마스크)의 디자인을 결정합니다. W 윈도우는윈도우 폭(Si seed width)이고 W 마스크는 SiO2 마스크 폭이며, SEG Ge 층이 인접한 층들과 합쳐질 수 있도록 한다. 파일 열기를 클릭하여 사각형을 그려 W창과 W마스크를 결정하고 사각형 또는 폴리라인→ 구조→ 결정합니다.

참고: 직사각형의 너비는 W창이 되고 직사각형의 간격은 W마스크가 됩니다. 본 연구에서, W윈도우 및 W마스크 의 최소값은 각각 0.5 μm 및 0.3 μm이며, 이는 채용된 EB 리소그래피 시스템에서의 분해능에 의해 제한된다. - 참고로, 블랭킷 영역으로 간주되는 폭 D의 4mm의 사각형 모양의 Si 창 영역을 그립니다. 사각형 또는 폴리선→ 구조→ 파일 열기 를 클릭하여 사각형 모양의 Si 창을 그립니다. 그림 1 에 표시된 회로도를 사용하여 선 및 공간 패턴과 4mm 정사각형 블랭킷 영역을 준비합니다.

- 1-100 Ω∙cm의 저항을 갖는 B 도핑 된 p-Si (001) 기판을 준비한다. 본 연구에서는 4 인치 Si 기판을 사용하십시오. 필요에 따라 피라냐 용액(30% H2O22 mL와 96% H2SO4 80mL의혼합물)으로 기판 표면을 청소합니다.

- 튜브 퍼니스의 뚜껑을 열고 유리 막대를 사용하여 퍼니스에 Si 기판을 로드합니다. 본 연구에서는 한 번에 10 개의 Si 기판을 산화시킨다.

- 가스 밸브를 열어 건조한 N2 가스를 용광로로 불어넣기 시작합니다. 그런 다음 밸브를 제어하여 가스 유량을 0.5L/m로 설정합니다.

- 프로그램을 변경하여 어닐링 온도를 설정합니다. 본 연구에서는 "패턴 단계(모드 2)"를 사용하여 공정 온도를 900°C로 설정합니다. 그런 다음 실행 기능을 눌러 프로그램을 → 실행합니다.

- 온도가 900°C에 도달하면 건조 N 2 밸브를 닫고 건조 O 2 밸브(O 2 유량 = 1L/m)를 열고2시간 동안 유지합니다.

알림: 노란색 방에서 2.1.9-2.1.16단계를 수행합니다. - 스핀 코터를 사용하여 산화된 Si 기판을 계면활성제(OAP)로 코팅한 다음 핫플레이트에서 110°C에서 90초 동안 굽습니다.

- 계면활성제 코팅 후, 스핀 코터를 이용하여 포토레지스트(예를 들어, ZEP520A)로 Si 기판을 코팅한 후, 핫플레이트 상에서 180°C에서 5분 동안 베이크한다.

- 계면활성제와 포토레지스트가 포함된 Si 기판을 전자빔(EB) 라이터에 로드합니다.

- EB 라이터에서 디자인 파일(2.1.2단계에서 준비)을 읽고 작업 파일(WEC 파일)을 만듭니다. WEC 파일에서 선량량을 120μC/cm2 로 설정합니다. 기판 로딩이 완료되면 단일 노출 버튼을 클릭하여 EB 노출 을 수행합니다.

- 노출이 끝나면 웨이퍼 운반 → 언로드를 클릭하여 EB 라이터에서 기판을 언로드합니다.

- 드래프트 챔버에서 포토레지스트 현상액(ZED)과 현상액용 헹굼(ZMD)을 준비합니다. 노출된 Si 기판을 실온에서 60초 동안 현상액에 담그십시오.

- 현상액으로부터 Si 기판을 제거하고,N2 가스로 기판을 건조시킨다.

- 현상된 Si 기판을 핫플레이트에 올려 놓고 110°C에서 90초 동안 소성한다.

- EB 노출 및 현상의 결과로 공기에 노출된SiO2 층의 일부를 제거하기 위해 Si 기질을 완충된 불산(BHF-63SE)에 1분 동안 담그십시오.

- 유기 포토레지스트 제거제(예를 들어, Hakuri-104)에 15분 동안 침지하여 Si 기판으로부터 포토레지스트를 제거한다.

- Si 기판을 0.5% 희석된 불화수소산에 4분 동안 담그면 윈도우 영역에서 얇은 천연 산화물을 제거하지만SiO2 마스크는 유지합니다. 그런 다음 초고진공 화학 기상 증착(UHV-CVD) 챔버에 로드하여 Ge를 성장시킵니다. 그림 2 는 본 작업에 사용된 UHV-CVD 시스템을 보여줍니다.

- 에피택셜 Ge 성장

- SEG 마스크(단계 2.1에서와 같이 제작됨)가 있는 Si 기판을 로드 잠금 챔버에 로드합니다.

- 작동 컴퓨터에 표시된 레시피 탭에서 버퍼/주 성장 온도를 설정합니다. SEG Ge 층이 인접한 층과 합쳐지도록 Ge의 주요 성장 기간을 결정합니다. 주요 성장에 대한 지속기간을 결정하기 위해, 평면내/횡방향26에서의 성장을 결정하는 {113}면에서의 Ge의 성장률을 고려한다. 본 연구에서, 주요 성장에 대한 지속 시간을 650°C 및 700°C에 대해 각각 270분 및 150분으로 설정한다.

- 메인 창에서 시작을 클릭하면 Si 기판이 자동으로 성장 챔버로 전송됩니다.

참고: 에피택셜 Ge 성장에 대한 프로토콜(단계 2.2.4-2.2.7)이 자동으로 처리됩니다. - 저온(≈380°C)에서 로딩된 Si 기판 상에서 Ge 버퍼를 성장시킨다. Ar중 9%로 희석된 GeH4를 원료 가스로서 사용하고, 완충액 성장 동안 0.5 Pa 동안GeH4 의 분압을 유지한다.

- 고온에서 Ge 주층을 성장시킵니다. 주요 성장 동안 0.8 Pa에 대한 GeH4 의 분압을 유지하십시오. 본 연구에서, SEG Ge를 둥근 형상 단면과 {113} 패싯 단면과 비교하기 위해 주 성장 온도에 대해 650 및 700 °C의 두 가지 다른 온도를 사용한다25.

참고: (001) 평면에서 Ge의 성장률은 온도와 무관하게 11.7nm/min이었습니다. - SEG Ge의 진화와 그 유착을 시각화하기 위해 다른 Si 기판에 10nm 두께의 Si0.3Ge0.7 경계층을 주기적으로 삽입하여 Ge 성장을 수행합니다. Si0.3Ge0.7층은Si2H6및 GeH4 가스를 사용하여 형성되었다. Si0.3Ge0.7층 성장 중에, Si2H6가스의 분압을 0.02Pa로,GeH4가스의 분압을 0.8Pa로 설정한다.

- Si 기판이 성장 챔버에서 로드 잠금 챔버로 자동 이송됨에 따라 로드 잠금 챔버를 환기시키고 Si 기판을 수동으로 언로드합니다.

- 에칭 피트 밀도(EPD) 측정

- 초음파 세척기를 사용하여 32 mg의 I2 를 67 mL의 CH3COOH에 용해시킨다.

- I2-용해된CH3COOH, 20 mL의HNO3, 및 10 mL의 HF를 혼합한다.

- 에칭 피트를 형성하기 위해 Ge 성장 Si 기판을 CH 3COOH / HNO3 / HF / I2 용액에 5-7 초 동안 담그십시오.

- 광학 현미경(일반적으로 100x)으로 에칭된 Ge 표면을 관찰하여 에칭된 피트가 성공적으로 형성되었는지 확인합니다.

- 원자력 현미경(AFM)을 사용하여 에칭된 피트를 계산합니다. 에칭된 Ge 샘플을 AFM 스테이지에 놓은 다음 자동 접근을 클릭하여 프로브에 접근합니다.

- AFM과 통합된 광학 현미경을 사용하여 관찰 영역을 결정하고 5개의 서로 다른 10μm x 10μm 영역을 스캔합니다. 진폭 감쇠 계수는 자동으로 결정됩니다.

- TEM 관찰

- 집속 된 Ge 이온 빔 (FIB 마이크로 샘플링 방법)을 사용하여 유착 / 블랭킷 Ge 층에서 TEM 표본을 채취합니다 (27).

- Ar 이온을 사용하여 이온 밀링 시스템에서 TEM 시편을 연마합니다. 현재 작업에서는 단면 관찰을 위해 TEM 표본을 [110] 방향으로 150-500nm로, 평면도 관찰을 위해 [001] 방향으로 200nm가 되도록 얇게 만듭니다.

- 평면도 TEM 시편의 경우 Ge 층의 상단 표면을 비정질 층으로 보호한 다음 Ge 층의 하단(기판) 쪽에서 얇게 만듭니다.

- 200kV의 가속 전압에서 TEM 관찰을 수행합니다. 두꺼운(500nm) TEM 표본을 관찰하기 위해 단면 명시야 스캐닝 TEM(STEM) 관찰을 수행합니다.

- Si0.3Ge 0.7경계층이 있는 유착 Ge의 경우 200kV의 가속 전압에서 단면 고각 환형 암시야(HAADF) STEM 관찰을 수행합니다.

결과

이론적 계산

그림 3은 6가지 유형의 유착된 Ge 레이어에서 계산된 TD의 궤적을 보여줍니다. 여기서는 조리개 비율(APR)을 W창/(W창 + W마스크)로 정의합니다. 도 3a 는 APR=0.8의 Ge가 합쳐진 둥근 형상의 SEG 원점을 나타낸다. 여기에 2/6 TD가 갇혀 있습니?...

토론

본 연구에서, 4 x 107/cm2 의 TDD를 실험적으로 나타내었다. 추가 TDD 감소를 위해 프로토콜 내에는 주로 SEG 마스크 준비 및 에피택셜 Ge 성장의 2가지 중요한 단계가 있습니다.

그림 4에 표시된 모델은 APR, W창 / (W창 + W마스크)가 0.1만큼 작을 때 유착 된 Ge에서 TDD가 107 / cm2보다 낮게 감소 될 수 있음을 나...

공개

저자는 공개 할 것이 없습니다.

감사의 말

이 작업은 일본 문부과학성(MEXT)의 일본 과학 진흥회(JSPS) KAKENHI(17J10044)의 재정 지원을 받았습니다. 제조 공정은 일본 문부과학성의 "나노기술 플랫폼"(프로젝트 번호 12024046)의 지원을 받았습니다. 저자는 TEM 관찰에 도움을 준 도쿄 대학의 K. Yamashita 씨와 S. Hirata 씨에게 감사의 뜻을 전합니다.

자료

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

참고문헌

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

재인쇄 및 허가

JoVE'article의 텍스트 или 그림을 다시 사용하시려면 허가 살펴보기

허가 살펴보기This article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. 판권 소유