È necessario avere un abbonamento a JoVE per visualizzare questo. Accedi o inizia la tua prova gratuita.

Method Article

Calcolo teorico e verifica sperimentale per la riduzione della dislocazione in strati epitassiali di germanio con vuoti semicilindrici su silicio

In questo articolo

Riepilogo

Il calcolo teorico e la verifica sperimentale sono proposti per una riduzione della densità di dislocazione di filettatura (TD) in strati epitassiali di germanio con vuoti semicilindrici su silicio. Vengono presentati calcoli basati sull'interazione di TD e superficie tramite forza dell'immagine, misurazioni TD e osservazioni al microscopio elettronico a trasmissione dei TD.

Abstract

La riduzione della densità di dislocazione della filettatura (TDD) nel germanio epitassiale (Ge) su silicio (Si) è stata una delle sfide più importanti per la realizzazione di circuiti fotonici monoliticamente integrati. Il presente articolo descrive i metodi di calcolo teorico e di verifica sperimentale di un nuovo modello per la riduzione della TDD. Il metodo di calcolo teorico descrive la flessione delle dislocazioni di filettatura (TD) in base all'interazione di TD e superfici di crescita non planari di crescita epitassiale selettiva (SEG) in termini di forza dell'immagine di dislocazione. Il calcolo rivela che la presenza di vuoti sulle maschere SiO2 aiuta a ridurre il TDD. La verifica sperimentale è descritta dal germanio (Ge) SEG, utilizzando un metodo di deposizione chimica da vapore ad altissimo vuoto e osservazioni TD del Ge cresciuto tramite incisione e microscopio elettronico a trasmissione in sezione trasversale (TEM). Si suggerisce fortemente che la riduzione del TDD sarebbe dovuta alla presenza di vuoti semicilindrici sopra le maschere SiO2 SEG e alla temperatura di crescita. Per la verifica sperimentale, gli strati di Ge epitassiale con vuoti semicilindrici si formano come risultato del SEG degli strati di Ge e della loro coalescenza. I TDD ottenuti sperimentalmente riproducono i TDD calcolati in base al modello teorico. Le osservazioni TEM in sezione trasversale rivelano che sia la terminazione che la generazione di TD avvengono a vuoti semicilindrici. Le osservazioni TEM in pianta rivelano un comportamento unico dei TD in Ge con vuoti semicilindrici (cioè, i TD sono piegati per essere paralleli alle maschere SEG e al substrato Si).

Introduzione

L'epitassial Ge su Si ha attirato notevoli interessi come piattaforma di dispositivi fotonici attivi poiché Ge può rilevare / emettere luce nel campo di comunicazione ottica (1,3-1,6 μm) ed è compatibile con le tecniche di elaborazione Si CMOS (complementary metal oxide semiconductor). Tuttavia, poiché la mancata corrispondenza del reticolo tra Ge e Si è grande come il 4,2%, le dislocazioni di filettatura (TD) si formano negli strati epitassiali di Ge su Si ad una densità di ~ 109 / cm2. Le prestazioni dei dispositivi fotonici Ge sono deteriorate dai TD perché i TD funzionano come centri di generazione di portatori nei fotorivelatori Ge (PD) e modulatori (MOD) e come centri di ricombinazione della portante nei diodi laser (LD). A loro volta, aumenterebbero la corrente di dispersione inversa (perdita J) nei PD e MOD 1,2,3 e la corrente di soglia (Jth) nei LD 4,5,6.

Sono stati segnalati vari tentativi di ridurre la densità TD (TDD) in Ge su Si (Figura supplementare 1). La ricottura termica stimola il movimento dei TD portando alla riduzione del TDD, tipicamente a 2 x 107/cm2. Lo svantaggio è la possibile mescolanza di Si e Ge e la diffusione di droganti in Ge come il fosforo 7,8,9 (figura supplementare 1a). Lo strato tampone graduato SiGe 10,11,12 aumenta gli spessori critici e sopprime la generazione di TD portando alla riduzione del TDD, tipicamente a 2 x 10 6/cm2. Lo svantaggio qui è che il tampone spesso riduce l'efficienza di accoppiamento della luce tra i dispositivi Ge e le guide d'onda Si sottostanti (Figura supplementare 1b). L'intrappolamento del rapporto di aspetto (ART)13,14,15 è un metodo di crescita epitassiale selettiva (SEG) e riduce i TD intrappolando i TD alle pareti laterali di spesse trincee di SiO 2, tipicamente a <1 x 10 6 / cm 2. Il metodo ART utilizza una maschera SiO 2 spessa per ridurre il TDD in Ge rispetto alle maschere SiO2, che si trova molto al di sopra di Si e ha lo stesso inconveniente (Figura supplementare 1b,1c). La crescita di Ge sui semi del pilastro Si e la ricottura 16,17,18 sono simili al metodo ART, consentendo l'intrappolamento TD con l'elevato rapporto di aspetto della crescita di Gue, a <1 x 10 5 / cm2. Tuttavia, la ricottura ad alta temperatura per la coalescenza Ge presenta gli stessi inconvenienti nella figura supplementare 1a-c (figura supplementare 1d).

Per ottenere una crescita epitassiale Ge a basso TDD su Si che sia libera dagli svantaggi dei metodi sopra menzionati, abbiamo proposto una riduzione del TDD indotta dalla coalescenza19,20 sulla base delle seguenti due osservazioni chiave riportate finora nella crescita di SEG Ge 7,15,21,22,23 : 1) i TD sono piegati per essere normali alle superfici di crescita (osservate dal microscopio elettronico a trasmissione in sezione trasversale (TEM)), e 2) la coalescenza degli strati di SEG Ge provoca la formazione di vuoti semicilindrici sopra le maschere di SiO2.

Abbiamo ipotizzato che i TD siano piegati a causa della forza dell'immagine dalla superficie di crescita. Nel caso di Ge su Si, la forza dell'immagine genera tensioni di taglio di 1,38 GPa e 1,86 GPa per dislocazioni di viti e dislocazioni di spigoli a distanze di 1 nm dalle superfici libere, rispettivamente19. Le sollecitazioni di taglio calcolate sono significativamente maggiori della sollecitazione di Peierls di 0,5 GPa riportata per dislocazioni di 60° in Ge24. Il calcolo prevede la riduzione del TDD negli strati di Ge SEG su base quantitativa ed è in buon accordo con la crescita del SEG Ge19. Le osservazioni TEM dei TD vengono effettuate per comprendere i comportamenti dei TD nella crescita di SEG Ge presentata su Si20. La riduzione TDD indotta dalla forza dell'immagine è priva di ricottura termica o strati tampone spessi, ed è quindi più adatta per l'applicazione di dispositivi fotonici.

In questo articolo, descriviamo i metodi specifici per il calcolo teorico e la verifica sperimentale impiegati nel metodo di riduzione TDD proposto.

Protocollo

1. Procedura teorica di calcolo

- Calcola le traiettorie dei TD. Nel calcolo, supponiamo che le maschere SEG siano abbastanza sottili da ignorare l'effetto ART sulla riduzione TDD.

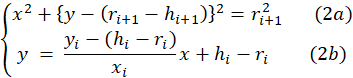

- Determinare le superfici di crescita ed esprimerle per equazione. Ad esempio, esprimere l'evoluzione temporale di una sezione trasversale di forma rotonda di uno strato SEG Ge con il parametro di evoluzione temporale n = i, altezze SEG Ge (h i) e raggi SEG Ge (r i), come mostrato nel video supplementare 1a ed Eq. (1):

- Determinare le direzioni normali per una posizione arbitraria sulle superfici di crescita. Per la sezione trasversale di forma rotonda SEG Ge, descrivere la linea normale in (x i , yi) come , mostrata nel video supplementare 1b come

una linea rossa. Quindi, ottenere lo spigolo del TD (x i+1 , y i+1) dal punto (x i , y i) risolvendo le seguenti equazioni simultanee:

una linea rossa. Quindi, ottenere lo spigolo del TD (x i+1 , y i+1) dal punto (x i , y i) risolvendo le seguenti equazioni simultanee:

- Calcolare una traiettoria di un TD in base alla posizione della generazione TD (x 0, 0), come mostrato nel video supplementare 1c. In altre parole, una traiettoria per un TD arbitrario può essere calcolata con il metodo descritto sopra.

- Calcolare il TDD assumendo che i TD penetrino nella superficie inferiore e contribuiscano alla riduzione del TDD (cioè, i TD al di sotto del punto in cui gli strati di SEG Ge si fondono sono intrappolati da vuoti semicilindrici e non appaiono mai sulla superficie superiore).

- Determinare le superfici di crescita ed esprimerle per equazione. Ad esempio, esprimere l'evoluzione temporale di una sezione trasversale di forma rotonda di uno strato SEG Ge con il parametro di evoluzione temporale n = i, altezze SEG Ge (h i) e raggi SEG Ge (r i), come mostrato nel video supplementare 1a ed Eq. (1):

2. Procedura di verifica sperimentale

- Preparazione maschera SEG

- Prima della fabbricazione delle maschere SEG, definire le aree di crescita Ge preparando un file di progettazione. Nel presente lavoro, preparare modelli di linee e spazi allineati alla direzione [110] e alle aree delle finestre Si di forma quadrata di 4 mm di larghezza utilizzando software commerciale (ad esempio, AutoCAD).

- Determinare il design delle maschere SEG (in particolare lafinestra W e lamaschera W) utilizzando il software. Wwindow è la larghezza della finestra (Si seed width) e Wmask è la larghezza della maschera SiO2 , in modo tale che gli strati SEG Ge possano fondersi con quelli adiacenti. Determinare lafinestra W e lamaschera W disegnando rettangoli facendo clic su Apri file → struttura → rettangolo o polilinea.

Nota : la larghezza dei rettangolidiventa finestra W e l'intervallo dei rettangolidiventa maschera W. Nel presente lavoro, i valori minimi dellafinestra W e dellamaschera W sono rispettivamente 0,5 μm e 0,3 μm, che sono limitati dalla risoluzione nel sistema di litografia EB impiegato. - Come riferimenti, disegna aree della finestra Si di forma quadrata di 4 mm di larghezza D, considerate come aree coperte. Fare clic su Apri file → struttura → rettangolo o polilinea per disegnare la finestra Si di forma quadrata. Utilizzare gli schemi illustrati nella Figura 1 per preparare i modelli di linee e spazi e l'area coperta quadrata di 4 mm.

- Preparare substrati p-Si (001) drogati con B con resistività di 1-100 Ω∙cm. Nel presente lavoro, utilizzare substrati di Si da 4 pollici. Pulire le superfici del substrato con la soluzione di Piranha (una miscela di 20 ml di H2 O 2 al30% e 80 ml di H2SO 4 al 96%.

- Aprire il coperchio di un forno tubolare e caricare i substrati di Si nel forno utilizzando una bacchetta di vetro. Nel presente lavoro, ossidare 10 substrati di Si contemporaneamente.

- Iniziare a soffiare il gas secco N2 nel forno aprendo la valvola del gas. Quindi, impostare la portata del gas su 0,5 L / m controllando la valvola.

- Impostare la temperatura di ricottura modificando il programma. Nel presente lavoro, utilizzare "pattern step (mode 2)" e impostare la temperatura di processo su 900 °C. Quindi, eseguire il programma premendo la funzione → eseguire.

- Quando la temperatura raggiunge i 900 °C, chiudere la valvola N 2 a secco, aprire la valvola O 2 a secco (flusso O 2 = 1 L/m) e conservare per2 ore.

NOTA: eseguire i passaggi 2.1.9-2.1.16 in una stanza gialla. - Rivestire i substrati di Si ossidato con un tensioattivo (OAP) utilizzando uno spin coater e quindi cuocere a 110 °C per 90 s su una piastra riscaldante.

- Dopo il rivestimento del tensioattivo, rivestire i substrati di Si con un fotoresist (ad esempio, ZEP520A) utilizzando un rivestimento di rotazione e quindi cuocere a 180 °C per 5 minuti su una piastra elettrica.

- Caricare i substrati di Si con il tensioattivo e fotoresistere in un writer a fascio di elettroni (EB).

- Leggere il file di progettazione (preparato al punto 2.1.2) nel writer EB e creare un file di operazione (file WEC). Impostare la quantità di dose come 120 μC/cm2 nel file WEC. Al termine del caricamento del substrato, eseguire l'esposizione EB facendo clic sul pulsante di esposizione singola .

- Scaricare il substrato dal writer EB facendo clic su wafer carry → scaricare al termine dell'esposizione.

- Preparare uno sviluppatore photoresist (ZED) e un risciacquo per lo sviluppatore (ZMD) in una camera di bozza. Immergere i substrati di Si esposti nello sviluppatore per 60 s a temperatura ambiente.

- Rimuovere i substrati di Si dallo sviluppatore, quindi asciugare il substrato con gas N2 .

- Mettere i substrati di Si sviluppati su una piastra riscaldante per cuocere a 110 °C per 90 s.

- Immergere i substrati di Si in un acido fluoridrico tamponato (BHF-63SE) per 1 minuto al fine di rimuovere parte degli strati di SiO2 esposti all'aria come risultato dell'esposizione e dello sviluppo di EB.

- Rimuovere il fotoresist dai substrati di Si immergendolo in un dispositivo di rimozione del fotoresist organico (ad esempio, Hakuri-104) per 15 minuti.

- Immergere i substrati di Si in acido fluoridrico diluito allo 0,5% per 4 minuti per rimuovere il sottile ossido nativo nelle regioni della finestra, ma per mantenere le maschere SiO2 . Quindi caricare su una camera di deposizione chimica da vapore ad ultraalto vuoto (UHV-CVD) per far crescere Ge. La figura 2 mostra il sistema UHV-CVD utilizzato nel presente lavoro.

- Crescita di Ge epitassiale

- Caricare il substrato di Si con maschere SEG (fabbricate come al punto 2.1) in una camera di blocco del carico.

- Impostare la temperatura di crescita del buffer/principale nella scheda Ricetta visualizzata sul computer operativo. Determinare le durate per la crescita principale di Ge in modo che gli strati di SEG Ge si coalizzino con quelli adiacenti. Per decidere le durate per la crescita principale, si consideri il tasso di crescita di Ge sui piani {113}, che determina la crescita nella direzione in-plane/lateral26. Nel presente lavoro, impostare le durate per la crescita principale come 270 min e 150 min per 650 °C e 700 °C, rispettivamente.

- Fare clic su Start nella finestra principale, quindi il substrato di Si viene automaticamente trasferito nella camera di crescita.

NOTA: Il protocollo sulla crescita epitassiale di Ge (fasi 2.2.4-2.2.7) viene elaborato automaticamente. - Tampone Ge di crescita sul substrato di Si caricato a bassa temperatura (≈380 °C). Utilizzare GeH 4 diluito al 9% in Ar come gas sorgente e mantenere la pressione parziale di GeH4 per 0,5 Pa durante la crescita del tampone.

- Coltiva lo strato principale di Ge a una temperatura elevata. Mantenere la pressione parziale di GeH4 per 0,8 Pa durante la crescita principale. Nel presente lavoro, utilizzare due diverse temperature di 650 e 700 °C per la temperatura di crescita principale al fine di confrontare SEG Ge con una sezione trasversale di forma rotonda e con una sezione trasversale a {113} sfaccettature25.

NOTA: Il tasso di crescita di Ge sul piano (001) è stato di 11,7 nm/min indipendente dalla temperatura. - Al fine di visualizzare l'evoluzione di SEG Ge e la loro coalescenza, eseguire la crescita di Ge con inserimento periodico di strati di demarcazione Si0.3Ge0.7 spessi 10 nm su un altro substrato di Si. Gli strati di Si 0,3 Ge0,7sono stati formati utilizzando gas Si2H6 e GeH4. Durante la crescita dello strato Si 0,3 Ge 0,7, impostare la pressione parziale del gas Si2H6 a 0,02 Pa e la pressione parziale del gas GeH4 a0,8Pa.

- Poiché il substrato di Si viene trasferito automaticamente dalla camera di crescita alla camera di blocco del carico, sfiatare la camera di blocco del carico e scaricare manualmente il substrato di Si.

- Misure della densità della fossa di incisione (EPD)

- Sciogliere 32 mg di I2 in 67 ml di CH3COOH utilizzando una macchina per la pulizia ad ultrasuoni.

- Mescolare il COOH CH 3 disciolto I2, 20 mL di HNO3e 10 mL di HF.

- Immergere i substrati di Si Ge-grown nella soluzione CH 3COOH/HNO3/HF/I2 per 5-7 s per formare fosse incise.

- Osservare le superfici Ge incise con un microscopio ottico (tipicamente 100x) per assicurarsi che le fosse incise si formino con successo.

- Utilizzare un microscopio a forza atomica (AFM) per contare le fosse incise. Posizionare il campione Ge inciso su uno stadio AFM, quindi avvicinarsi alla sonda facendo clic su avvicinamento automatico.

- Decidi l'area di osservazione utilizzando un microscopio ottico integrato con un AFM e scansiona cinque diverse aree da 10 μm x 10 μm. Il fattore di smorzamento dell'ampiezza viene determinato automaticamente.

- Osservazioni TEM

- Prelevare campioni di TEM dagli strati di Ge coalesced/coperta utilizzando un fascio di ioni Ge focalizzato (metodo di microcampionamento FIB)27.

- Lucidare i campioni TEM in un sistema di macinazione ionica utilizzando ioni Ar. Nel presente lavoro, assottigliare i campioni TEM per le osservazioni in sezione trasversale a 150-500 nm nella direzione [110] e per le osservazioni in pianta per essere 200 nm nella direzione [001].

- Per i campioni TEM in pianta, proteggere le superfici superiori degli strati di Ge con strati amorfi e quindi assottigliarsi dal lato inferiore (substrato) degli strati di Ge.

- Eseguire osservazioni TEM con una tensione di accelerazione di 200 kV. Eseguire osservazioni TEM (STEM) a scansione a campo chiaro in sezione trasversale per osservare campioni TEM spessi (500 nm).

- Per un Ge coalescente con strati di demarcazione Si0,3Ge0,7, eseguire osservazioni STEM in campo anulare ad alto angolo trasversale (HAADF) sotto una tensione di accelerazione di 200 kV.

Risultati

Calcolo teorico

La Figura 3 mostra le traiettorie calcolate dei TD in 6 tipi di strati Ge coalescenti: qui, definiamo il rapporto di apertura (APR) come finestra W /(finestra W +maschera W). La figura 3a mostra un Ge coalescente di origine SEG di forma rotonda di APR = 0,8. Qui, 2/6 TD sono intrappolati.

Discussione

Nel presente lavoro, sono stati mostrati sperimentalmente TDD di 4 x 107/cm2 . Per un'ulteriore riduzione del TDD, ci sono principalmente 2 passaggi critici all'interno del protocollo: preparazione della maschera SEG e crescita del Ge epitassiale.

Il nostro modello mostrato in Figura 4 indica che il TDD può essere ridotto al di sotto di 107/cm2 in Ge coalescente quando APR, W window/(Wwindow +W mask

Divulgazioni

Gli autori non hanno nulla da rivelare.

Riconoscimenti

Questo lavoro è stato sostenuto finanziariamente dalla Japan Society for the Promotion of Science (JSPS) KAKENHI (17J10044) dal Ministero dell'Istruzione, della Cultura, dello Sport, della Scienza e della Tecnologia (MEXT), Giappone. I processi di fabbricazione sono stati supportati da "Nanotechnology Platform" (progetto n. 12024046), MEXT, Giappone. Gli autori desiderano ringraziare il signor K. Yamashita e la signora S. Hirata, dell'Università di Tokyo, per il loro aiuto nelle osservazioni TEM.

Materiali

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

Riferimenti

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Ristampe e Autorizzazioni

Richiedi autorizzazione per utilizzare il testo o le figure di questo articolo JoVE

Richiedi AutorizzazioneThis article has been published

Video Coming Soon