Se requiere una suscripción a JoVE para ver este contenido. Inicie sesión o comience su prueba gratuita.

Method Article

Cálculo teórico y verificación experimental para la reducción de la dislocación en capas epitaxiales de germanio con huecos semicilíndricos en silicio

En este artículo

Resumen

Se propone el cálculo teórico y la verificación experimental para una reducción de la densidad de dislocación de roscado (TD) en capas epitaxiales de germanio con huecos semicilíndricos en silicio. Se presentan cálculos basados en la interacción de TD y superficie a través de la fuerza de imagen, mediciones de TD y observaciones de microscopio electrónico de transmisión de TD.

Resumen

La reducción de la densidad de dislocación de roscado (TDD) en germanio epitaxial (Ge) sobre silicio (Si) ha sido uno de los desafíos más importantes para la realización de circuitos fotónicos monolíticamente integrados. El presente artículo describe métodos de cálculo teórico y verificación experimental de un nuevo modelo para la reducción de TDD. El método de cálculo teórico describe la flexión de las dislocaciones de roscado (TD) basadas en la interacción de TD y superficies de crecimiento no planas de crecimiento epitaxial selectivo (SEG) en términos de fuerza de imagen de dislocación. El cálculo revela que la presencia de huecos en las máscaras deSiO2 ayuda a reducir el TDD. La verificación experimental se describe mediante SEG de germanio (Ge), utilizando un método de deposición química de vapor de ultra alto vacío y observaciones TD del Ge cultivado a través de grabado y microscopio electrónico de transmisión transversal (TEM). Se sugiere encarecidamente que la reducción de TDD se deba a la presencia de huecos semicilíndricos sobre las máscaras de SiO2 SEG y la temperatura de crecimiento. Para la verificación experimental, se forman capas epitaxiales de Ge con huecos semicilíndricos como resultado de SEG de capas de Ge y su coalescencia. Los TDD obtenidos experimentalmente reproducen los TDD calculados basados en el modelo teórico. Las observaciones transversales de TEM revelan que tanto la terminación como la generación de TD ocurren en vacíos semicilíndricos. Las observaciones TEM de vista en planta revelan un comportamiento único de los TD en Ge con vacíos semicilíndricos (es decir, los TD se doblan para ser paralelos a las máscaras SEG y al sustrato Si).

Introducción

Epitaxial Ge en Si ha atraído intereses sustanciales como una plataforma de dispositivo fotónico activo ya que Ge puede detectar / emitir luz en el rango de comunicación óptica (1.3-1.6 μm) y es compatible con las técnicas de procesamiento de Si CMOS (semiconductor complementario de óxido metálico). Sin embargo, dado que el desajuste de la red entre Ge y Si es tan grande como 4.2%, las dislocaciones de roscado (TD) se forman en capas epitaxiales de Ge en Si a una densidad de ~ 109 / cm2. El rendimiento de los dispositivos fotónicos Ge se ve deteriorado por los TD porque los TD funcionan como centros de generación de portadoras en fotodetectores de Ge (PD) y moduladores (MOD), y como centros de recombinación de portadores en diodos láser (LD). A su vez, aumentarían la corriente de fuga inversa (fuga J) en PD y MODs 1,2,3, y la corriente umbral (Jth) en LD 4,5,6.

Se han reportado varios intentos para reducir la densidad de TD (TDD) en Ge en Si (Figura Suplementaria 1). El recocido térmico estimula el movimiento de los TD que conducen a la reducción de TDD, típicamente a 2 x 107/cm2. El inconveniente es la posible mezcla de Si y Ge y la difusión de dopantes en Ge como el fósforo 7,8,9 (Figura suplementaria 1a). La capa tampón graduada de SiGe 10,11,12 aumenta los espesores críticos y suprime la generación de TD que conduce a la reducción de TDD, típicamente a 2 x 10 6/cm2. El inconveniente aquí es que el búfer grueso reduce la eficiencia de acoplamiento de luz entre los dispositivos Ge y las guías de onda de Si debajo (Figura suplementaria 1b). El atrapamiento por relación de aspecto (ART)13,14,15 es un método de crecimiento epitaxial selectivo (SEG) y reduce los TD atrapando TD en las paredes laterales de zanjas gruesas de SiO 2, típicamente a <1 x 10 6/cm 2. El método ART utiliza una máscara gruesa deSiO2 para reducir TDD en Ge sobre las máscaras de SiO2, que se ubica muy por encima de Si y tiene el mismo inconveniente (Figura suplementaria 1b, 1c). El crecimiento de Ge en semillas de pilar de Si y recocido 16,17,18 es similar al método ART, lo que permite el atrapamiento de TD por el crecimiento de Ge de alta relación de aspecto, a <1 x 10 5/cm2. Sin embargo, el recocido a alta temperatura para la coalescencia de Ge tiene los mismos inconvenientes en la Figura Suplementaria 1a-c (Figura Suplementaria 1d).

Para lograr un crecimiento epitaxial de Ge de TDD bajo en Si que esté libre de los inconvenientes de los métodos mencionados anteriormente, hemos propuesto una reducción de TDD inducida por coalescencia 19,20 basada en las siguientes dos observaciones clave reportadas hasta ahora en el crecimiento de SEG Ge 7,15,21,22,23 : 1) los TD se doblan para ser normales a las superficies de crecimiento (observados por el microscopio electrónico de transmisión de sección transversal (TEM)), y 2) la coalescencia de las capas de SEG Ge da como resultado la formación de vacíos semicilíndricos sobre las máscaras de SiO2.

Hemos asumido que los TD están doblados debido a la fuerza de imagen de la superficie de crecimiento. En el caso de Ge en Si, la fuerza de imagen genera tensiones de cizallamiento de 1,38 GPa y 1,86 GPa para dislocaciones de tornillos y dislocaciones de bordes a distancias de 1 nm de las superficies libres, respectivamente19. Las tensiones de cizallamiento calculadas son significativamente mayores que la tensión de Peierls de 0,5 GPa reportada para dislocaciones de 60° en Ge24. El cálculo predice la reducción de TDD en las capas de Ge SEG sobre una base cuantitativa y está en buen acuerdo con el crecimiento de SEG Ge19. Las observaciones TEM de TD se llevan a cabo para comprender los comportamientos de TD en el crecimiento SEG Ge presentado en Si20. La reducción TDD inducida por la fuerza de la imagen está libre de recocido térmico o capas de amortiguación gruesas y, por lo tanto, es más adecuada para la aplicación de dispositivos fotónicos.

En este artículo, describimos métodos específicos para el cálculo teórico y la verificación experimental empleados en el método de reducción de TDD propuesto.

Protocolo

1. Procedimiento teórico de cálculo

- Calcular trayectorias de TD. En el cálculo, supongamos que las máscaras SEG son lo suficientemente delgadas como para ignorar el efecto ART en la reducción de TDD.

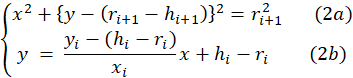

- Determine las superficies de crecimiento y expréselas mediante ecuaciones. Por ejemplo, exprese la evolución temporal de una sección transversal de forma redonda de una capa SEG Ge con el parámetro de evolución temporal n = i, las alturas SEG Ge (h i) y los radios SEG Ge (ri), como se muestra en el Video Suplementario 1a y Eq. (1):

- Determine las direcciones normales para una ubicación arbitraria en las superficies de crecimiento. Para la sección transversal de forma redonda SEG Ge, describa la línea normal en (x i , yi) como , que se muestra en el Video Suplementario 1b como

una línea roja. Luego, obtén la arista del TD (x i+1 , y i+1) del punto (x i , yi) resolviendo las siguientes ecuaciones simultáneas:

una línea roja. Luego, obtén la arista del TD (x i+1 , y i+1) del punto (x i , yi) resolviendo las siguientes ecuaciones simultáneas:

- Calcule una trayectoria de un TD dependiendo de la ubicación de la generación de TD (x 0, 0), como se muestra en el video suplementario 1c. En otras palabras, una trayectoria para un TD arbitrario puede calcularse mediante el método descrito anteriormente.

- Calcule TDD suponiendo que los TD penetran en la superficie inferior y contribuyen a la reducción de TDD (es decir, los TD por debajo del punto donde las capas de SEG Ge se unen están atrapados por vacíos semicilíndricos y nunca aparecen en la superficie superior).

- Determine las superficies de crecimiento y expréselas mediante ecuaciones. Por ejemplo, exprese la evolución temporal de una sección transversal de forma redonda de una capa SEG Ge con el parámetro de evolución temporal n = i, las alturas SEG Ge (h i) y los radios SEG Ge (ri), como se muestra en el Video Suplementario 1a y Eq. (1):

2. Procedimiento experimental de verificación

- Preparación de la máscara SEG

- Antes de la fabricación de máscaras SEG, defina las áreas de crecimiento de Ge preparando un archivo de diseño. En el presente trabajo, prepare patrones de línea y espacio alineados con la dirección [110] y áreas de ventana de Si de forma cuadrada de 4 mm de ancho utilizando software comercial (por ejemplo, AutoCAD).

- Determine el diseño de las máscaras SEG (en particular la ventana W yla máscara W) utilizando el software. La ventana W es el ancho de laventana (ancho de la semilla de Si) y la máscara W es el ancho de lamáscara SiO2 , de modo que las capas SEG Ge pueden unirse con las adyacentes. Determine laventana W y lamáscara W dibujando rectángulos haciendo clic en abrir archivo → estructura → rectángulo o polilínea.

NOTA: El ancho de los rectángulos se convierte enventana W y el intervalo de los rectángulos se convierte enmáscara W. En el presente trabajo, los valores mínimos deventana W ymáscara W son 0,5 μm y 0,3 μm, respectivamente, que están restringidos por la resolución en el sistema de litografía EB empleado. - Como referencias, dibuje áreas de ventanas de Si de forma cuadrada de 4 mm de ancho D, consideradas como las áreas de manta. Haga clic en Abrir archivo → estructura → rectángulo o polilínea para dibujar la ventana Si de forma cuadrada. Utilice los esquemas que se muestran en la figura 1 para preparar los patrones de línea y espacio y el área de la manta cuadrada de 4 mm.

- Preparar sustratos de p-Si (001) dopados con B con una resistividad de 1-100 Ω∙cm. En el presente trabajo, use sustratos de Si de 4 pulgadas. Limpie las superficies del sustrato con solución de piraña (una mezcla de 20 mL de 30% deH2O2 y 80 mL de 96%H2SO4) segúnsea necesario.

- Abra la tapa de un horno tubular y cargue los sustratos de Si en el horno con una varilla de vidrio. En el presente trabajo, oxide 10 sustratos de Si a la vez.

- Comience a soplar gasN2 seco en el horno abriendo la válvula de gas. Luego, ajuste el caudal de gas a 0,5 L / m controlando la válvula.

- Ajuste la temperatura de recocido cambiando el programa. En el presente trabajo, utilice el "paso de patrón (modo 2)" y ajuste la temperatura del proceso a 900 °C. Luego, ejecute el programa presionando la función → ejecutar.

- Cuando la temperatura alcance los 900 °C, cierre la válvula N 2 seca, abra la válvula de O 2 seca (flujo deO2 = 1 L/m) y manténgala durante2 h.

NOTA: Realice los pasos 2.1.9-2.1.16 en una sala amarilla. - Cubrir los sustratos de Si oxidado con un tensioactivo (OAP) con una recubridora de centrifugado y, a continuación, hornear a 110 °C durante 90 s en una placa calefactora.

- Después del recubrimiento con surfactante, cubra los sustratos de Si con una fotorresistencia (por ejemplo, ZEP520A) con una recubridora de centrifugado y luego hornee a 180 °C durante 5 minutos en una placa calefactora.

- Cargue los sustratos de Si con el surfactante y fotorresista en un escritor de haz de electrones (EB).

- Lea el archivo de diseño (preparado en el paso 2.1.2) en el escritor de EB y cree un archivo de operación (archivo WEC). Establezca la cantidad de dosis como 120 μC/cm2 en el archivo WEC. Cuando finalice la carga del sustrato, realice la exposición EB haciendo clic en el botón de exposición única .

- Descargue el sustrato del escritor EB haciendo clic en oblea transportar → descargar a medida que finaliza la exposición.

- Prepare un revelador de fotorresistencia (ZED) y un enjuague para el revelador (ZMD) en una cámara de tiro. Sumerja los sustratos de Si expuestos en el revelador durante 60 s a temperatura ambiente.

- Retire los sustratos de Si del revelador y luego seque el sustrato con gasN2 .

- Coloque los sustratos de Si desarrollados en una placa calefactora para hornear a 110 °C durante 90 s.

- Sumerja los sustratos de Si en un ácido fluorhídrico tamponado (BHF-63SE) durante 1 minuto para eliminar parte de las capas de SiO2 expuestas al aire como resultado de la exposición y el desarrollo de EB.

- Retire el fotoprotector de los sustratos de Si sumergiéndolo en un removedor de fotorresistencia orgánico (por ejemplo, Hakuri-104) durante 15 minutos.

- Sumerja los sustratos de Si en ácido fluorhídrico diluido al 0,5% durante 4 minutos para eliminar el óxido nativo delgado en las regiones de la ventana, pero para retener las máscaras de SiO2 . Luego cargue en una cámara de deposición química de vapor de ultra alto vacío (UHV-CVD) para cultivar Ge. La Figura 2 muestra el sistema UHV-CVD utilizado en el presente trabajo.

- Crecimiento de Ge epitaxial

- Cargue el sustrato de Si con máscaras SEG (fabricadas como en el paso 2.1) en una cámara de bloqueo de carga.

- Establezca la temperatura de crecimiento del búfer/principal en la pestaña Receta que se muestra en la computadora de operación. Determine las duraciones para el crecimiento principal de Ge de modo que las capas de SEG Ge se unan con las adyacentes. Para decidir las duraciones para el crecimiento principal, considere la tasa de crecimiento de Ge en los planos {113}, que determina el crecimiento en la dirección intraplano/lateral26. En el presente trabajo, establezca las duraciones para el crecimiento principal como 270 min y 150 min para 650 °C y 700 °C, respectivamente.

- Haga clic en Inicio en la ventana principal y, a continuación, el sustrato de Si se transfiere automáticamente a la cámara de crecimiento.

NOTA: El protocolo sobre el crecimiento epitaxial de Ge (pasos 2.2.4-2.2.7) se procesa automáticamente. - Tampón de cultivo de Ge sobre el sustrato de Si cargado a baja temperatura (≈380 °C). Use GeH 4 diluido al 9% en Ar como gas fuente y mantenga la presión parcial de GeH4 durante 0.5 Pa durante el crecimiento del tampón.

- Cultive la capa principal de Ge a una temperatura elevada. Mantenga la presión parcial de GeH4 durante 0.8 Pa durante el crecimiento principal. En el presente trabajo, utilice dos temperaturas diferentes de 650 y 700 °C para la temperatura de crecimiento principal con el fin de comparar SEG Ge con una sección transversal de forma redonda y con una sección transversal de {113} facetas25.

NOTA: La tasa de crecimiento de Ge en el plano (001) fue de 11,7 nm/min independientemente de la temperatura. - Para visualizar la evolución de SEG Ge y su coalescencia, realice el crecimiento de Ge con la inserción periódica de capas de demarcación de Si0.3Ge0.7 de 10 nm de espesor en otro sustrato de Si. Se formaron capas de Si0.3Ge0.7 utilizando gases Si2H6 y GeH4. Durante el crecimiento de la capa de Si 0.3 Ge0.7, establezca la presión parcial del gas Si2H6 en 0.02 Pa y la presión parcial del gas GeH4 en0.8 Pa.

- Como el sustrato de Si se transfiere automáticamente de la cámara de crecimiento a la cámara de bloqueo de carga, ventile la cámara de bloqueo de carga y descargue el sustrato de Si manualmente.

- Mediciones de densidad de pozo de grabado (EPD)

- Disuelva 32 mg de I2 en 67 ml de CH3COOH utilizando una máquina de limpieza ultrasónica.

- Mezclar el CH 3 COOH I2-disuelto, 20 mL de HNO3y 10 mL de HF.

- Sumerja los sustratos de Si cultivados en Ge-grown en la solución CH 3 COOH/HNO3/HF/I2 durante 5-7 s para formar fosas grabadas.

- Observe las superficies de Ge grabadas con un microscopio óptico (típicamente 100x) para asegurarse de que los hoyos grabados se formen con éxito.

- Emplee un microscopio de fuerza atómica (AFM) para contar los pozos grabados. Coloque la muestra de Ge grabada en una etapa AFM y, a continuación, acérquese a la sonda haciendo clic en enfoque automático.

- Decida el área de observación utilizando un microscopio óptico integrado con un AFM y escanee cinco áreas diferentes de 10 μm x 10 μm. El factor de amortiguación de amplitud se determina automáticamente.

- Observaciones de TEM

- Recoger muestras TEM de las capas de Ge fusionadas/manta utilizando un haz de iones de Ge enfocado (método de micromuestreo FIB)27.

- Pule las muestras TEM en un sistema de molienda de iones utilizando iones Ar. En el presente trabajo, los especímenes TEM delgados para observaciones transversales para que sean de 150-500 nm en la dirección [110], y para las observaciones de vista en planta sean de 200 nm en la dirección [001].

- Para especímenes TEM de vista en planta, proteja las superficies superiores de las capas de Ge con capas amorfas y, a continuación, adelgase desde el lado inferior (sustrato) de las capas de Ge.

- Realizar observaciones TEM bajo una tensión de aceleración de 200 kV. Realizar observaciones TEM (STEM) de escaneo de campo brillante de sección transversal para observar muestras TEM gruesas (500 nm).

- Para un Ge fusionado con capas de demarcación de Si 0.3 Ge0.7, realice observaciones STEM de campo oscuro anular de alto ángulo (HAADF) de sección transversal bajo un voltaje de aceleración de 200 kV.

Resultados

Cálculo teórico

La Figura 3 muestra las trayectorias calculadas de TD en 6 tipos de capas de Ge fusionadas: aquí, definimos la relación de apertura (APR) como W ventana / (ventana W + máscara W). La Figura 3a muestra un origen SEG de forma redonda fusionado Ge de APR = 0.8. Aquí, 2/6 TDs están atrapados.

Discusión

En el presente trabajo, se mostraron experimentalmente TDD de 4 x 107/cm2 . Para una mayor reducción de TDD, hay principalmente 2 pasos críticos dentro del protocolo: preparación de la máscara SEG y crecimiento epitaxial de GE.

Nuestro modelo que se muestra en la Figura 4 indica que TDD puede reducirse por debajo de 107 / cm2 en Ge fusionado cuando APR, ventana W / (ventana W +máscara

Divulgaciones

Los autores no tienen nada que revelar.

Agradecimientos

Este trabajo fue apoyado financieramente por la Sociedad Japonesa para la Promoción de la Ciencia (JSPS) KAKENHI (17J10044) del Ministerio de Educación, Cultura, Deportes, Ciencia y Tecnología (MEXT), Japón. Los procesos de fabricación fueron apoyados por "Plataforma de Nanotecnología" (proyecto No. 12024046), MEXT, Japón. Los autores desean agradecer al Sr. K. Yamashita y a la Sra. S. Hirata, de la Universidad de Tokio, por su ayuda en las observaciones de TEM.

Materiales

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

Referencias

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Reimpresiones y Permisos

Solicitar permiso para reutilizar el texto o las figuras de este JoVE artículos

Solicitar permisoThis article has been published

Video Coming Soon

ACERCA DE JoVE

Copyright © 2025 MyJoVE Corporation. Todos los derechos reservados