Zum Anzeigen dieser Inhalte ist ein JoVE-Abonnement erforderlich. Melden Sie sich an oder starten Sie Ihre kostenlose Testversion.

Method Article

Theoretische Berechnung und experimenteller Nachweis zur Versetzungsreduktion in Germanium-Epitaxieschichten mit semizylindrischen Hohlräumen auf Silizium

In diesem Artikel

Zusammenfassung

Theoretische Berechnungen und experimentelle Nachweise werden für eine Verringerung der Dichte der Gewindeversetzungen (TD) in Germanium-Epitaxieschichten mit semizylindrischen Hohlräumen auf Silizium vorgeschlagen. Es werden Berechnungen vorgestellt, die auf der Wechselwirkung von TDs und Oberfläche über Bildkraft, TD-Messungen und transmissionselektronenmikroskopische Beobachtungen von TDs basieren.

Zusammenfassung

Die Reduzierung der Gewindeversetzungsdichte (TDD) in epitaktischem Germanium (Ge) auf Silizium (Si) war eine der wichtigsten Herausforderungen für die Realisierung monolithisch integrierter photonischer Schaltkreise. Die vorliegende Arbeit beschreibt Methoden der theoretischen Berechnung und experimentellen Verifikation eines neuartigen Modells zur Reduktion von TDD. Die Methode der theoretischen Berechnung beschreibt die Biegung von Gewindeversetzungen (TDs) basierend auf der Wechselwirkung von TDs und nicht-planaren Wachstumsflächen des selektiven epitaktischen Wachstums (SEG) in Bezug auf die Versetzungsbildkraft. Die Berechnung zeigt, dass das Vorhandensein von Hohlräumen auf SiO2 -Masken dazu beiträgt, TDD zu reduzieren. Die experimentelle Verifizierung wird durch Germanium (Ge) SEG unter Verwendung einer chemischen Ultrahochvakuum-Gasphasenabscheidungsmethode und TD-Beobachtungen des gezüchteten Ge mittels Ätzen und Querschnittstransmissionselektronenmikroskop (TEM) beschrieben. Es wird stark vermutet, dass die TDD-Reduktion auf das Vorhandensein von halbzylindrischen Hohlräumen über den SiO2-SEG-Masken und der Wachstumstemperatur zurückzuführen ist. Zur experimentellen Überprüfung werden epitaktische Ge-Schichten mit halbzylindrischen Hohlräumen als Ergebnis von SEG von Ge-Schichten und deren Koaleszenz gebildet. Die experimentell erhaltenen TDDs reproduzieren die berechneten TDDs auf der Grundlage des theoretischen Modells. TEM-Beobachtungen im Querschnitt zeigen, dass sowohl die Terminierung als auch die Erzeugung von TDs in semizylindrischen Hohlräumen auftreten. Draufsicht-TEM-Beobachtungen zeigen ein einzigartiges Verhalten von TDs in Ge mit halbzylindrischen Hohlräumen (d.h. TDs sind so gebogen, dass sie parallel zu den SEG-Masken und dem Si-Substrat sind).

Einleitung

Epitaktisches Ge on Si hat als aktive photonische Bauelementplattform großes Interesse geweckt, da Ge Licht im optischen Kommunikationsbereich (1,3-1,6 μm) detektieren/emittieren kann und mit Si-CMOS-Verarbeitungstechniken (komplementärer Metalloxid-Halbleiter) kompatibel ist. Da die Gitterfehlanpassung zwischen Ge und Si jedoch bis zu 4,2% beträgt, bilden sich in Ge-Epitaxieschichten auf Si Gewindeversetzungen (TDs) mit einer Dichte von ~109/cm2. Die Leistung von photonischen Ge-Bauelementen wird durch TDs verschlechtert, da TDs als Trägererzeugungszentren in Ge-Photodetektoren (PDs) und Modulatoren (MODs) und als Ladungsträger-Rekombinationszentren in Laserdioden (LDs) fungieren. Im Gegenzug würden sie den Sperrleckstrom (J-Leck) in PDs und MODs 1,2,3 und den Schwellenstrom (Jth) in LDs 4,5,6 erhöhen.

Es wurde über verschiedene Versuche berichtet, die TD-Dichte (TDD) in Ge on Si zu reduzieren (ergänzende Abbildung 1). Das thermische Glühen stimuliert die Bewegung von TDs, was zu einer Reduzierung der TDD führt, typischerweise auf 2 x 107/cm2. Der Nachteil ist die mögliche Vermischung von Si und Ge und die Ausdiffusion von Dotierstoffen in Ge wie Phosphor 7,8,9 (Ergänzende Abbildung 1a). Die SiGe-abgestufte Pufferschicht 10,11,12 erhöht die kritischen Dicken und unterdrückt die Erzeugung von TDs, was zu einer Reduzierung der TDD führt, typischerweise auf 2 x 10 6/cm2. Der Nachteil hierbei ist, dass der dicke Puffer die Lichtkopplungseffizienz zwischen Ge-Bauelementen und darunter liegenden Si-Wellenleitern verringert (ergänzende Abbildung 1b). Aspect Ratio Trapping (ART)13,14,15 ist eine Methode des selektiven epitaktischen Wachstums (SEG) und reduziert TDs durch Einfangen von TDs an den Seitenwänden dickerSiO2-Gräben, typischerweise auf <1 x 10 6/cm2. Die ART-Methode verwendet eine dicke SiO2-Maske, um TDD in Ge gegenüber denSiO2-Masken zu reduzieren, die weit über Si liegen und den gleichen Nachteil aufweisen (ergänzende Abbildung 1b,1c). Das Ge-Wachstum auf Si-Säulensamen und das Glühenvon 16,17,18 ähneln der ART-Methode und ermöglichen das TD-Einfangen durch das hohe Aspektverhältnis Ge-Wachstum auf <1 x 10 5/cm2. Das Hochtemperaturglühen für die Ge-Koaleszenz hat jedoch die gleichen Nachteile in der ergänzenden Abbildung 1a-c (ergänzende Abbildung 1d).

Um ein epitaktisches Wachstum mit niedrigem TDD-Ge auf Si zu erreichen, das frei von den Nachteilen der oben genannten Methoden ist, haben wir eine Koaleszenz-induzierte TDD-Reduktion 19,20 vorgeschlagen, basierend auf den folgenden zwei Schlüsselbeobachtungen, die bisher im SEG Ge-Wachstum berichtet wurden 7,15,21,22,23 : 1) TDs werden so gebogen, dass sie senkrecht zu den Wachstumsoberflächen sind (beobachtet durch das Querschnittstransmissionselektronenmikroskop (TEM)), und 2) die Koaleszenz von SEG Ge-Schichten führt zur Bildung von halbzylindrischen Hohlräumen über denSiO2-Masken.

Wir haben angenommen, dass die TDs aufgrund der Bildkraft von der Wachstumsoberfläche gebogen werden. Im Fall von Ge auf Si erzeugt die Bildkraft 1,38 GPa und 1,86 GPa Schubspannungen für Schraubenversetzungen und Kantenversetzungen in Abständen von 1 nm von den freien Oberflächen bzw.19. Die berechneten Schubspannungen sind signifikant größer als die Peierls-Spannung von 0,5 GPa, die für 60°-Versetzungen in Ge24 angegeben wurde. Die Berechnung prognostiziert eine TDD-Reduktion in Ge-SEG-Schichten auf quantitativer Basis und stimmt gut mit dem SEG Ge-Wachstum19 überein. TEM-Beobachtungen von TDs werden durchgeführt, um das TD-Verhalten im vorgestellten SEG Ge-Wachstum auf Si20 zu verstehen. Die bildkraftinduzierte TDD-Reduktion ist frei von jeglichem thermischen Annealing oder dicken Pufferschichten und eignet sich daher besser für die Anwendung in photonischen Bauelementen.

In diesem Artikel beschreiben wir spezifische Methoden für die theoretische Berechnung und experimentelle Überprüfung, die in der vorgeschlagenen TDD-Reduktionsmethode verwendet werden.

Protokoll

1. Theoretisches Berechnungsverfahren

- Berechnen Sie Trajektorien von TDs. Nehmen Sie bei der Berechnung an, dass die SEG-Masken dünn genug sind, um den ART-Effekt auf die TDD-Reduktion zu ignorieren.

- Bestimmen Sie Wachstumsoberflächen und drücken Sie sie durch Gleichung(en) aus. Drücken Sie beispielsweise die zeitliche Entwicklung eines runden Querschnitts einer SEG Ge-Schicht mit dem Zeitentwicklungsparameter n = i, SEG Ge-Höhen (h i) und SEG Ge-Radien (ri) aus, wie im ergänzenden Video 1a und Gl. (1) gezeigt:

- Bestimmen Sie normale Richtungen für eine beliebige Position auf den Wachstumsflächen. Beschreiben Sie für das SEG Ge mit rundem Querschnitt die Normallinie bei (x i , yi) als

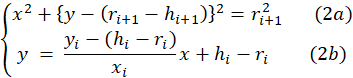

, die im ergänzenden Video 1b als rote Linie dargestellt ist. Erhalten Sie dann die Kante des TD (x i + 1 , y i + 1) vom Punkt (x i , y i), indem Sie die folgenden simultanen Gleichungen lösen:

, die im ergänzenden Video 1b als rote Linie dargestellt ist. Erhalten Sie dann die Kante des TD (x i + 1 , y i + 1) vom Punkt (x i , y i), indem Sie die folgenden simultanen Gleichungen lösen:

- Berechnen Sie eine Trajektorie eines TD in Abhängigkeit vom Ort der TD-Erzeugung (x 0, 0), wie in Ergänzendes Video 1c gezeigt. Mit anderen Worten, eine Trajektorie für einen beliebigen TD kann nach der oben beschriebenen Methode berechnet werden.

- Berechnen Sie die TDD unter der Annahme, dass TDs in die Bodenfläche eindringen und zur Verringerung der TDD beitragen (d. h. TDs unterhalb des Punktes, an dem SEG Ge-Schichten verschmelzen, werden von halbzylindrischen Hohlräumen eingeschlossen und erscheinen niemals auf der Oberseite).

- Bestimmen Sie Wachstumsoberflächen und drücken Sie sie durch Gleichung(en) aus. Drücken Sie beispielsweise die zeitliche Entwicklung eines runden Querschnitts einer SEG Ge-Schicht mit dem Zeitentwicklungsparameter n = i, SEG Ge-Höhen (h i) und SEG Ge-Radien (ri) aus, wie im ergänzenden Video 1a und Gl. (1) gezeigt:

2. Verfahren zur experimentellen Überprüfung

- Vorbereitung der SEG-Maske

- Definieren Sie vor der Herstellung von SEG-Masken die Wachstumsbereiche von Ge, indem Sie eine Designdatei erstellen. In der vorliegenden Arbeit werden Linien- und Raummuster, die auf die [110] Richtung ausgerichtet sind, und quadratische Si-Fensterflächen von 4 mm Breite mit kommerzieller Software (z. B. AutoCAD) vorbereitet.

- Bestimmen Sie das Design von SEG-Masken (insbesondereW-Fenster undW-Maske) mit der Software. Das W-Fenster ist die Fensterbreite (Si-Seed-Breite) und dieW-Maske ist die SiO2-Maskenbreite, so dass SEGGe-Schichten mit ihren benachbarten verschmelzen können. Bestimmen Sie dasW-Fenster und dieW-Maske, indem Sie Rechtecke zeichnen, indem Sie auf Datei öffnen → Struktur → Rechteck oder Polylinie klicken.

HINWEIS: Die Breite der Rechtecke wird zumW-Fenster und das Intervall der Rechtecke zurW-Maske. In der vorliegenden Arbeit liegen die Mindestwerte desW-Fensters und derW-Maske bei 0,5 μm bzw. 0,3 μm, die durch die Auflösung im verwendeten EB-Lithographiesystem eingeschränkt sind. - Zeichnen Sie als Referenzen quadratische Si-Fensterflächen mit einer Breite von 4 mm in der Breite D, die als Deckenflächen betrachtet werden. Klicken Sie auf Datei öffnen → Struktur → Rechteck oder Polylinie , um das quadratische Si-Fenster zu zeichnen. Verwenden Sie die in Abbildung 1 gezeigten Schaltpläne, um die Linien- und Abstandsmuster und die quadratische Deckenfläche von 4 mm vorzubereiten.

- Bereiten Sie B-dotierte p-Si (001) -Substrate mit einem spezifischen Widerstand von 1-100 Ω∙cm vor. Verwenden Sie in der vorliegenden Arbeit 4-Zoll-Si-Substrate. Reinigen Sie die Substratoberflächen bei Bedarf mit Piranha-Lösung (einer Mischung aus 20 ml 30% H2O2 und 80 ml 96%H2SO4).

- Öffnen Sie den Deckel eines Rohrofens und laden Sie die Si-Substrate mit einem Glasstab in den Ofen. In der vorliegenden Arbeit werden 10 Si-Substrate gleichzeitig oxidiert.

- Beginnen Sie, trockenes N2 -Gas in den Ofen zu blasen, indem Sie das Gasventil öffnen. Stellen Sie dann den Gasdurchfluss auf 0,5 l / m ein, indem Sie das Ventil steuern.

- Stellen Sie die Glühtemperatur ein, indem Sie das Programm ändern. Verwenden Sie in der vorliegenden Arbeit den "Musterschritt (Modus 2)" und stellen Sie die Prozesstemperatur auf 900 °C ein. Führen Sie dann das Programm aus, indem Sie Funktion drücken → ausführen.

- Wenn die Temperatur 900 °C erreicht, schließen Sie das trockene N 2 -Ventil, öffnen Sie das trockene O 2 -Ventil (O2 Durchfluss = 1 l / m) und halten Sie es 2 h lang.

HINWEIS: Führen Sie die Schritte 2.1.9 bis 2.1.16 in einem gelben Raum aus. - Die oxidierten Si-Substrate werden mit einem Tensid (OAP) mit einem Schleuderbeschichter bestreut und anschließend bei 110 °C 90 s auf einer Kochplatte gebacken.

- Nach der Tensidbeschichtung werden die Si-Substrate mit einem Fotolack (z. B. ZEP520A) mit einem Schleudercoater beschichtet und anschließend bei 180 °C 5 min auf einer Kochplatte gebacken.

- Laden Sie die Si-Substrate mit dem Tensid und dem Fotolack in einen Elektronenstrahlschreiber (EB).

- Lesen Sie die Konstruktionsdatei (vorbereitet in Schritt 2.1.2) im EB-Writer und erstellen Sie eine Arbeitsvorgangsdatei (WEC-Datei). Stellen Sie die Dosismenge in der WEC-Datei auf 120 μC/cm2 ein. Wenn die Substratbeladung abgeschlossen ist, führen Sie die EB-Belichtung durch, indem Sie auf die Schaltfläche Einzelbelichtung klicken.

- Entladen Sie das Substrat aus dem EB-Writer, indem Sie auf " Wafer Carry" → "Entladen " klicken, wenn die Belichtung beendet ist.

- Bereiten Sie einen Fotolackentwickler (ZED) und eine Spülung für den Entwickler (ZMD) in einer Zugkammer vor. Tauchen Sie die belichteten Si-Substrate für 60 s bei Raumtemperatur in den Entwickler.

- Entfernen Sie die Si-Substrate aus dem Entwickler und trocknen Sie das Substrat dann mit N2 -Gas.

- Legen Sie die entwickelten Si-Substrate auf eine Kochplatte, um sie bei 110 °C für 90 s zu backen.

- Tauchen Sie die Si-Substrate für 1 Minute in eine gepufferte Flusssäure (BHF-63SE), um einen Teil der SiO2-Schichten zu entfernen, die infolge der EB-Exposition und -Entwicklung der Luft ausgesetzt sind.

- Entfernen Sie den Fotolack von den Si-Substraten, indem Sie ihn 15 Minuten lang in einen organischen Fotolackentferner (z. B. Hakuri-104) tauchen.

- Tauchen Sie die Si-Substrate 4 Minuten lang in 0,5% verdünnte Flusssäure, um das dünne native Oxid in den Fensterbereichen zu entfernen, aber dieSiO2-Masken zu erhalten. Anschließend wird in eine Ultrahochvakuum-Kammer für die chemische Gasphasenabscheidung (UHV-CVD) geladen, um Ge zu züchten. Abbildung 2 zeigt das in der vorliegenden Arbeit verwendete UHV-CVD-System.

- Epitaktisches Ge-Wachstum

- Laden Sie das Si-Substrat mit SEG-Masken (hergestellt wie in Schritt 2.1) in eine Lastschleusenkammer.

- Stellen Sie die Puffer-/Hauptwachstumstemperatur auf der Registerkarte " Rezept" ein, die auf dem Betriebscomputer angezeigt wird. Bestimmen Sie die Dauer für das Hauptwachstum von Ge so, dass SEG Ge-Schichten mit benachbarten verschmelzen. Um die Dauer für das Hauptwachstum zu bestimmen, betrachten Sie die Wachstumsrate von Ge auf den {113} Ebenen, die das Wachstum in der In-Ebene/lateralen Richtung26 bestimmt. In der vorliegenden Arbeit werden die Dauern für das Hauptwachstum auf 270 min und 150 min für 650 °C bzw. 700 °C festgelegt.

- Klicken Sie im Hauptfenster auf Start , und dann wird das Si-Substrat automatisch in die Wachstumskammer übertragen.

HINWEIS: Das Protokoll über das epitaktische Ge-Wachstum (Schritte 2.2.4-2.2.7) wird automatisch verarbeitet. - Ge-Puffer auf dem beladenen Si-Substrat bei niedriger Temperatur (≈380 °C) züchten. Verwenden Sie GeH 4 verdünnt mit 9 % in Ar als Quellgas und halten Sie den Partialdruck von GeH4 für 0,5 Pa während des Pufferwachstums.

- Wachsen Sie die Ge-Hauptschicht bei erhöhter Temperatur. Halten Sie den Partialdruck von GeH4 für 0,8 Pa während des Hauptwachstums. In der vorliegenden Arbeit werden zwei unterschiedliche Temperaturen von 650 und 700 °C für die Hauptwachstumstemperatur verwendet, um SEG Ge mit einem runden Querschnitt und mit einem {113} facettenförmigen Querschnitt25 zu vergleichen.

HINWEIS: Die Wachstumsrate von Ge auf der (001)-Ebene betrug unabhängig von der Temperatur 11,7 nm/min. - Um die Entwicklung von SEG Ge und ihre Koaleszenz zu visualisieren, führen Sie ein Ge-Wachstum mit periodischer Insertion von 10 nm dicken Si 0,3 Ge0,7-Abgrenzungsschichten auf einem anderen Si-Substrat durch. Si0,3 Ge 0,7Schichten wurden unter Verwendung von Si2H6 und GeH4 Gasen gebildet. Stellen Sie während des Si 0,3 Ge 0,7-Schichtwachstums den Partialdruck von Si2H6 -Gas auf 0,02 Pa und den Partialdruck von GeH4 -Gas auf0,8Pa ein.

- Da das Si-Substrat automatisch von der Wachstumskammer in die Lastschleusenkammer übertragen wird, entlüften Sie die Lastschleusenkammer und entladen Sie das Si-Substrat manuell.

- Messungen der Ätzgrubendichte (EPD)

- 32 mg I2 in 67 ml CH3COOH werden mit einer Ultraschallreinigungsmaschine gelöst.

- Mischen Sie das I2 -gelöste CH 3 COOH, 20 ml HNO3und 10 ml HF.

- Tauchen Sie die gezüchteten Si-Substrate für 5-7 s in die CH 3 COOH / HNO3/ HF / I2 -Lösung, um geätzte Gruben zu bilden.

- Beobachten Sie die geätzten Ge-Oberflächen mit einem optischen Mikroskop (typischerweise 100x), um sicherzustellen, dass geätzte Gruben erfolgreich gebildet werden.

- Verwenden Sie ein Rasterkraftmikroskop (AFM), um die geätzten Gruben zu zählen. Legen Sie die geätzte Ge-Probe auf einen AFM-Tisch und nähern Sie sich dann der Sonde, indem Sie auf Automatischer Ansatz klicken.

- Bestimmen Sie den Beobachtungsbereich mit einem optischen Mikroskop, das in ein AFM integriert ist, und scannen Sie fünf verschiedene Bereiche von 10 μm x 10 μm. Der Amplitudendämpfungsfaktor wird automatisch bestimmt.

- TEM-Beobachtungen

- Nehmen Sie TEM-Proben aus den koaleszenten/deckenförmigen Ge-Schichten auf, indem Sie einen fokussierten Ge-Ionenstrahl (FIB-Mikroabtastmethode) verwenden27.

- Polieren Sie die TEM-Proben in einem Ionenmahlsystem mit Ar-Ionen. In der vorliegenden Arbeit werden TEM-Proben für Querschnittsbeobachtungen von 150-500 nm in [110]-Richtung und für Draufsicht-Beobachtungen von 200 nm in [001]-Richtung verdünnt.

- Schützen Sie bei TEM-Proben in der Draufsicht die Oberseite der Ge-Schichten mit amorphen Schichten und verdünnen Sie sie dann von der Unterseite (Substrat) der Ge-Schichten.

- Führen Sie TEM-Beobachtungen unter einer Beschleunigungsspannung von 200 kV durch. Durchführung von Querschnitts-Hellfeld-Scanning-TEM-Beobachtungen (STEM), um dicke TEM-Proben (500 nm) zu beobachten.

- Für ein koalesziertes Ge mit Si0,3 Ge 0,7Abgrenzungsschichten werden Querschnitts-Hochwinkel-Ringdunkelfeld-STEM-Beobachtungen (HAADF) unter einer Beschleunigungsspannung von 200 kV durchgeführt.

Ergebnisse

Theoretische Berechnung

Abbildung 3 zeigt berechnete Trajektorien von TDs in 6 Arten von verschmolzenen Ge-Schichten: Hier definieren wir das Öffnungsverhältnis (APR) als W-Fenster/(W-Fenster + W-Maske). Abbildung 3a zeigt ein rundes SEG-Ursprungskoalesziertes Ge mit einem effektiven Jahreszins = 0,8. Hier sind 2/6 TDs...

Diskussion

In der vorliegenden Arbeit wurden TDD von 4 x 107/cm2 experimentell gezeigt. Für eine weitere TDD-Reduzierung gibt es hauptsächlich 2 kritische Schritte innerhalb des Protokolls: SEG-Maskenvorbereitung und epitaktisches Ge-Wachstum.

Unser in Abbildung 4 gezeigtes Modell zeigt, dass TDD in koaleszierendem Ge unter 107/cm2 reduziert werden kann, wenn der effektive Jahreszins (W-Fenster/(W-Fenster +<...

Offenlegungen

Die Autoren haben nichts zu offenbaren.

Danksagungen

Diese Arbeit wurde von der Japan Society for the Promotion of Science (JSPS) KAKENHI (17J10044) des japanischen Ministeriums für Bildung, Kultur, Sport, Wissenschaft und Technologie (MEXT) finanziell unterstützt. Die Herstellungsprozesse wurden von der "Nanotechnology Platform" (Projekt-Nr. 12024046), MEXT, Japan, unterstützt. Die Autoren danken Herrn K. Yamashita und Frau S. Hirata von der Universität Tokio für ihre Hilfe bei TEM-Beobachtungen.

Materialien

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

Referenzen

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Nachdrucke und Genehmigungen

Genehmigung beantragen, um den Text oder die Abbildungen dieses JoVE-Artikels zu verwenden

Genehmigung beantragenThis article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. Alle Rechte vorbehalten