A subscription to JoVE is required to view this content. Sign in or start your free trial.

Method Article

חישוב תיאורטי ואימות ניסיוני להפחתת נקעים בשכבות גרמניום אפיטקסיאליות עם חללים סמי-גליליים על סיליקון

In This Article

Summary

חישוב תיאורטי ואימות ניסיוני מוצעים להפחתת צפיפות פריקת השחלה (TD) בשכבות גרמניום אפיטקסיאליות עם חללים גליליים למחצה על סיליקון. מוצגים חישובים המבוססים על האינטראקציה של TDs ופני השטח באמצעות כוח תמונה, מדידות TD ותצפיות במיקרוסקופ אלקטרונים תמסורת של TDs.

Abstract

הפחתת צפיפות פריקת השחלה (TDD) בגרמניום אפיטקסיאלי (Ge) על סיליקון (Si) הייתה אחד האתגרים החשובים ביותר למימוש מעגלים פוטוניים משולבים מונוליטית. המאמר הנוכחי מתאר שיטות חישוב תיאורטיות ואימות ניסיוני של מודל חדשני להפחתת TDD. שיטת החישוב התיאורטית מתארת את כיפוף נקעי השחלה (TDs) בהתבסס על אינטראקציה של TDs ומשטחי צמיחה לא מישוריים של צמיחה אפיטקסית סלקטיבית (SEG) במונחים של כוח תמונת נקע. החישוב מגלה כי נוכחות של חללים על מסכות SiO2 לעזור להפחית TDD. אימות ניסיוני מתואר על ידי גרמניום (Ge) SEG, באמצעות שיטת שיקוע אדים כימיים בוואקום גבוה במיוחד ותצפיות TD של Ge הגדל באמצעות תחריט ומיקרוסקופ אלקטרונים תמסורת חתך (TEM). מומלץ מאוד כי הפחתת TDD תהיה בשל נוכחותם של חללים גליליים למחצה מעל מסכות SiO2 SEG וטמפרטורת הצמיחה. לצורך אימות ניסיוני, שכבות Ge אפיטקסיאליות עם חללים גליליים למחצה נוצרות כתוצאה של SEG של שכבות Ge והתלכדותן . ה-TDDs שהתקבלו בניסוי משחזרים את ה-TDDs המחושבים בהתבסס על המודל התיאורטי. תצפיות TEM בחתך רוחב מגלות כי הן הסיום והן היצירה של TDs מתרחשים בחללים גליליים למחצה. תצפיות TEM במבט תוכניתי חושפות התנהגות ייחודית של TDs ב-Ge עם חללים סמי-גליליים (כלומר, TDs מכופפים להיות מקבילים למסכות SEG ולמצע Si).

Introduction

Epitaxial Ge on Si משכה תחומי עניין משמעותיים כפלטפורמת התקנים פוטוניים פעילה מכיוון ש- Ge יכולה לזהות/לפלוט אור בתחום התקשורת האופטית (1.3-1.6 מיקרומטר) והיא תואמת לטכניקות עיבוד Si CMOS (מוליכים למחצה משלימים של תחמוצת מתכת). עם זאת, מכיוון שאי ההתאמה בסריג בין Ge ו- Si היא גדולה כמו 4.2%, נקעי השחלה (TDs) נוצרים בשכבות Ge epitaxial על Si בצפיפות של ~ 109/cm2. הביצועים של התקנים פוטוניים Ge מתדרדרים על ידי TDs מכיוון ש- TDs פועלים כמרכזי ייצור נשאים בפוטו-גלאים Ge (PDs) ומודולטורים (MODs), וכמרכזי רקומבינציה נשאים בדיודות לייזר (LD). בתורו, הם יגדילו את זרם הדליפה ההפוכה (דליפת J) ב- PDs ו- MODs 1,2,3, ואת זרם הסף (Jth) ב- LDs 4,5,6.

דווח על ניסיונות שונים להפחית את צפיפות TD (TDD) ב-Ge on Si (איור משלים 1). חישול תרמי מגרה תנועה של TDs המוביל להפחתת TDD, בדרך כלל ל 2 x 107/cm2. החיסרון הוא הערבוב האפשרי של Si ו-Ge ודיפוזיה החוצה של דופנטים ב-Ge כמו זרחן 7,8,9 (איור משלים 1a). שכבת החיץ המדורגת SiGe 10,11,12 מגדילה את העוביים הקריטיים ומדכאת את יצירת ה- TD מה שמוביל להפחתת TDD, בדרך כלל ל 2 x 10 6/cm2. החיסרון כאן הוא שהמאגר העבה מפחית את יעילות צימוד האור בין מכשירי Ge ומדריכי גל Si שמתחתיהם (איור משלים 1b). לכידת יחס גובה-רוחב (ART)13,14,15 היא שיטת גידול אפיטקסיאלי סלקטיבי (SEG) ומפחיתה TDs על ידי לכידת TDs בדפנות של תעלות SiO 2 עבות, בדרך כלל ל <1 x 10 6/cm 2. שיטת ART משתמשת במסכת SiO 2 עבה כדי להפחית TDD ב-Ge על פני מסכות SiO2, אשר ממוקמות הרבה מעל Si ויש להן את אותו החיסרון (איור משלים 1b,1c). צמיחת Ge על זרעי עמוד Si וחישול 16,17,18 דומים לשיטת ART, ומאפשרים לכידת TD על ידי יחס גובה-רוחב גבוה צמיחת Ge, ל- <1 x 10 5/cm2. אולם לחישול בטמפרטורה גבוהה עבור התלכדות Ge יש את אותם חסרונות באיור המשלים 1a-c (איור משלים 1d).

כדי להשיג צמיחה אפיטקסיאלית נמוכה של TDD Ge על Si שאינה משוחררת מהחסרונות של השיטות הנ"ל, הצענו הפחתת TDD הנגרמת על ידי התלכדות 19,20 בהתבסס על שתי התצפיות העיקריות הבאות שדווחו עד כה בצמיחת SEG Ge 7,15,21,22,23 1) TDs מכופפים להיות נורמליים למשטחי הגידול (נצפו במיקרוסקופ אלקטרונים בחתך רוחב (TEM)), ו-2) התלכדות של שכבות SEG Ge גורמת להיווצרות חללים סמי-גליליים מעל מסכות SiO2.

הנחנו שה-TDs מכופפים בגלל כוח התמונה ממשטח הצמיחה. במקרה של Ge on Si, כוח התמונה מייצר לחצים של 1.38 GPa ו-1.86 GPa עבור נקעי בורג ונקעי קצה במרחקים של 1 ננומטר מהמשטחים החופשיים, בהתאמה19. לחצי הגזירה המחושבים גדולים משמעותית מלחץ פיירלס של 0.5 GPa שדווח עבור נקעים של 60° ב-Ge24. החישוב חוזה הפחתת TDD בשכבות Ge SEG על בסיס כמותי ותואם היטב את צמיחת SEG Ge19. תצפיות TEM של TDs מתבצעות כדי להבין התנהגויות TD בצמיחת SEG Ge המוצגת ב- Si20. הפחתת TDD הנגרמת על ידי כוח תמונה חופשית מכל חישול תרמי או שכבות חיץ עבות, ולכן מתאימה יותר ליישום התקנים פוטוניים.

במאמר זה, אנו מתארים שיטות ספציפיות לחישוב תיאורטי ואימות ניסיוני המשמשים בשיטת הפחתת TDD המוצעת.

Protocol

1. הליך חישוב תיאורטי

- חישוב מסלולים של TDs. בחישוב, נניח שמסכות SEG דקות מספיק כדי להתעלם מאפקט ART על הפחתת TDD.

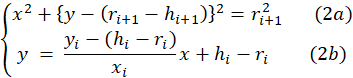

- לקבוע משטחי צמיחה ולבטא אותם על ידי משוואה/ות. לדוגמה, בטאו את התפתחות הזמן של חתך בצורת חתך עגול של שכבת SEG Ge עם פרמטר התפתחות הזמן n = i, גבהים של SEG Ge (h i) ורדיסי SEG Ge (ri), כפי שמוצג בסרטון המשלים 1a ו-Eq. (1):

- קבע כיוונים נורמליים עבור מיקום שרירותי על משטחי הצמיחה. עבור חתך הרוחב העגול SEG Ge, תאר את הקו הנורמלי ב- (x i , yi) כ

- , המוצג בסרטון המשלים 1b כקו אדום. לאחר מכן, קבל את קצה ה- TD (x i+1 , y i+1) מהנקודה (x i , y i) על ידי פתרון המשוואות הבאות בו זמנית:

- , המוצג בסרטון המשלים 1b כקו אדום. לאחר מכן, קבל את קצה ה- TD (x i+1 , y i+1) מהנקודה (x i , y i) על ידי פתרון המשוואות הבאות בו זמנית:

- חשב מסלול של TD אחד בהתאם למיקום של יצירת TD (x 0, 0), כפי שמוצג בסרטון משלים 1c. במילים אחרות, ניתן לחשב מסלול עבור TD שרירותי לפי השיטה שתוארה לעיל.

- חישוב TDD בהנחה ש-TDs חודרים למשטח התחתון ותורמים להפחתת TDD (כלומר, TDs מתחת לנקודה שבה שכבות SEG Ge מתלכדות נלכדות על ידי חללים חצי גליליים ולעולם לא מופיעות על פני השטח העליונים).

- לקבוע משטחי צמיחה ולבטא אותם על ידי משוואה/ות. לדוגמה, בטאו את התפתחות הזמן של חתך בצורת חתך עגול של שכבת SEG Ge עם פרמטר התפתחות הזמן n = i, גבהים של SEG Ge (h i) ורדיסי SEG Ge (ri), כפי שמוצג בסרטון המשלים 1a ו-Eq. (1):

2. הליך אימות ניסיוני

- הכנת מסכת SEG

- לפני ייצור מסכות SEG, הגדירו אזורי גידול Ge על ידי הכנת קובץ עיצוב. בעבודה הנוכחית, הכינו תבניות קו ורווח המיושרות לכיוון [110] ואזורי חלון Si בצורת ריבוע ברוחב 4 מ"מ באמצעות תוכנה מסחרית (למשל, AutoCAD).

- קבע את העיצוב של מסכות SEG (בפרטחלון Wומסיכת W) באמצעות התוכנה. חלון W הוא רוחב החלון (רוחב זרע Si)ומסיכת W היא רוחב מסיכת SiO2 , כך ששכבות SEG Ge יכולות להתמזג עם הסמוכות להן. קבעחלון Wומסיכת W על-ידי ציור מלבנים בלחיצה על Open File → מבנה → מלבן או polyline.

הערה: רוחב המלבנים הופךלחלון W, והמרווח בין המלבנים הופךלמסיכת W. בעבודה הנוכחית, ערכי המינימום שלחלון Wומסיכת W הם 0.5 מיקרומטר ו- 0.3 מיקרומטר, בהתאמה, המוגבלים על ידי הרזולוציה במערכת הליתוגרפיה EB המועסקת. - כסימוכין, ציירו אזורי חלון Si בצורת ריבוע ברוחב 4 מ"מ D, הנחשבים לאזורי השמיכה. לחץ על קובץ פתוח → מבנה → מלבן או פוליליין כדי לצייר את חלון Si בצורת ריבוע. השתמשו בסכמות המוצגות באיור 1 כדי להכין את תבניות הקו והרווח ואת שטח השמיכה המרובעת בגודל 4 מ"מ.

- הכינו מצעים מסוממים מסוג B-Si (001) עם התנגדות של 1-100 Ω∙cm. בעבודה הנוכחית, השתמש במצעי Si בגודל 4 אינץ '. נקו את משטחי המצע בתמיסת פיראנה (תערובת של 20 מ"ל של 30% H 2 O 2ו-80 מ"ל של 96% H2 SO4) לפי הצורך.

- פתחו את המכסה של תנור צינור והעמיסו את מצעי הסי לתוך הכבשן באמצעות מוט זכוכית. בעבודה הנוכחית, לחמצן 10 Si מצעים בו זמנית.

- התחל לנשוף גז N2 יבש לתוך הכבשן על ידי פתיחת שסתום הגז. לאחר מכן, הגדר את קצב זרימת הגז ל -0.5 ליטר / מטר על ידי שליטה בשסתום.

- הגדר את טמפרטורת החישול על-ידי שינוי התוכנית. בעבודה הנוכחית, השתמש ב"שלב תבנית (מצב 2)" והגדר את טמפרטורת התהליך ל -900 מעלות צלזיוס. לאחר מכן, הפעל את התוכנית על ידי דחיפת פונקציה → לרוץ.

- כאשר הטמפרטורה מגיעה ל -900 מעלות צלזיוס, סגור את שסתום N 2 היבש, פתח את שסתום O 2 היבש (זרימת O2 = 1 ליטר / מטר), ושמור למשך שעתיים.

הערה: בצע את שלבים 2.1.9-2.1.16 בחדר צהוב. - מצפים את מצעי Si המחומצנים בסורפקטנט (OAP) באמצעות ציפוי מסתובב ולאחר מכן אופים ב-110°C במשך 90 שניות על פלטה חשמלית.

- לאחר ציפוי פעילי השטח, מצפים את מצעי Si בפוטו-התנגדות (למשל, ZEP520A) באמצעות ציפוי מסתובב ולאחר מכן אופים בחום של 180°C במשך 5 דקות על פלטה חשמלית.

- לטעון את מצעי Si עם פעילי שטח photoresist לתוך סופר קרן אלקטרונים (EB).

- קרא את קובץ העיצוב (שהוכן בשלב 2.1.2) בכותב EB וצור קובץ פעולה (קובץ WEC). הגדר את כמות המינון כ- 120 μC/cm2 בקובץ WEC. עם סיום טעינת המצע, בצע חשיפת EB על-ידי לחיצה על לחצן החשיפה היחידה .

- פרוק את המצע מכותב EB על ידי לחיצה על רקיק נשיאה → פריקה עם סיום החשיפה.

- הכן מפתח photoresist (ZED) ושטיפה עבור המפתח (ZMD) בתא טיוטה. טבלו את מצעי Si החשופים לתוך המפתח במשך 60 שניות בטמפרטורת החדר.

- הסר את מצעי Si מהיזם, ולאחר מכן יבש את המצע עם גז N2 .

- הניחו את מצעי Si המפותחים על פלטה חמה לאפייה בטמפרטורה של 110°C למשך 90 שניות.

- טבלו את מצעי Si בחומצה הידרופלואורית חוצצת (BHF-63SE) למשך דקה אחת על מנת להסיר חלק משכבות SiO2 שנחשפו לאוויר כתוצאה מחשיפה והתפתחות EB.

- הסר את photoresist מן המצע Si על ידי טבילה לתוך מסיר photoresist אורגני (למשל, Hakuri-104) במשך 15 דקות.

- טבלו את מצעי Si בחומצה הידרופלואורית מדוללת 0.5% למשך 4 דקות כדי להסיר את התחמוצת הטבעית הדקה באזורי החלונות, אך כדי לשמור על מסכות SiO2 . לאחר מכן העמיסו על תא שיקוע אדים כימי בוואקום גבוה במיוחד (UHV-CVD) כדי לגדל Ge. איור 2 מראה את מערכת UHV-CVD ששימשה בעבודה הנוכחית.

- צמיחת Ge אפיטקסיאלית

- טען את מצע Si עם מסכות SEG (מיוצרות כמו בשלב 2.1) לתוך תא נעילת עומס.

- הגדר את המאגר/טמפרטורת הגידול הראשית בכרטיסיה מתכון המוצגת במחשב הפעולה. קבע את משכי הזמן לצמיחה העיקרית של Ge כך ששכבות SEG Ge יתמזגו עם שכבות סמוכות. כדי להחליט על משכי הזמן לצמיחה העיקרית, שקול את קצב הצמיחה של Ge במישורי {113}, הקובע את הצמיחה בכיוון המישורי/רוחבי26. בעבודה הנוכחית, הגדר את משכי הזמן לצמיחה העיקרית כ- 270 דקות ו- 150 דקות עבור 650 ° C ו- 700 ° C, בהתאמה.

- לחץ על התחל בחלון הראשי, ולאחר מכן מצע Si מועבר באופן אוטומטי לתוך תא הגידול.

הערה: פרוטוקול על צמיחת Ge אפיטקסיאלית (שלבים 2.2.4-2.2.7) מעובד באופן אוטומטי. - גדל חיץ Ge על מצע Si טעון בטמפרטורה נמוכה (≈380 ° C). השתמש ב- GeH 4 מדולל ב- 9% ב- Ar כגז המקור ושמור על הלחץ החלקי של GeH4 עבור 0.5 Pa במהלך צמיחת החיץ.

- לגדל את השכבה הראשית Ge בטמפרטורה גבוהה. שמור על הלחץ החלקי של GeH4 עבור 0.8 Pa במהלך הצמיחה העיקרית. בעבודה הנוכחית, השתמש בשתי טמפרטורות שונות של 650 ו 700 ° C עבור טמפרטורת הצמיחה העיקרית על מנת להשוות SEG Ge עם חתך בצורת עגול ועם חתך {113} פאות25.

הערה: קצב הצמיחה של Ge במישור (001) היה 11.7 ננומטר לדקה ללא תלות בטמפרטורה. - על מנת להמחיש את האבולוציה של SEG Ge ואת ההתלכדות שלהם, בצע צמיחת Ge עם החדרה תקופתית של שכבות תיחום Si0.3Ge0.7 בעובי 10 ננומטר על מצע Si אחר. שכבות Si0.3Ge0.7 נוצרו באמצעות גזים Si2H6 ו- GeH4. במהלך הגידול של Si0.3Ge 0.7 שכבות, הגדר את הלחץ החלקי של גז Si2H6 על 0.02 Pa ואת הלחץ החלקי של גז GeH4 על0.8 Pa.

- כאשר מצע Si מועבר באופן אוטומטי מתא הגידול לתא נעילת העומס, אווררו את תא נעילת העומס ופרקו את מצע Si באופן ידני.

- מדידות צפיפות בור תחריט (EPD)

- להמיס 32 מ"ג של I2 ב 67 מ"ל של CH3COOH באמצעות מכונת ניקוי קולי.

- ערבבואת I 2-dismsed CH 3COOH, 20 מ"ל של HNO3 ו-10 מ"ל של HF.

- טבלו את מצעי Si שגדלו ב-Ge בתמיסתCH 3 COOH/HNO3/HF/I2 למשך 5-7 שניות על מנת ליצור בורות חרוטים.

- התבונן במשטחי Ge החרוטים במיקרוסקופ אופטי (בדרך כלל 100x) כדי להבטיח שהבורות החרוטים נוצרו בהצלחה.

- השתמש במיקרוסקופ כוח אטומי (AFM) כדי לספור את הבורות החרוטים. הניחו את דגימת Ge החרוטה על במת AFM ולאחר מכן התקרבו לגשושית על ידי לחיצה על גישה אוטומטית.

- החליטו על אזור התצפית באמצעות מיקרוסקופ אופטי משולב עם AFM, וסרוקו חמישה אזורים שונים בגודל 10 מיקרומטר x 10 מיקרומטר. גורם דעיכת המשרעת נקבע באופן אוטומטי.

- תצפיות TEM

- איסוף דגימות TEM משכבות Ge המגובשות/שמיכות באמצעות קרן יון Ge ממוקדת (שיטת דגימת מיקרו FIB)27.

- לטש את דגימות TEM במערכת כרסום יונים באמצעות יוני Ar. בעבודה הנוכחית, יש לדלל את דגימות ה-TEM כך שתצפיות חתך יהיו 150-500 ננומטר בכיוון [110], ותצפיות תוכנית-מבט יהיו 200 ננומטר בכיוון [001].

- לדגימות TEM בתצוגת תוכנית, הגן על המשטחים העליונים של שכבות Ge באמצעות שכבות אמורפיות, ולאחר מכן דק כלפי מטה מהצד התחתון (המצע) של שכבות Ge.

- בצע תצפיות TEM תחת מתח תאוצה של 200 kV. בצע תצפיות TEM (STEM) של סריקת שדה בהיר בחתך רוחב על מנת לצפות בדגימות TEM עבות (500 ננומטר).

- עבור Ge מאוחד עם שכבות תיחום Si0.3Ge0.7 , בצע תצפיות STEM בשדה כהה טבעתי בעל זווית גבוהה (HAADF) תחת מתח תאוצה של 200 kV.

תוצאות

חישוב תיאורטי

איור 3 מראה מסלולים מחושבים של TD ב-6 סוגים של שכבות Ge מאוחדות: כאן אנו מגדירים את יחס הצמצם (APR)כחלון W/(חלון W +מסיכת W). איור 3a מראה מקור SEG בצורת עגול שהתלכד Ge של APR = 0.8. כ?...

Discussion

בעבודה הנוכחית, TDD של 4 x 107/cm2 הוצגו באופן ניסיוני. להפחתת TDD נוספת, ישנם בעיקר 2 שלבים קריטיים בפרוטוקול: הכנת מסכת SEG וצמיחת Ge אפיטקסיאלית.

המודל שלנו המוצג באיור 4 מצביע על כך שניתן להפחית TDD מתחת ל-107/cm2 ב-Ge מאוחד כאשר APR,חלון W/(חלו...

Disclosures

למחברים אין מה לחשוף.

Acknowledgements

עבודה זו נתמכה כספית על ידי האגודה היפנית לקידום המדע (JSPS) KAKENHI (17J10044) ממשרד החינוך, התרבות, הספורט, המדע והטכנולוגיה (MEXT), יפן. תהליכי הייצור נתמכו על ידי "פלטפורמת ננוטכנולוגיה" (פרויקט מס '12024046), MEXT, יפן. המחברים רוצים להודות למר ק. ימאשיטה ולגב' ס. היראטה, מאוניברסיטת טוקיו, על עזרתם בתצפיות TEM.

Materials

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

References

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Reprints and Permissions

Request permission to reuse the text or figures of this JoVE article

Request PermissionThis article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. All rights reserved