É necessária uma assinatura da JoVE para visualizar este conteúdo. Faça login ou comece sua avaliação gratuita.

Method Article

Cálculo Teórico e Verificação Experimental para Redução de Deslocamento em Camadas Epitaxiais de Germânio com Vazios Semicilíndricos em Silício

Neste Artigo

Resumo

Cálculo teórico e verificação experimental são propostos para uma redução da densidade de deslocamento de rosca (DT) em camadas epitaxiais de germânio com vazios semicilíndricos sobre silício. Cálculos baseados na interação de TDs e superfície via força de imagem, medições de TD e observações de microscópio eletrônico de transmissão de TDs são apresentados.

Resumo

A redução da densidade de deslocamento por rosqueamento (TDD) em germânio epitaxial (Ge) sobre silício (Si) tem sido um dos desafios mais importantes para a realização de circuitos fotônicos monoliticamente integrados. O presente trabalho descreve métodos de cálculo teórico e verificação experimental de um novo modelo para a redução de TDD. O método de cálculo teórico descreve a flexão de deslocamentos de rosqueamento (TDs) com base na interação de TDs e superfícies de crescimento não planares de crescimento epitaxial seletivo (SEG) em termos de força de imagem de deslocamento. O cálculo revela que a presença de vazios nas máscaras SiO2 ajuda a reduzir o TDD. A verificação experimental é descrita por germânio (Ge) SEG, usando um método de deposição de vapor químico de ultra-alto vácuo e observações de TD do Ge cultivado via gravura e microscópio eletrônico de transmissão transversal (MET). Sugere-se fortemente que a redução do TDD seria devida à presença de vazios semicilíndricos sobre as máscaras SiO2 SEG e à temperatura de crescimento. Para verificação experimental, camadas epitaxiais de Ge com vazios semicilíndricos são formadas como resultado das camadas de SEG de Ge e sua coalescência. Os TDDs obtidos experimentalmente reproduzem os TDDs calculados com base no modelo teórico. Observações transversais de ETM revelam que tanto a terminação quanto a geração de DTs ocorrem em vazios semicilíndricos. As observações de MET de visão plana revelam um comportamento único de TDs em Ge com vazios semicilíndricos (ou seja, TDs são dobrados para serem paralelos às máscaras SEG e ao substrato Si).

Introdução

O Epitaxial Ge on Si atraiu interesses substanciais como uma plataforma de dispositivo fotônico ativo, uma vez que o Ge pode detectar / emitir luz na faixa de comunicação óptica (1,3-1,6 μm) e é compatível com técnicas de processamento Si CMOS (semicondutor complementar de óxido metálico). No entanto, uma vez que a incompatibilidade de rede entre Ge e Si é tão grande quanto 4,2%, os deslocamentos de rosqueamento (TDs) são formados em camadas epitaxiais de Ge em Si a uma densidade de ~109/cm2. Os desempenhos dos dispositivos fotônicos Ge são deteriorados pelos TDs porque os TDs funcionam como centros de geração de portadores em fotodetectores Ge (PDs) e moduladores (MODs) e como centros de recombinação de portadores em diodos laser (LDs). Por sua vez, aumentariam a corrente de fuga reversa (vazamento J) em PDs e MODs 1,2,3 e a corrente limiar (Jth) em LDs 4,5,6.

Várias tentativas foram relatadas para reduzir a densidade de DT (TDD) em Ge em Si (Figura Suplementar 1). O recozimento térmico estimula o movimento dos TDs levando à redução do TDD, tipicamente para 2 x 107/cm2. A desvantagem é a possível mistura de Si e Ge e a superdifusão de dopantes em Ge, como o fósforo 7,8,9 (Figura suplementar 1a). A camada tampão graduada SiGe 10,11,12 aumenta as espessuras críticas e suprime a geração de TDs levando à redução de TDD, tipicamente para 2 x 10 6/cm2. A desvantagem aqui é que o buffer espesso reduz a eficiência de acoplamento de luz entre dispositivos Ge e guias de onda Si por baixo (Figura suplementar 1b). O aprisionamento da relação de aspecto (TARV)13,14,15 é um método de crescimento epitaxial seletivo (SEG) e reduz os TDs por meio do aprisionamento de TDs nas paredes laterais de trincheiras espessas de SiO 2, tipicamente para <1 x 10 6/cm2. O método ART usa uma máscara de SiO 2 espessa para reduzir o TDD em Ge sobre as máscaras de SiO2, que se localiza muito acima de Si e tem a mesma desvantagem (Figura suplementar 1b,1c). O crescimento de Ge em sementes de pilar Si e o recozimento 16,17,18 são semelhantes ao método TARV, possibilitando o aprisionamento de DT pela alta proporção de crescimento de GE, para <1 x 10 5/cm2. No entanto, o recozimento de alta temperatura para coalescência de Ge tem as mesmas desvantagens na Figura Suplementar 1a-c (Figura Suplementar 1d).

Para alcançar um crescimento epitaxial de Ge de baixo TDD em Si, livre das desvantagens dos métodos acima mencionados, propusemos a redução de TDD induzida por coalescência19,20 com base nas duas principais observações a seguir relatadas até agora no crescimento de GEESEG 7,15,21,22,23 : 1) Os TDs são dobrados para serem normais às superfícies de crescimento (observado pelo microscópio eletrônico de transmissão transversal (MET)), e 2) a coalescência das camadas de SEG Ge resulta na formação de vazios semicilíndricos sobre as máscaras de SiO2.

Assumimos que os TDs são dobrados devido à força da imagem da superfície de crescimento. No caso de Ge em Si, a força de imagem gera tensões de cisalhamento de 1,38 GPa e 1,86 GPa para luxações de parafusos e deslocamentos de borda a distâncias de 1 nm das superfícies livres, respectivamente19. As tensões de cisalhamento calculadas são significativamente maiores do que a tensão de Peierls de 0,5 GPa relatada para luxações de 60° em Ge24. O cálculo prevê a redução do TDD nas camadas de Ge SEG em uma base quantitativa e está em boa concordância com o crescimento do SEG Ge19. Observações de MET de TDs são realizadas para entender os comportamentos de DT no crescimento apresentado do SEG Ge no Si20. A redução TDD induzida pela força de imagem é livre de qualquer recozimento térmico ou camadas de buffer espessas e, portanto, é mais adequada para a aplicação de dispositivos fotônicos.

Neste artigo, descrevemos métodos específicos para o cálculo teórico e verificação experimental empregados no método de redução de TDD proposto.

Protocolo

1. Procedimento de cálculo teórico

- Calcular trajetórias de TDs. No cálculo, suponha que as máscaras SEG sejam finas o suficiente para ignorar o efeito ART na redução de TDD.

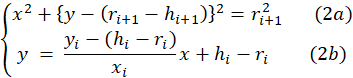

- Determine as superfícies de crescimento e expresse-as por equação(ões). Por exemplo, expresse a evolução temporal de uma seção transversal de forma redonda de uma camada SEG Ge com o parâmetro de evolução temporal n = i, alturas SEG Ge (h i) e raios SEG Ge (ri), conforme mostrado no Vídeo Suplementar 1a e Eq. (1):

- Determine as direções normais para um local arbitrário nas superfícies de crescimento. Para a seção transversal de forma redonda SEG Ge, descreva a linha normal em (x i , yi) como , mostrado no Vídeo Suplementar 1b como

uma linha vermelha. Em seguida, obtenha a borda do TD (x i+1 , y i + 1) a partir do ponto (x i , yi) resolvendo as seguintes equações simultâneas:

uma linha vermelha. Em seguida, obtenha a borda do TD (x i+1 , y i + 1) a partir do ponto (x i , yi) resolvendo as seguintes equações simultâneas:

- Calcule uma trajetória de um TD dependendo do local de geração do TD (x 0, 0), conforme mostrado no Vídeo Suplementar 1c. Em outras palavras, uma trajetória para uma DT arbitrária pode ser calculada pelo método descrito acima.

- Calcule o TDD assumindo que os TDs penetram na superfície inferior e contribuem para a redução do TDD (ou seja, os TDs abaixo do ponto em que as camadas de SEG Ge se aglutinam são aprisionadas por vazios semicilíndricos e nunca aparecem na superfície superior).

- Determine as superfícies de crescimento e expresse-as por equação(ões). Por exemplo, expresse a evolução temporal de uma seção transversal de forma redonda de uma camada SEG Ge com o parâmetro de evolução temporal n = i, alturas SEG Ge (h i) e raios SEG Ge (ri), conforme mostrado no Vídeo Suplementar 1a e Eq. (1):

2. Procedimento de verificação experimental

- Preparação da máscara SEG

- Antes da fabricação de máscaras SANG, defina as áreas de crescimento Ge preparando um arquivo de design. No presente trabalho, prepare padrões de linha e espaço alinhados à direção [110] e às áreas de janela Si em forma de quadrado de 4 mm de largura usando software comercial (por exemplo, AutoCAD).

- Determine o design das máscaras SEG (em particular ajanela W e amáscara W) usando o software. A janela W é a largura dajanela (largura da semente Si) e a máscara W é a largura damáscara SiO2 , de modo que as camadas SEG Ge podem se aglutinar com as adjacentes. Determine ajanela W e amáscara W desenhando retângulos clicando em abrir arquivo → estrutura → retângulo ou polilinha.

NOTA: A largura dos retângulos torna-sejanela W e o intervalo dos retângulos torna-semáscara W. No presente trabalho, os valores mínimos dejanela W emáscara W são 0,5 μm e 0,3 μm, respectivamente, que são restritos pela resolução no sistema de litografia EB empregado. - Como referências, desenhe áreas de janela Si em forma de quadrado de 4 mm de largura D, consideradas como as áreas de cobertura. Clique em abrir arquivo → estrutura → retângulo ou polilinha para desenhar a janela Si em forma de quadrado. Use os esquemas mostrados na Figura 1 para preparar os padrões de linha e espaço e a área do cobertor quadrado de 4 mm.

- Preparar substratos p-Si dopados com B (001) com a resistividade de 1-100 Ω∙cm. No presente trabalho, utilizar substratos Si de 4 polegadas. Limpe as superfícies do substrato com solução de piranha (uma mistura de 20 mL de 30% de H 2 O 2 e 80 mL de 96% de H2SO4) conforme necessário.

- Abra a tampa de um forno de tubo e carregue os substratos Si no forno usando uma haste de vidro. No presente trabalho, oxidar 10 substratos de Si de uma só vez.

- Comece a soprar gás N2 seco no forno abrindo a válvula de gás. Em seguida, defina a taxa de fluxo de gás para 0,5 L / m, controlando a válvula.

- Defina a temperatura de recozimento alterando o programa. No presente trabalho, use "etapa padrão (modo 2)" e defina a temperatura do processo para 900 °C. Em seguida, execute o programa pressionando a função → executar.

- Quando a temperatura atingir 900 °C, feche a válvula N 2 seca, abra a válvula O 2 seca (fluxo O 2 = 1 L/m) e mantenha por2 h.

Observação : execute as etapas 2.1.9-2.1.16 em uma sala amarela. - Revestir os substratos de Si oxidado com um surfactante (OAP) usando um revestidor de spin e, em seguida, assar a 110 °C por 90 s em uma placa de aquecimento.

- Após o revestimento do surfactante, revestir os substratos de Si com um fotorresistente (por exemplo, ZEP520A) usando um revestidor de spin e, em seguida, assar a 180 °C por 5 min em uma placa de aquecimento.

- Carregue os substratos Si com o surfactante e fotorresista em um gravador de feixe de elétrons (EB).

- Leia o arquivo de design (preparado na etapa 2.1.2) no gravador EB e crie um arquivo de operação (arquivo WEC). Defina a quantidade da dose como 120 μC/cm2 no arquivo WEC. À medida que o carregamento do substrato terminar, execute a exposição EB clicando no botão de exposição única .

- Descarregue o substrato do gravador EB clicando em wafer carry → descarregar à medida que a exposição termina.

- Prepare um revelador fotorresistente (ZED) e um enxágue para o revelador (ZMD) em uma câmara de rascunho. Mergulhe os substratos Si expostos no revelador por 60 s à temperatura ambiente.

- Remova os substratos Si do revelador e, em seguida, seque o substrato com gás N2 .

- Coloque os substratos Si desenvolvidos em uma placa de aquecimento para assar a 110 °C por 90 s.

- Mergulhe os substratos de Si em um ácido fluorídrico tamponada (BHF-63SE) por 1 minuto para remover parte das camadas de SiO2 expostas ao ar como resultado da exposição e desenvolvimento de EB.

- Remova o fotorresistente dos substratos Si mergulhando em um removedor fotorresistente orgânico (por exemplo, Hakuri-104) por 15 min.

- Mergulhe os substratos de Si em ácido fluorídrico diluído a 0,5% por 4 min para remover o óxido nativo fino nas regiões da janela, mas para reter as máscaras de SiO2 . Em seguida, carregue em uma câmara de deposição de vapor químico de ultra-alto vácuo (UHV-CVD) para crescer Ge. A Figura 2 mostra o sistema UHV-CVD utilizado no presente trabalho.

- Crescimento de Ge epitaxial

- Carregue o substrato Si com máscaras SEG (fabricadas como na etapa 2.1) em uma câmara de bloqueio de carga.

- Defina a temperatura de crescimento do buffer/principal na guia Receita mostrada no computador de operação. Determine as durações para o crescimento principal de Ge de modo que as camadas de SEG Ge coalescem com as adjacentes. Para decidir as durações do crescimento principal, considere a taxa de crescimento de Ge nos planos {113}, que determina o crescimento na direção plano/lateral26. No presente trabalho, definir as durações para o crescimento principal como 270 min e 150 min para 650 °C e 700 °C, respectivamente.

- Clique em Iniciar na janela principal e, em seguida, o substrato Si é automaticamente transferido para a câmara de crescimento.

NOTA: O protocolo sobre o crescimento epitaxial de Ge (etapas 2.2.4-2.2.7) é processado automaticamente. - Cultivar tampão Ge no substrato Si carregado a baixa temperatura (≈380 °C). Use GeH 4 diluído a 9% em Ar como gás fonte e mantenha a pressão parcial de GeH4 por 0,5 Pa durante o crescimento do tampão.

- Crescer a camada principal de Ge a uma temperatura elevada. Mantenha a pressão parcial de GeH4 por 0,8 Pa durante o crescimento principal. No presente trabalho, utilizar duas temperaturas diferentes de 650 e 700 °C para a temperatura de crescimento principal, a fim de comparar o SEG Ge com uma seção transversal de forma redonda e com uma seção transversal de faceta {113}25.

NOTA: A taxa de crescimento de Ge no plano (001) foi de 11,7 nm/min independente da temperatura. - Para visualizar a evolução do SEG Ge e sua coalescência, realizar o crescimento do Ge com inserção periódica de camadas de demarcação de Si0,3Ge0,7 de 10 nm de espessura em outro substrato de Si. As camadas de Si 0,3 Ge0,7foram formadas utilizando os gases Si2H6 e GeH4. Durante o crescimento da camada Si0,3Ge 0,7, defina a pressão parcial do gás Si2H6 em 0,02 Pa e a pressão parcial do gás GeH4 em0,8 Pa.

- À medida que o substrato Si é transferido automaticamente da câmara de crescimento para a câmara de bloqueio de carga, ventile a câmara de bloqueio de carga e descarregue o substrato Si manualmente.

- Medições da densidade do poço de gravação (EPD)

- Dissolva 32 mg de I2 em 67 mL de CH3COOH usando uma máquina de limpeza ultra-sônica.

- Misture o COOH I 2-dissolvido CH 3, 20 mL de HNO 3e 10 mL de HF.

- Mergulhe os substratos de Si cultivados em Ge, na solução CH3 COOH/HNO3/HF/I2 por 5-7 s, a fim de formar poços gravados.

- Observe as superfícies Ge gravadas com um microscópio óptico (tipicamente 100x) para garantir que os poços gravados sejam formados com sucesso.

- Empregue um microscópio de força atômica (AFM) para contar os poços gravados. Coloque a amostra Ge gravada em um estágio AFM e, em seguida, aproxime-se da sonda clicando em abordagem automática.

- Decida a área de observação usando um microscópio óptico integrado com um AFM e digitalize cinco áreas diferentes de 10 μm x 10 μm. O fator de amortecimento da amplitude é determinado automaticamente.

- Observações do TEM

- Pegar os corpos de prova de MET das camadas de Ge coalescidas/mantas utilizando um feixe de íons Ge focalizado (método de microamostragem FIB)27.

- Polir os espécimes TEM em um sistema de moagem de íons usando íons Ar. No presente trabalho, espécimes de MET diluídos para observações transversais devem ser de 150-500 nm na direção [110] e para observações de visão plana de 200 nm na direção [001].

- Para amostras TEM de visualização plana, proteja as superfícies superiores das camadas Ge com camadas amorfas e, em seguida, dilua do lado inferior (substrato) das camadas Ge.

- Realizar observações MET sob uma tensão de aceleração de 200 kV. Realizar observações de MET de varredura de campo brilhante (STEM) de seção transversal para observar espécimes de MET espessos (500 nm).

- Para um Ge coalescido com camadas de demarcação Si0,3Ge0,7, execute observações STEM de campo escuro anular de alto ângulo (HAADF) de seção transversal sob uma tensão de aceleração de 200 kV.

Resultados

Cálculo Teórico

A Figura 3 mostra trajetórias calculadas de TDs em 6 tipos de camadas Ge coalescidas: aqui, definimos a razão de abertura (APR) comosendo janela W/(janela W +máscara W). A Figura 3a mostra uma origem SEG de forma redonda Ge coalescida de APR = 0,8. Aqui, 2/6 TDs estão presos. A ...

Discussão

No presente trabalho, foram mostrados experimentalmente TDD de 4 x 107/cm2 . Para uma maior redução do TDD, existem principalmente 2 etapas críticas dentro do protocolo: preparação da máscara SEG e crescimento epitaxial do GE.

Nosso modelo mostrado na Figura 4 indica que o TDD pode ser reduzido abaixo de 107/cm2 em Ge coalescida quando APR, janela W/(janela W + máscara W), é tão ...

Divulgações

Os autores não têm nada a revelar.

Agradecimentos

Este trabalho foi apoiado financeiramente pela Sociedade Japonesa para a Promoção da Ciência (JSPS) KAKENHI (17J10044) do Ministério da Educação, Cultura, Esportes, Ciência e Tecnologia (MEXT), Japão. Os processos de fabricação foram apoiados pela "Nanotechnology Platform" (projeto No. 12024046), MEXT, Japão. Os autores gostariam de agradecer ao Sr. K. Yamashita e à Sra. S. Hirata, da Universidade de Tóquio, por sua ajuda nas observações do ETM.

Materiais

| Name | Company | Catalog Number | Comments |

| AFM | SII NanoTechnology | SPI-3800N | |

| BHF | DAIKIN | BHF-63U | |

| CAD design | AUTODESK | AutoCAD 2013 | Software |

| CH3COOH | Kanto-Kagaku | Acetic Acid | for Electronics |

| CVD | Canon ANELVA | I-2100 SRE | |

| Developer | ZEON | ZED | |

| Developer rinse | ZEON | ZMD | |

| EB writer | ADVANTEST | F5112+VD01 | |

| Furnace | Koyo Thermo System | KTF-050N-PA | |

| HF, 0.5 % | Kanto-Kagaku | 0.5 % HF | |

| HF, 50 % | Kanto-Kagaku | 50 % HF | |

| HNO3, 61 % | Kanto-Kagaku | HNO3 1.38 | for Electronics |

| I2 | Kanto-Kagaku | Iodine 100g | |

| Photoresist | ZEON | ZEP520A | |

| Photoresist remover | Tokyo Ohka | Hakuri-104 | |

| Surfactant | Tokyo Ohka | OAP | |

| TEM | JEOL | JEM-2010HC |

Referências

- Giovane, L. M., Luan, H. C., Agarwal, A. M., Kimerling, L. C. Correlation between leakage current density and threading dislocation density in SiGe p-i-n diodes grown on relaxed graded buffer layers. Applied Physics Letters. 78 (4), 541-543 (2001).

- Wang, J., Lee, S. Ge-photodetectors for Si-based optoelectronic integration. Sensors. 11, 696-718 (2011).

- Ishikawa, Y., Saito, S. Ge-on-Si photonic devices for photonic-electronic integration on a Si platform. IEICE Electronics Express. 11 (24), 1-17 (2014).

- Cai, Y. . Materials science and design for germanium monolithic light source on silicon, Ph.D. dissertation. , (2009).

- Wada, K., Kimerling, L. C. . Photonics and Electronics with Germanium. , 294 (2015).

- Higashitarumizu, N., Ishikawa, Y. Enhanced direct-gap light emission from Si-capped n+-Ge epitaxial layers on Si after post-growth rapid cyclic annealing: Impact of non-radiative interface recombination toward Ge/Si double heterostructure lasers. Optics Express. 25 (18), 21286-21300 (2017).

- Luan, H. C., et al. High-quality Ge epilayers on Si with low threading-dislocation densities. Applied Physics. Letters. 75 (19), 2909-2911 (1999).

- Nayfeha, A., Chui, C. O., Saraswat, K. C. Effects of hydrogen annealing on heteroepitaxial-Ge layers on Si: Surface roughness and electrical quality. Applied Physics Letters. 85 (14), 2815-2817 (2004).

- Choi, D., Ge, Y., Harris, J. S., Cagnon, J., Stemmer, S. Low surface roughness and threading dislocation density Ge growth on Si (001). Journal of Crystal Growth. 310 (18), 4273-4279 (2008).

- Currie, M. T., Samavedam, S. B., Langdo, T. A., Leitz, C. W., Fitzgerald, E. A. Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing. Applied Physics Letters. 72 (14), 1718-1720 (1998).

- Liu, J. L., Tong, S., Luo, Y. H., Wan, J., Wang, K. L. High-quality Ge films on Si substrates using Sb surfactant-mediated graded SiGe buffers. Applied Physics Letters. 79 (21), 3431-3433 (2001).

- Yoon, T. S., Liu, J., Noori, A. M., Goorsky, M. S., Xie, Y. H. Surface roughness and dislocation distribution in compositionally graded relaxed SiGe buffer layer with inserted-strained Si layers. Applied Physics Letters. 87 (1), 012014 (2005).

- Langdo, T. A., Leitz, C. W., Currie, M. T., Fitzgerald, E. A., Lochtefeld, A., Antoniadis, D. A. High quality Ge on Si by epitaxial necking. Applied Physics Letters. 76 (25), 3700-3702 (2000).

- Park, J. S., Bai, J., Curtin, M., Adekore, B., Carroll, M., Lochtefeld, A. Defect reduction of selective Ge epitaxy in trenches on Si(001) substrates using aspect ratio trapping. Applied Physics Letters. 90 (5), 052113 (2007).

- Fiorenza, J. G., et al. Aspect ratio trapping: A unique technology for integrating Ge and III-Vs with silicon CMOS. ECS Transactions. 33 (6), 963-976 (2010).

- Salvalaglio, M., et al. Engineered Coalescence by Annealing 3D Ge Microstructures into High-Quality Suspended Layers on Si. Applied Materials & Interfaces. 7 (34), 19219-19225 (2015).

- Bergamaschini, R., et al. Self-aligned Ge and SiGe three-dimensional epitaxy on dense Si pillar arrays. Surface Science Reports. 68 (3), 390-417 (2013).

- Isa, F., et al. Highly Mismatched, Dislocation-Free SiGe/Si Heterostructures. Advanced Materials. 28 (5), 884-888 (2016).

- Yako, M., Ishikawa, Y., Wada, K. Coalescence induced dislocation reduction in selectively grown lattice-mismatched heteroepitaxy: Theoretical prediction and experimental verification. Journal of Applied Physics. 123 (18), 185304 (2018).

- Yako, M., Ishikawa, Y., Abe, E., Wada, K. Defects and Their Reduction in Ge Selective Epitaxy and Coalescence Layer on Si With Semicylindrical Voids on SiO2 Masks. IEEE Journal of Selected Topics in Quantum Electronics. 24 (6), 8201007 (2018).

- Park, J. S., Bai, J., Curtin, M., Carroll, M., Lochtefeld, A. Facet formation and lateral overgrowth of selective Ge epitaxy on SiO2-patterned Si(001) substrates. Journal of Vacuum Science & Technology B. 26 (1), 117-121 (2008).

- Bai, J., et al. Study of the defect elimination mechanisms in aspect ratio t.rapping Ge growth. Applied Physics Letters. 90 (10), 101902 (2007).

- Montalenti, F., et al. Dislocation-Free SiGe/Si Heterostructures. Crystals. 8 (6), 257 (2018).

- Zhang, H. L. Calculation of shuffle 60° dislocation width and Peierls barrier and stress for semiconductors silicon and germanium. European Physical Journal B. 81 (2), 179-183 (2011).

- Kim, M., Olubuyide, O. O., Yoon, J. U., Hoyt, J. L. Selective Epitaxial Growth of Ge-on-Si for Photodiode Applications. ECS Transactions. 16 (10), 837-847 (2008).

- Yako, M., Kawai, N. J., Mizuno, Y., Wada, K. The kinetics of Ge lateral overgrowth on SiO2. Proceedings of MRS Fall Meeting. , (2015).

- Kamino, T., Yaguchi, T., Hashimoto, T., Ohnishi, T., Umemura, K. A FIB Micro-Sampling Technique and a Site Specific TEM Specimen Preparation Method. Introduction to Focused Ion Beams. , (2005).

- Park, J. S., et al. Low-defect-density Ge epitaxy on Si(001) using aspect ratio trapping and epitaxial lateral overgrowth. Electrochemical and Solid-State Letters. 12 (4), H142-H144 (2009).

- Li, Q., Jiang, Y. B., Xu, H., Hersee, S., Han, S. M. Heteroepitaxy of high-quality Ge on Si by nanoscale Ge seeds grown through a thin layer of SiO2. Applied Physics Letters. 85 (11), 1928-1930 (2004).

- Halbwax, M., et al. Epitaxial growth of Ge on a thin SiO2 layer by ultrahigh vacuum chemical vapor deposition. Journal of Crystal Growth. 308 (1), 26-29 (2007).

- Leonhardt, D., Ghosh, S., Han, S. M. Origin and removal of stacking faults in Ge islands nucleated on Si within nanoscale openings in SiO2. Journal of Applied Physics. 10 (7), 073516 (2011).

- Takada, Y., Osaka, J., Ishikawa, Y., Wada, K. Effect of Mesa Shape on Threading Dislocation Density in Ge Epitaxial Layers on Si after Post-Growth Annealing. Japanese Journal of Applied Physics. 49 (4S), 04DG23 (2010).

- Ishikawa, Y., Wada, K. Germanium for silicon photonics. Thin Solid Films. 518 (6), S83-S87 (2010).

- Nagatomo, S., Ishikawa, Y., Hoshino, S. Near-infrared laser annealing of Ge layers epitaxially grown on Si for high-performance photonic devices. Journal of Vacuum Science & Technology B. 35 (5), 051206 (2017).

- Ayers, J. E., Schowalter, L. J., Ghandhi, S. K. Post-growth thermal annealing of GaAs on Si(001) grown by organometallic vapor phase epitaxy. Journal of Crystal Growth. 125 (1), 329-335 (1992).

- Wang, G., et al. A model of threading dislocation density in strain-relaxed Ge and GaAs epitaxial films on Si (100). Applied Physics Letters. 94 (10), 102115 (2009).

- Leonhardt, D., Ghosh, S., Han, S. M. Defects in Ge epitaxy in trench patterned SiO2 on Si and Ge substrates. Journal of Crystal Growth. 335 (1), 62-65 (2011).

- Sammak, A., Boer, W. B., Nanver, L. K. Ge-on-Si: Single-crystal selective epitaxial growth in a CVD reactor. ECS Transactions. 50 (9), 507-512 (2012).

- Ishikawa, Y., Wada, K., Cannon, D. D., Liu, J., Luan, H. C., Kimerling, L. C. Strain-induced band gap shrinkage in Ge grown on Si substrate. Applied Physics Letters. 82 (13), 2044-2046 (2003).

- Bolkhovityanov, Y. B., Gutakovskii, A. K., Deryabin, A. S., Sokolov, L. V. Edge Misfit Dislocations in GexSi1–x/Si(001) (x~1) Heterostructures: Role of Buffer GeySi1–y (y < x) Interlayer in Their Formation. Physics of the Solid State. 53 (9), 1791-1797 (2011).

- Bourret, A. How to control the self-organization of nanoparticles by bonded thin layers. Surface Science. 432 (1), 37-53 (1999).

- Hirth, J. P., Lothe, J. Grain boundaries. Theory of Dislocations, 2nd ed. 19, 697-750 (1982).

- Mizuno, Y., Yako, M., Luan, N. M., Wada, K. Strain tuning of Ge bandgap by selective epigrowth for electro-absorption modulators. Proceedings of SPIE Photonics West, San Francisco, CA, USA. 9367, 1-6 (2015).

- Nam, J. H., et al. Lateral overgrowth of germanium for monolithic integration of germanium-on-insulator on silicon. Journal of Crystal Growth. 416 (15), 21-27 (2015).

- Fitch, J. T. Selectivity Mechanisms in Low Pressure Selective Epitaxial Silicon Growth. Journal of The Electrochemical Society. 141 (4), 1046-1055 (1994).

- Ye, H., Yu, J. Germanium epitaxy on silicon. Science and Technology of Advanced Materials. 15 (2), 1-9 (2014).

Reimpressões e Permissões

Solicitar permissão para reutilizar o texto ou figuras deste artigo JoVE

Solicitar PermissãoThis article has been published

Video Coming Soon

Copyright © 2025 MyJoVE Corporation. Todos os direitos reservados